#### RICE UNIVERSITY

## OKL: A Unified Language for Parallel Architectures

by

#### David Medina

A THESIS SUBMITTED

IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE

#### **Doctor of Philosophy**

APPROVED, THESIS COMMITTEE:

Timothy Warburton, Chair Professor of Computational and Applied Mathematics

Beatrice Riviere Professor of Computational and Applied Mathematics

Danny C. Sorensen Noah Harding Professor of Computational and Applied Mathematics

Keith D. Cooper L. John and Ann H. Doerr Professor of Computational Engineering

Houston, Texas

May, 2015

#### **Abstract**

#### OKL: A Unified Language for Parallel Architectures

#### David Medina

Rapid evolution of computer processor architectures has spawned multiple programming languages and standards. This thesis strives to address the challenges caused by fast and cyclical changes in programming models. The novel contribution of this thesis is the introduction of an abstract unified framework which addresses portability and performance for programming manycore devices. To test this concept, I developed a specific implementation of this framework called OCCA. OCCA provides evidence that it is possible to achieve high performance across multiple platforms.

The programming model investigated in this thesis abstracts a hierarchical representation of modern manycore devices. The model at its lowest level adopts native programming languages for these manycore devices, including serial code, OpenMP, OpenCL, NVIDIA's CUDA, and Intel's COI. At its highest level, the ultimate goal is a high level language that is agnostic about the underlying architecture. I developed a multiply layered approach to bridge the gap between expert "close to the metal" low-level programming and novice-level programming. Each layer requires varying degrees of programmer intervention to access low-level features in device architectures.

I begin by introducing an approach for encapsulating programming language features, delivering a single intermediate representation (OCCA IR). Built above the OCCA

iii Abstract

IR are two kernel languages extending the prominent programming languages C and Fortran, the OCCA kernel language (OKL) and the OCCA Fortran language (OFL). Additionally, I contribute two automated approaches for facilitating data movement and automating translations from serial code to OKL kernels.

To validate OCCA as a unified framework implementation, I compare performance results across a variety of applications and benchmarks. A spectrum of applications have been ported to utilize OCCA, showing no performance loss compared to their native programming language counterparts. In addition, a majority of the discussed applications show comparable results with a single OCCA kernel.

I'm grateful to my advisor Professor Tim Warburton for his guidance and providing me a great working environment during my time at Rice University. With his supervision, teachings, and collaboration, I was able to gain the valuable knowledge and experience required for this thesis work. Through him, I've had the opportunity to meet many colleagues from our research group and collaborators in academia, national labs, and industry. Likewise, I'm thankful for the faculty at CAAM for teaching the fundamentals required for my work. I would like to thank my committee, Prof. Riviere, Prof. Symes, Prof. Sorensen, and Prof. Cooper, for their advice, feedback, and support. I also want to mention my great thanks to Dr. Amik St-Cyr for his mentoring and suggestions through my internships.

This would also not have been made possible without important people outside my academic life. In particular, I would like to thank my wife Xiong for her constant help, understanding, and coffee. Many colleagues are also very good friends outside of school, helping me out when I need it. I'm lucky to have good friends, notably Rajesh Gandham for being my awesome officemate and collaborator through many projects and Jesse Chan for his constant help.

## Table of Contents

| A            | bstra  | ct                                                    | ii           |

|--------------|--------|-------------------------------------------------------|--------------|

| $\mathbf{A}$ | cknov  | vledgements                                           | iv           |

| Ta           | able ( | of Contents                                           | $\mathbf{v}$ |

| N            | omer   | clature                                               | x            |

|              | 1      | Abbreviations                                         | X            |

|              | 2      | Languages and Standards                               | X            |

|              | 3      | GPU Terminology                                       | xi           |

|              | 4      | OCCA Terminology                                      | xii          |

| 1            | Intr   | oduction                                              | 1            |

|              | 1.1    | Overview of Computational Architectures               | 1            |

|              |        | 1.1.1 Central Processing Units                        | 2            |

|              |        | 1.1.2 Graphics Processing Units                       | 3            |

|              | 1.2    | Programming Next-Generation Architectures             | 4            |

|              |        | 1.2.1 Programming with CUDA and OpenCL                | 4            |

|              |        | 1.2.2 Performance Differences Between CUDA and OpenCL | 6            |

|              | 1.3    | Literature Review                                     | 7            |

|              |        | 1.3.1 Directive Approach                              | 7            |

|        |     |                  | $\sim$ |        |   |

|--------|-----|------------------|--------|--------|---|

| ' I 'A | BLE | $^{\mathrm{OF}}$ | CON    | ITENTS | 1 |

| T 7 | ٠ |

|-----|---|

|     |   |

|     |   |

|   |     | 1.3.2  | Source-to-source Approach                     | 10 |

|---|-----|--------|-----------------------------------------------|----|

|   |     | 1.3.3  | Wrapper Approach                              | 11 |

|   | 1.4 | Public | eations                                       | 13 |

|   |     | 1.4.1  | Published Journal Articles                    | 13 |

|   |     | 1.4.2  | Journal Articles in Progress                  | 13 |

|   |     | 1.4.3  | Conferences and Seminar Invitations           | 14 |

|   |     | 1.4.4  | Poster Presentations                          | 15 |

|   | 1.5 | Outlin | ıe                                            | 15 |

| 2 | OC  | CA: U  | nified Approach To Multithreading Languages   | 18 |

|   | 2.1 | OCC    | A Background                                  | 19 |

|   |     | 2.1.1  | CPU Architecture                              | 20 |

|   |     | 2.1.2  | GPU Architecture                              | 22 |

|   |     | 2.1.3  | CPU and GPU Similarities                      | 24 |

|   | 2.2 | OCC    | A Intermediate Representation (IR)            | 25 |

|   |     | 2.2.1  | Derivation                                    | 26 |

|   |     | 2.2.2  | Programming Model                             | 27 |

|   |     |        | 2.2.2.1 Kernel Arguments                      | 32 |

|   |     |        | 2.2.2.2 Outside occaOuterFor                  | 34 |

|   |     |        | 2.2.2.3 Between occaOuterFors                 | 34 |

|   |     |        | 2.2.2.4 Between occaOuterFor and occaInnerFor | 34 |

|   |     |        | 2.2.2.5 Between occaInnerFors                 | 35 |

|   |     |        | 2.2.2.6 Inside occaInnerFors                  | 35 |

|   |     | 2.2.3  | Device Memory Hierarchy                       | 35 |

|   | 2.3 | Applie | eation Programming Interface                  | 37 |

|   |     | 2.3.1  | Offload Model and Device Abstractions         | 37 |

|   |     |        | 2.3.1.1 occa::device Class          | 38 |

|---|-----|--------|-------------------------------------|----|

|   |     |        | 2.3.1.2 occa::memory Class          | 39 |

|   |     |        | 2.3.1.3 occa::kernel Class          | 40 |

|   |     | 2.3.2  | Kernel Compilation                  | 41 |

|   |     | 2.3.3  | High Performance Computing Features | 45 |

|   | 2.4 | Conclu | uding Remarks                       | 46 |

| 3 | OK  | L and  | OFL: OCCA Kernel Languages          | 48 |

|   | 3.1 | Comp   | iler Tools                          | 49 |

|   |     | 3.1.1  | Preprocessor                        | 50 |

|   |     | 3.1.2  | Parsing and Tokenization            | 50 |

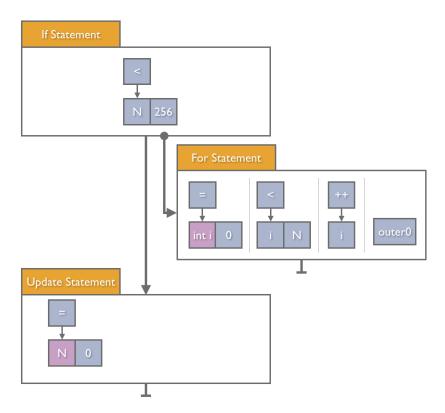

|   |     | 3.1.3  | Statement Labeling                  | 51 |

|   |     | 3.1.4  | Expression Trees                    | 53 |

|   |     | 3.1.5  | Types and Variable Information      | 55 |

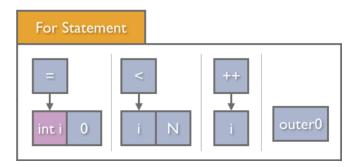

|   | 3.2 | OKL    | Specification and Features          | 56 |

|   |     | 3.2.1  | Exposing Parallelism                | 56 |

|   |     | 3.2.2  | Memory Types                        | 61 |

|   |     | 3.2.3  | Device Functions                    | 63 |

|   | 3.3 | OFL    | Specification                       | 65 |

|   |     | 3.3.1  | Exposing Parallelism                | 65 |

|   |     | 3.3.2  | Memory Types                        | 67 |

|   | 3.4 | Suppo  | ort for CUDA and OpenCL             | 68 |

|   | 3.5 | Concl  | uding Remarks                       | 71 |

| 4 | Aut | omate  | ed Data Movement                    | 73 |

| $\frac{T}{}$ | ABLE                           | OF CONTENTS                                             |     |  |  |

|--------------|--------------------------------|---------------------------------------------------------|-----|--|--|

|              | 4.1                            | Automated Data Movement Approaches                      | 73  |  |  |

|              | 4.2                            | Emulating Unified Memory                                | 75  |  |  |

|              | 4.3                            | Optimizations                                           | 77  |  |  |

|              | 4.4                            | Concluding Remarks                                      | 79  |  |  |

| 5            | OA                             | K: OCCA Automagic Kernel                                | 80  |  |  |

| 5            | 5.1                            | Coding Patterns in Numerical Applications               |     |  |  |

|              |                                | 5.1.1 Finite Difference                                 | 81  |  |  |

|              |                                | 5.1.2 Finite Element and Discontinuous Galerkin Methods | 86  |  |  |

|              | 5.2                            | Automagic Analysis                                      | 92  |  |  |

|              |                                | 5.2.1 Value Extractions                                 | 93  |  |  |

|              |                                | 5.2.2 Detection of Loop Carried Dependencies            | 95  |  |  |

|              |                                | 5.2.3 Additional Language Constructs                    | 98  |  |  |

|              | 5.3 Auto-generation of Kernels |                                                         |     |  |  |

|              | 5.4                            | Concluding Remarks                                      | 105 |  |  |

| 6            | Imp                            | plementation Studies and Benchmarks                     | 107 |  |  |

|              | 6.1                            | Finite Difference Method                                | 107 |  |  |

|              | 6.2                            | Monte Carlo                                             | 111 |  |  |

|              | 6.3                            | Finite Element Method                                   | 113 |  |  |

|              | 6.4                            | Discontinuous Galerkin                                  | 117 |  |  |

|              | 6.5                            | Rodinia Benchmarks                                      | 118 |  |  |

|              |                                | 6.5.1 Back Propagation                                  | 119 |  |  |

|              |                                | 6.5.2 Breadth-First Search                              | 120 |  |  |

| ix | Nomenclature |

|----|--------------|

|    |              |

|    |            | 6.5.3 Gaussian Elimination   | 121 |

|----|------------|------------------------------|-----|

|    | 6.6        | Concluding Remarks           | 122 |

| 7  | Con        | aclusions and Future Work    | 124 |

|    | 7.1        | Conclusions                  | 124 |

|    | 7.2        | Future Work                  | 125 |

| A  | App        | pendix: OCCA Kernel Keywords | 127 |

| Re | References |                              |     |

## Nomenclature

## 1 Abbreviations

CPU Central Processing Unit

FPGA Field Programmable Gate Arrays

FPU Floating-Point Unit

GPU Graphics Processing Unit

HPC High Performance Computing

IR Intermediate Representation

NUMA Non-Uniform Memory Access

RAM Random Access Memory

SIMD Single-Instruction Multiple-Data

## 2 Languages and Standards

Heterogeneous Combined use of CPUs and accelerators for computational

Computing purposes

OpenMP Open standard for programming multithreaded systems

through directives.

xi Nomenclature

OpenMP 4.0 Open standard for programming heterogeneous systems

through directives.

OpenACC Open standard for programming GPUs through directives.

OpenCL Open standard for programming heterogeneous systems by

unifying parallel device architectures such as CPUs, GPUs,

and FPGAs.

CUDA NVIDIA's proprietary language for programming NVIDIA

GPUs

COI Intel's Coprocessor Offload Infrastructure used to program the

Xeon Phi

OKL OCCA Kernel Language (C-based)

OFL OCCA Fortran Language (Fortran-based)

## 3 GPU Terminology

GPGPU General Purpose Graphics Processing Unit, GPUs

used for general purpose computing

Host Processor(s) running an application, usually by a

CPU

Device Hardware targeted for offload computations to

such as a multicore CPU, GPU, or other accel-

erator

Kernel GPU Function

Nomenclature

(CUDA) Thread Manages work in the GPU at the finest granularity

level

(CUDA) Block Group of CUDA threads executing concurrently

(OpenCL) Work-item Manages work in the GPU at the finest granularity

level. Synonymous with threads in CUDA

(OpenCL) Work-group Group of OpenCL work-items executing concur-

rently. Synonymous with blocks in CUDA

Global memory Memory located on the device with the longest la-

tency in the device memory hierarchy

Shared memory Memory co-located with the processor's cache, ac-

cessible by all FPUs on a compute unit

Register memory Processing unit's register file, smallest latency in

the device memory hierarchy

## 4 OCCA Terminology

Mode Target language/specification for a device such as

Serial, OpenMP, OpenCL, and CUDA

Loop Tag Fourth clause in a for-loop indicating the type of

parallelism to be taken by the for-loop

Outer Loops For-loops with an outer tag, parallelized by

threads (CPU) or work-groups (GPU)

Inner Loops For-loops with an inner tag, able to be vectorized

(CPU) or work concurrently (GPU)

xiii Nomenclature

Shared memory Shared memory when using a GPU architecture,

otherwise a regular buffer

Exclusive memory Register memory unique to a inner-loop iteration,

value can jump inner-loop scopes

Introduction

With the collapse of single-processor computing in the high performance computing (HPC) field, a wave of parallel-computing has emerged. Alongside the paradigm shift of multiprocessor computing, several hardware architectures tailored for parallel computing have risen and fallen. Keeping confidence in numerical methods and their implementations while engaging in this undetermined and changing environment became a motivation for the work provided in this thesis.

The novelty presented in this thesis is the programming model used to abstract modern manycore devices. Multiple layers in this model were developed, including the representation of low-level features present in manycore architectures towards a high-level model automating. These concepts were implemented throughout the OCCA project to unify commonalities found across prominent architectures in the HPC community. We start with an introduction on the past, present and projected future architectures and their programming models to set the background for the thesis work. Although the work shown in this thesis generalizes current many-core models, knowledge in architecture advancements provides insight on identifying recurring features across generations of hardware designs.

## 1.1 Overview of Computational Architectures

We begin by discussing the general-purpose central processing unit (CPU) and its architectural improvements through the last few decades. Following is an overview on graphics processing units (GPU) and strides to the general-purpose programming model we see today in CUDA and OpenCL.

#### 1.1.1 Central Processing Units

Floating point units (FPUs) began as co-processors, replacements for software-designed floating-point operations. Central processing units would offload floating-precision work to external FPUs until the FPUs became integrated with the processor. Transistors per area grew exponentially (modeled by Moore's Law), increasing peak FLOPS exponentially (Schaller 1997). Once power limitations became apparent, voltage and currents were scaled proportionally to transistor sizes (Dennard scaling) to control power utilization and maintain the transistor density rate noted by Moore's Law (Dennard et al. 1974). Although Dennard scaling made the use of the transistor count feasible, performance scaling was reduced around the year 2000, requiring architectural improvements to continue scaling (Dally 2009).

The use of Beowulf clusters (computers networked together) gained traction as a method to sidestep the limitations set by a single processing unit. A similar philosophy was then applied to central processing units, resulting in multicore processor designs with each core containing an independent instruction scheduler. Processors with 2-8 cores and motherboards containing 2-4 processor sockets became the industry standard. Together with increasing core-count, single-instruction multiple-data (SIMD) cores became common on general-purpose and performance-based processing units. This idea of reusing an instruction on multiple data entries is not new and has been implemented since the CRAY-1 in 1976 (Russell 1978). Current SIMD vectorization units not only allow for instruction reuse but decrease overall fetching latency due to vector instructions operating on a contiguous data segment, usually requiring page alignment of memory accesses.

While many aspects contributed to gains in computation performance, bandwidth and latency has improved at different rates. The processor clock speeds increased at a rate to which memory systems were incapable of continuously providing data for, hence a computational bottleneck stemming from the memory bandwidth. Apart from pure bandwidth increases, a hierarchy of cache levels were introduced to predict and prefetch data directly for processing elements to avoid excessive data movement. Transfers between memory and cache are automated to fetch fixed-sized memory segment cache lines into cache following a non-cached memory access (cache miss). Likewise, cache line evictions are also automated while maintaining coherence across cores.

Alongside with CPU architecture improvements, co-processors tailored for specific computational tasks were also developed. Graphics-processing and embarrassingly-parallel computations are currently common uses for co-processors while the central processor is used for general-purpose computations. Well known co-processors include graphics processing units (GPUs), field programmable gate arrays (FPGAs), Intel's Xeon Phi, and IBM's Cell architecture. However, there are also architectures aiming for performance with low-power consumption, such as massively parallel processor arrays (MPPAs).

#### 1.1.2 Graphics Processing Units

Graphics cards were developed due to the increasing demand for improved graphics in video games. The architectural design for graphics cards was based on the linear algebra operations used in 3D rendering. Rather than relying on the general-purpose CPU, computations for rendering were offloaded onto graphics cards. Briefly stated, programming practices for graphics rendering queue batches of identical instructions which make use of an embarrassingly parallel architecture.

Programming graphics cards made use of a fixed pipeline, splitting work into

different stages for updating vertices and managing individual fragments. With the potential of using graphics cards for general purpose computing, the Brook language was developed to reduce the complexity of using the fixed pipeline for general purpose computations (Buck et al. 2004). In 2007, Brook inspired CUDA, NVIDIA's proprietary language, for using their graphics cards as general purpose GPUs (GPGPUs). However, CUDA vendor-locks application development to NVIDIA GPUs for hardware acceleration (Bodin and Bihan 2009).

To address this issue, the Khronos group, an open standards consortium, released specifications for the OpenCL standard for programming heterogeneous platforms including: CPUs, GPUs, Intel's Xeon Phi and field-programmable gate arrays (FPGAs). In 2008, a year after CUDA's initial release, NVIDIA and Advanced Micro Devices (AMD) presented their first functional OpenCL demo in Siggraph Asia 2008 (Munshi 2008). Presently, programming for these accelerators requires either CUDA or OpenCL, or approaches which make use of these languages.

## 1.2 Programming Next-Generation Architectures

With the rise of accelerator models, it is not known which architectures will endure. For example, the IBM's Cell architecture, that powered the Playstation 3 and in the first petaflop-capable machine, was put on hiatus less than a decade after development (Campbell 2009). The uncertainty in lasting architectures could cause applications to become defunct in the future. This systemic risk for software development presents a challenge for code longevity. I will briefly discuss programming differences between CUDA and OpenCL together with their respective advantages and disadvantages.

#### 1.2.1 Programming with CUDA and OpenCL

The similarities between CUDA and OpenCL become evident in their programming model but their popularity in use differ. NVIDIA releases their own compiler wrapper, nvcc, to allow CUDA kernels to be embedded in the application code, while OpenCL separates host code (application code) with the device code (kernels), which steepens the learning curve. The simplicity of combining host and device code is one of the reasons CUDA is somewhat more popular than OpenCL which separates device kernels (functions written for the GPU) from application code. Despite this, OpenCL is favorable largely due to its open standard which has been implemented for a large range of architectures. Fortunately, kernels written in CUDA can be translated to OpenCL without much effort as seen in AMD's "Porting into OpenCL" (Advanced Micro Devices 2013) site; however, the same could not be said about the host-device interaction. As seen in code listing 1.1, CUDA allows mixing host and device code; whereas OpenCL requires separate files.

```

// (1) CUDA: Embedded file holding type

// (2) OpenCL: External file holding type

11

definitions and functions

definitions and functions

class vector3 {

struct vector3 {

public:

float x, y, z;

};

float x, y, z;

__host__ __device__ float normalize(){

float normalize(vector3 *v){

const float norm = sqrt((x*x) +

const float x2 = (v \rightarrow x)*(v \rightarrow x);

const float y2 = (v->y)*(v->y);

(y*y) +

(z*z));

const float z2 = (v->z)*(v->z);

x /= norm;

const float norm = sqrt(x2 + y2 + z2);

y /= norm;

z /= norm;

v \rightarrow x /= norm;

v->y /= norm;

};

v->z /= norm;

__global__

void normalizeArray(vector3 *array,

void normalizeArray(vector3 *array,

const int entries){

const int entries){

const int n = threadIdx.x +

const int n = get_global_id(0);

(blockIdx.x * blockDim.x)

if(n < entries)</pre>

if(n < entries)

array[n].normalize();

normalize( &(array[n]) );

}

}

```

Listing 1.1: Examples of object-oriented programming in (1) CUDA and (2) OpenCL

#### 1.2.2 Performance Differences Between CUDA and OpenCL

There are striking differences between NVIDIA's proprietary language and runtime API compared with OpenCL's low-level API (with flexibility on platform-choice). Hence, approaches have been taken to combine advantages from each language. The benefits for developing multithreaded GPGPU applications in CUDA inspired the question whether a translation between CUDA and OpenCL would be possible and useful. Various papers have benchmarked well-known suites on both CUDA and OpenCL, summarizing that comparable performance can be achieved in both, but depend on the hardware and optimizations (Karimi et al. 2010, Fang et al. 2011, Du et al. 2012, Wang et al. 2014). For example, fluctuations in performance can be seen across NVIDIA's

CUDA, NVIDIA's OpenCL and AMD's OpenCL platforms running the same kernel, with one-to-one translations, due to varying optimizations found on the different platforms. A similar occurrence is found when comparing with performance across compilers on the same application code.

Different approaches have been taken to address portability and performance when uniting these two frameworks. Some approaches try to minimize adjustments to legacy codes to prevent refactoring on the host-device model by using directives, inspiring standards such as OpenMP and OpenACC (Dolbeau et al. 2007). Other approaches accept the host-device programming model and strive to combine CUDA's language features with OpenCL's flexibility, motivating source-to-source solutions. Lastly, we discuss libraries which hide the underlying languages by providing specialized routines, such as BLAS (Basic Linear Algebra Subprograms).

## 1.3 Literature Review

The next chapter describes in detail the initial development of OCCA (Medina 2014), including the OCCA IR kernel language. This section provides a spectrum of approaches for achieving similar code portability throughout a range of hardware. Analyzing these present and past approaches motive the choices taken in the development of the OCCA IR. These approaches are grouped into three categories: the use of directives which allow the compiler to provide code transformations; source-to-source transformations between programming languages; and lastly, providing a set of tailored operations, hand-coded for each provided backend.

#### 1.3.1 Directive Approach

The first approach we will discuss makes use of directives in the form of #pragma's or comment regions to shift code manipulation to the compiler. OpenMP is a promi-

nent example of a specification which uses directives. Rather than using a low-level management of threads, OpenMP eases multithreading development by automating thread management.

With the introduction of GPUs used in high performance computing (HPC), it was of interest to achieve the simplification seen in multithreading for these new accelerators. In 2009, hiCuda was one of the first directive-based project to address this issue, handling device tasks such as memory management and kernel generation (Han and Abdelrahman 2009, Han and Abdelrahman 2011). In the same year, a Star Superscalar (StarSs) programming model extension was proposed, anticipating an extension of OpenMP to introduce multithreaded programming on GPGPUs (Ayguadé et al. 2009). These projects were followed by a large number of standards and standard proposals, resulting in OpenACC and OpenMP 4.0. OpenACC was the first commercial release, supported at the time by compilers from Cray, NVIDIA, CAPS and PGI. Open-source projects such as openMPC (Lee and Eigenmann 2010) and IPMACC (Lashgar et al. 2014) gave open-source alternatives to using OpenACC in application codes. Meanwhile, OpenMP received a few proposals for its 4.0 specification (Ferrer et al. 2011, Duran et al. 2011). There are currently few compilers supporting OpenMP 4.0 due to the specification being relatively new.

While there have been promising results, it should be noted that several benchmarks were embarrassingly parallel and could be described with simple access patterns (Han and Abdelrahman 2009, Wienke et al. 2012, Herdman et al. 2012, Reyes et al. 2012). It was of interest to not only note the performance, but the amount of labor required to enable GPGPU support on traditional CPU applications through directives as opposed to refactorization with OpenCL and/or CUDA (Wienke et al. 2012, Wang et al. 2014). The paper by (Wienke et al. 2012) showed a drop of 90% performance when using an OpenACC implementation of their non-linear optimization algorithm

when using naive placements of #pragmas compared to OpenCL, and a 60%-80% drop when restructuring the parallel loops. Similarly, (Wang et al. 2014) reported a 20%-40% performance drop when comparing on a Fermi GPU, Kepler GPU, and the Xeon Phi for their finite difference implementation. However, the restructuring required for the naive OpenACC implementations in both papers required 1%-2% line changes when compared to their OpenCL and CUDA implementation counterparts. The tailored OpenACC kernels which achieved 40%-60% relative performance, line changes were still less than 45% when comparing with OpenCL and CUDA. The fact that there are missing or immature elements required for GPU optimization cannot be hidden, including:

- Access to manually manipulate shared memory

- Manual memory retainment between the host and device

- Forced global synchronization across certain parallel regions

- Light asynchronous support

- Limited use of functions (required to be inline but not guaranteed to work)

Nevertheless, while some algorithms could be deemed inefficient with this approach, others generate comparable CUDA/OpenCL kernels as to their hand-coded counterparts; an important factor when balancing developer time with performance. There are tools to attempt different optimizations with code transformations; for example, some machine-learning-based methods automatically test for performance improvements, but their use in practice still needs investigation (Grewe et al. 2013, Lee and Vetter 2014).

To summarize, the use of directives puts greater value on the learning curve and development time as opposed to computational performance. Preliminary results have been positive for simple kernel examples, but the specification appears to be lacking

low-level features for leveraging the full targeted architecture. In contrast with the directive approach, the following discussed approach makes use of the advantages in CUDA, for it's simpler programming language, and OpenCL, for it's portability across multiple architectures.

#### 1.3.2 Source-to-source Approach

The second approach discussed is a source-to-source approach, where code transformation occurs prior to compilation or at the compilation stage. Although not as simple as the directive approach, this approach allows users to take advantage of CUDA's language extensions which provide many features to ease GPGPU programming. For example, NVIDIA has released toolkits for several optimized linear algebra routines, such as cuBLAS and MAGMA, which facilitate many dense and sparse linear operations; something difficult to enable with the directive approach.

However, as previously mentioned, using CUDA limits the user to use NVIDIA GPUs for accelerating codes. Two projects addressed this issue by creating source-to-source translators from CUDA to OpenCL to achieve platform flexibility: CU2CL (Martinez et al. 2011, Gardner et al. 2013) and SWAN (Harvey and De Fabritiis 2011). The SWAN project came from industry and apparently stopped updating after the introduction of NVIDIA's Fermi architecture. Meanwhile CU2CL, an academic prototype, currently supports a core portion of later versions of CUDA which have added many useful features.

A second approach to source-to-source conversion is based on analyzing the intermediate assembly produced by CUDA and converting it to assembly supported by other platforms. GPU Ocelot (Diamos et al. 2010, Farooqui et al. 2011) and INSIEME (Jordan et al. 2013) have taken this assembly approach towards platform flexibility. A possible disadvantage arises when porting assembly to non-NVIDIA platforms or even

distinct hardware due to architecture-dependent optimizations applied on distinct architectures.

Aside from pure CUDA-to-OpenCL and assembly transformations, a few other translation projects have been released. Par4All is a project that was developed to automatically detect loops from C and Fortran and transform them at compile-time into OpenMP, OpenCL and CUDA (Amini et al. 2012, Ventroux et al. 2012). Similarly, the project discussed in (Anderson 2014) is a prototype to convert Python code into OpenCL kernels in a more controlled environment. These approaches resemble a blackbox due to automatic conversion, which may be overly intrusive and could create issues interfacing with other libraries.

To summarize, the source-to-source approaches encounters difficulties due to the transformation scope and the rapidly changing specifications. Similar to requirements of directive-based approaches, which require access to the complete project source code, source-to-source projects could require a full application transformation which may be impractical in industrial codes. The last approach tries to prevent the global-scope requirement and is robust to changes in specifications. By creating a wrapper around CUDA and OpenCL, the next approach creates tailored frameworks which prioritize in easy-to-use routines without sacrificing high performance.

### 1.3.3 Wrapper Approach

The "wrapper approach" focuses on creating libraries and objects wrappers. By developing and implementing tailored algorithms for supported architectures, high performance can be achieved while maintaining platform flexibility. While CUDA has several exclusive mathematical libraries, such as cuBLAS and MTL4, there are also libraries available for OpenCL, such as VexCL/ViennaCL (Demidov 2012, Demidov et al. 2013). AMD has also released the open-source OpenCL counterpart, clBlas, as

well as Bolt, the standard template library (STL) styled library for executing common algorithms on vector structures (Rogers and FELLOW 2013). Other industrial approaches include Intel's Thread Building Blocks (TBB) and Microsoft's specification for C++ AMP, a collection of highly templated libraries for executing parallel tasks (Pheatt 2008, Gregory and Miller 2012).

SkePU is another C++ library which focuses on the map-reduce model for kernel generation (Enmyren and Kessler 2010, Dastgeer et al. 2011). By providing "skeleton" code, users have limited templates with which to create kernels. While SkePU can generate OpenCL and CUDA kernels, the code skeletons offered to generated kernels with require simple access patterns.

The motivation for platform flexibility has increased with the growing number of architectures, and so have the available libraries. Several national labs have investigated possible portable solutions for next generation codes. The Sandia National Laboratory has developed Kokkos, a C++ library which supports Pthreads, OpenMP and CUDA (Edwards and Trott 2013). Kokkos is based on multidimensional arrays which cover device memory and textures for linear algebra routines. Kokkos uses C++ and supports CUDA and thus is able to implement API calls which take in functors as inputs for generating code at compile-time. Likewise, Lawrence Livermore National Laboratory developed RAJA, a C++ library focused on portability for simulation codes (Hornung and Keasler 2013). Similar to Kokkos, RAJA focuses on kernel generation through functors but relies in C++ 11 and lambdas. The Los Alamos National Laboratory has instead focused on improving Thrust which support CUDA, OpenMP and Intel's TBB (Bell and Hoberock 2011). And lastly, the Oak Ridge National Laboratory been working with directive approaches, such as OpenACC.

Relying on libraries to provide optimized subroutines can improve developer time, but can also limit the scope of an application and cause excess data movement. These tailored libraries, although allowing for minimal kernel generation, do not expose enough flexibility for customizing complex kernels. Because our goal is to present a portable solution for developing in heterogeneous environments, releasing a set number of specialized routines is not sufficient. However, we acknowledge and adopt salient features such as the simplification in between host and device interaction seen in libraries like Thrust, Kokkos and RAJA.

## 1.4 Publications

During the thesis work, I had the opportunity to collaborate with various colleagues from Rice University, industry, and national laboratories. I would like to include the co-authored publications that have been accepted in peer-reviewed journals, in submission, or in progress, together with a list of talk invitations and poster presentations.

#### 1.4.1 Published Journal Articles

- Gandham, R., Medina, D. and Warburton, T. 2014, GPU Accelerated discontinuous Galerkin methods for shallow water equations, *Communications in Computational Physics*. This paper discusses a high-order discontinuous Galerkin method for the shallow water equations, implementing algorithms implemented used OCCA.

- Medina, D. S., St-Cyr, A. and Warburton, T. 2015, High-Order Finite-differences on multi-threaded architectures using OCCA, in 'ICOSAHOM 2015', Springer. We discuss a high-order finite difference implementation for a seismic imaging. An efficient algorithm implemented in OCCA is described for the wave equation using a vertical transverse isotropy model.

#### 1.4.2 Journal Articles in Progress

- Medina, D. S., St-Cyr, A. and Warburton, T. 2014, OCCA: A unified approach to multi-threading languages, arXiv preprint arXiv:1403.0968. The original paper describing OCCA, it's programming model and the macro-based OCCA IR (intermediate representation) discussed in chapter 2.

- Rahaman, R., Medina, D., Lund, A., Tramm, J., Warburton, T. and Seigel, A. 2015, Portability and Performance of Nuclear Reactor Simulations on Many-Core Architectures, in '77th EAGE Conference and Exhibition 2015'. This article came from a collaboration with a group at the Center for the Exascale Simulation of Advanced Reactors (CESAR) at the Argonne National Laboratory. We compare a neutronics Monte Carlo algorithm on various architectures and programming approaches, such as OCCA and OpenACC.

- Fahrenholtz, S. J., Moon, T., Franco, M., Medina, D., Danish, S., Gowda, A., Shetty, A., Maier, F., Hazle, J., Stafford, R. J., Warburton, T. and Fuentes, D. n.d., A model evaluation study for treatment planning of laser induced thermal therapy. This article discusses the use of a spectral element method for simulating heat transfer from a laser induced thermal therapy. The efficient implementation uses occa to utilize modern architectures.

#### 1.4.3 Conferences and Seminar Invitations

- OKL: A unified kernel language for parallel architectures, Sandia National Laboratory, May 2015

- OKL: A unified kernel language for parallel architectures, SIAM CSE '15, March

2015

- OKL: A unified kernel language for parallel architectures, Rice Oil & Gas '15,

March 2015

- OKL: A unified kernel language for parallel architectures, Chevron, February 2015

- Tutorial on OCCA, CESAR Sound-off meeting at Argonne National Lab, December 2014

- OCCA: A unified approach to multi-threading languages, Computation-Institute for Scientific Computing Research at Lawrence Livermore National Lab, September 2014

- OCCA: A unified approach to multi-threading languages, ICOSAHOM 2014,

June 2014

- High-order Numerical Methods for High-Contrast Seismic Imaging, Rice Oil & Gas '13, February 2013

#### 1.4.4 Poster Presentations

- OKL: A unified kernel language for parallel architectures, SIAM CSE '15, March 2015

- OCCA: A unified approach to multi-threading languages, Rice Oil & Gas '14,

March 2014

#### 1.5 Outline

The goals for this thesis include a portable solution for current and future architectures, an ease for the development of parallel codes, and the ability to expose as much parallelism as possible for achieving optimal performance; in other words, uniting the advantages from the approaches previously mentioned. A portable solution is developed using the OCCA intermediate representation discussed in chapter 2, a macro-based approach using the preprocessor for source-to-source transformation. Facilitating the development for heterogeneous platforms is addressed by introducing OKL and OFL, minor extensions to C and Fortran (discussed in chapter 3) which replaces #pragma's with more familiar loop structures. Lastly, by requiring users to expose parallelism, the OKL and OFL languages avoid unintentionally removing features seen in multicore and many-core architectures.

The thesis content is split into the different components that make up the OCCA project. Chapter 2 details the host API and the OCCA intermediate representation which describes how portability is achieved. Also included in chapter 2 are updates to OCCA since the original papers (Medina 2014, Medina et al. 2014) such as: current and future language support, methods which make OCCA non-intrusive, and HPC-related features. Chapter 3 outlines the tools, specifications and features for the proposed kernel languages, the OCCA kernel language (OKL) and the OCCA Fortran language (OFL). The minimal extensions to C and Fortran seen in OKL and OFL respectively, which allows OCCA to embed kernels into the application code in the future, similar to CUDA. With the compiler tools developed and discussed in chapter 3, it is possible to give an option which assimilates the kernel languages without much change to the application host. Chapter 4 and chapter 5 finish the OCCA specifications by describing two additional layers of assistance towards developers. Chapter 4 introduces unified virtual addressing, its focus being on the implemented automatic data movement for obscuring data movement between the host and device. Chapter 5 introduces a method for automatically detecting loop-carried dependencies on serial code, auto-tagging forloops to generate OKL kernel instances, and run them for detecting efficient kernels generated. Chapter 6 details current applications based on OCCA with preliminary results jointly with benchmarks for performance and portability validation. The thesis

concludes with a synopsis of the thesis work and future work in chapter 7.

# OCCA: Unified Approach To Multithreading Languages

The novel contribution detailed in this chapter comes from the abstracted programming model used to encapsulate native programming languages for manycore devices. An implementation of this model resulted in the OCCA intermediate representation (IR) which supports serial code, Pthreads, OpenMP, CUDA, OpenCL, and COI. Constructing the OCCA IR used a generalization of current parallel architectures to unify the different languages and standards for heterogeneous computing. Furthermore, I discuss an abstract offload model demonstrating a runtime compilation design with the ability to pick a target architecture at runtime and utilize native compilers for their respective language standard.

In this chapter, I discuss an abstract programming model for manycore devices. To further motivate the use of a unified programming model, I first demonstrate the architecture similarities between traditional multicore processors and current graphics processing units (GPUs). The similarities in manycore devices motivate features in the proposed unified programming model. An implementation of this concept was developed, producing the OCCA intermediate representation (IR) which generalizes current parallel architectures to unify the different languages and standards for heterogeneous computing, including serial code, Pthreads, OpenMP, CUDA, OpenCL, and COI.

Accompanying the OCCA IR is an abstracted offload model for the supported backends and a unified interface to manage it, where the offload model defines the *host* as the computational processing unit running an application, offloading computations

to the *device*, the targeted hardware used for additional computations. We conclude the chapter by discussing shortcomings in the macro-based language and transition towards the kernel language discussed in chapter 3.

## 2.1 OCCA Background

Prior to the OCCA project, I developed and translated industrial and academic numerical simulation codes between OpenMP, OpenCL, and CUDA. Through this experience, it became apparent that optimizations between parallel languages did not differ much due to the commonality across their programming models as inferred by the approaches mentioned in section 1.3. It was of interest to investigate a method for leveraging the common aspects found in OpenMP, OpenCL, and CUDA. Thus I developed a prototype for OCCA to offer a unified frontend for those languages and standards through an offload model. The offload model retains the programming model seen in OpenCL and CUDA, where the *host* uses the developed frontend to communicate with the *device*. However, because the coding standards for each device still differed, I created the OCCA intermediate representation to also unify the OpenMP, OpenCL and CUDA compute kernels. I discuss current parallel architecture similarities, a motivation for the development of a single kernel language which can maintain performance across distinct platforms.

Chapter 1 gave a brief introduction to the development of current architectures. In this section, I elaborate on CPU and GPU architectures and their programming models. By describing architectural similarities, we motivate the development of the OCCA IR and OCCA application programming interface (API) discussed in the next sections. We start by outlining the traditional CPU architecture, the most common processor currently used in HPC, followed by analogous descriptions for the GPU

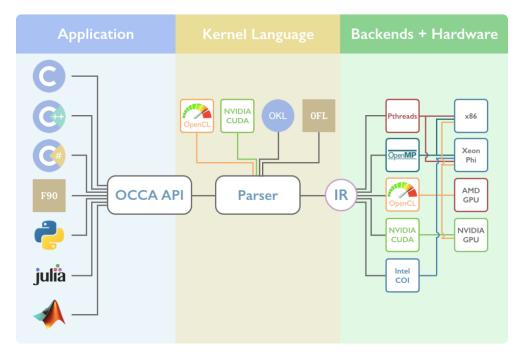

Figure 2.1: Current relationship between supported frontends, the OCCA languages (OKL, OFL, OCCA IR), and supported backends

architecture.

#### 2.1.1 CPU Architecture

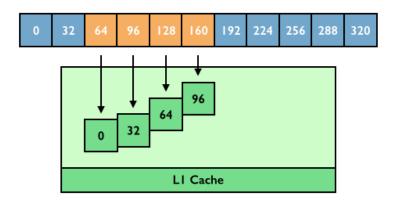

As mentioned in subsection 1.1.1, it has become common for architectures to feature a hierarchy of cache. When data is queried by the processor, a segment of data is moved to cache if not already in cache, as seen in figure 2.2. Common optimization algorithms tailored for modern CPUs try to make use of data locality to maintain needed data in cache, otherwise the segment (cache line) could be evicted.

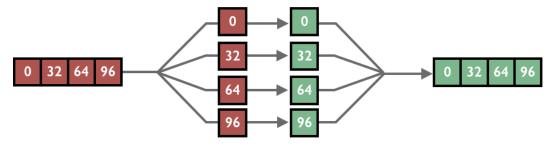

An increase in clock frequency was slowly followed by an increase in data loading capabilities (Wulf and McKee 1995). With the plateau in clock speed, different approaches to increasing computational speed were examined, such as vectorization. Vectorization is a computational complement to local data fetching in caching policies which applies one instruction to consecutive data as seen in figure 2.3

Figure 2.2: When data is accessed from DRAM, neighboring data is sent and stored through the different cache levels.

Figure 2.3: With large registers and vectorization instructions, multiple consecutive data entries can be updated in parallel.

Intel's MMX vectorization instruction set introduced single-instruction multiple-data (SIMD) operations for the x86 architectures, allowing for operations on 64-bit registers to occur concurrently. MMX was followed by the streaming SIMD extension (SSE) instruction set family (SSE, SSE2, SSE3, SSE4) which operated on 128-bit registers. The most current vectorization instruction set by Intel is the advanced vector extensions (AVX) supporting 256-bit registers and 512-bit registers in the case of Intel's Xeon Phi.

Multithreading is the last CPU architecture feature that will be discussed. A large advancement has been made since the first dual-core processor in 2001, to consumer-level processors possessing up to eight cores. Akin to creating a network of computing units (such as those found in Beowulf clusters and current supercomputers) multi-threading integrates multiple independent compute units in a processor. By incorpo-

rating multithreading, it is possible to scale algorithms by the number of cores while still making use of the architecture optimizations mentioned above. This next section will go over major optimizations used in the GPU architecture which are then compared with the architecture features discussed in this section.

#### 2.1.2 GPU Architecture

Graphics processing units were originally developed to manage computations needed in 3D rendering procedures. By using programmable graphics shaders, such as OpenGL's shading language (GLSL) and DirectX's high-level shader language (HLSL), processes were able to offload data and processing to graphics cards. The graphics pipeline can be generalized into three parts: primitive processing, primitive culling, and fragment processing. While the first two steps detect the primitives (such as triangles and quadrilaterals) which will be rendered, the fragment processing step is usually the most computational intensive processes in the graphics pipeline. Each fragment represents the smallest unit in the rendered buffer, analogous to a pixel and it's display, and whose value is calculated through a graphics shader. All fragments run through the same computational shader, an embarrassingly parallel task.

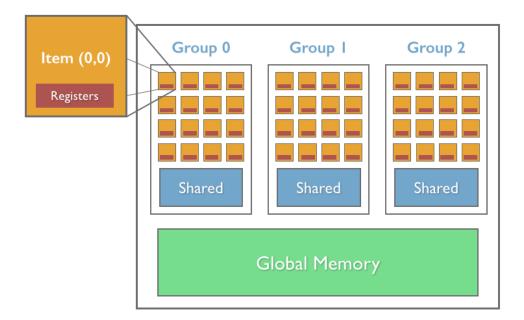

Figure 2.4 shows the GPU architecture layout and memory hierarchy. The compute units in the GPU are denoted by work-items, or threads in CUDA, which are grouped into work-groups, blocks in CUDA, using a SIMD operation approach, relabed as SIMT (single-instruction multiple-threads) by NVIDIA. A synchronization between all work-groups can only occur when a kernel finishes executing since the standard allows for more work-groups than available hardware to execute them; in other words, there is an implicit loop over work-groups that need to be launched for every kernel. In order to expose enough parallelism for GPUs, the user must lay out instructions to be executed as a work-item. Work-items which reside on specific hard-

Figure 2.4: GPU Hierarchy showing work-group and work-item relation as well as the different memory types and their scopes.

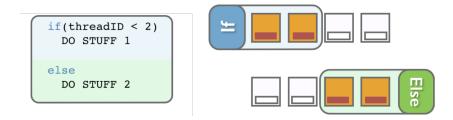

ware groups (as wavefronts in AMD terminology and warps in NVIDIA terminology) are issued the same instruction to execute with the option of calling a NOOP, no operation, instruction when branching occurs. Figure 2.5 shows kernel execution with branching.

Figure 2.5: Work-items on the same hardware groups (half-warp or wavefront) follow the same instruction or call a NOOP (No Operation) instruction.

In the memory hierarchy seen in figure 2.4, each work-item is associated with its own private register set, using the memory layer with the fastest fetching times. Shared memory is the second-fastest memory type found on GPU architectures, which uses the same physical hardware as cache. Apart from latency, shared memory is useful for

synchronizing and communicating data across work-items. Global memory refers to the DRAM found in GPUs, having the longest latency in the GPU memory hierarchy. Data resident in global memory can be fetched from all work-items with support for atomic operations across work-groups.

Aside from GPU shared memory, the existence of registers, cache and DRAM are also seen in CPU architectures. Similarly, the global bandwidth is distributed to the memory managers between the large number of compute units found on modern GPUs; hence, bandwidth is also a common bottleneck in most numerical applications.

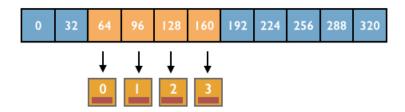

Figure 2.6: Having consecutive work-items load from global memory consecutive data, otherwise known as coalescing reads, allows full use of the bus which vectorizes loads.

If we compare memory access speeds on an NVIDIA K40, NVIDIA's newest single-processor workstation card at this time, the bandwidth for global memory accesses is 288 GB/s while shared memory bandwidth is around 1.2 - 1.8 TB/s using NVIDIA's profiler. The large gap in bandwidth often forces optimizations and best-practices to avoid global memory fetches. The cost of global memory fetches can be reduced through consecutive work-items loading consecutive data (coalesced reads) by making use of the GPU's large bus (384 and 512 bits on current NVIDIA and AMD cards respectively), as seen in figure 2.6. Likewise, shared and register data can be used as intermediate storage for computations.

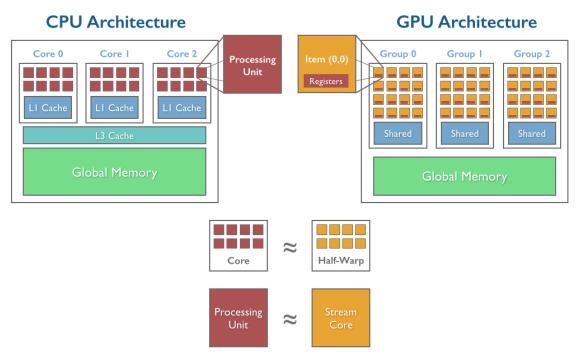

### 2.1.3 CPU and GPU Similarities

By looking at the optimizations discussed for both CPU and GPU architectures, we identify shared features in their programming practices. The key features include: memory accesses, vectorization and efficient multithreading.

Efficient GPU memory accesses make use of the large bus width by using consecutive strides in memory. In comparison, the CPU would make use of resident cache lines by also loading consecutive strides in cached memory. As for vectorization, hardware mapped to consecutive work-items, such as a half-warp or wavefront, could be thought of entities in a vector unit. Being forced to apply the same instruction or call a NOOP is analogous to a CPU's vector instruction operating on a large register. Lastly, the GPU programming model makes an assumption that there is no interdependence between work-groups. If we make the same assumption on a CPU multithreaded program that work is split in the work-group/work-item paradigm, each thread would become independent aside from atomic operations. Forks and joins are no longer present through the assumption that threads operate on independent work-groups.

Similarities in optimization procedures between the CPU and GPU create the foundation on which occa is developed. Making use of the work-group/work-item model while exposing shared memory unifies most optimizations found in the CPU and GPU architectures. Unfortunately, as is discussed in chapter 6, performance is not always portable between architectures. However, language has enough flexibility to include architecture-specific kernel optimizations to achieve near-optimal performance.

# 2.2 OCCA Intermediate Representation (IR)

This section discusses the approach taken to integrate different heterogeneous parallel programming languages and standards. While the focus for the unified programming model arose from the CPU and GPU, as described in section 2.1, the OCCA

IR targets a variety of devices. Given the support for the initial backends (OpenMP, CUDA, and OpenCL), occa is usable on traditional CPUs, GPUs, Intel's Xeon Phi, and FPGAs. However, the number of available backends was extended during the thesis work to include Pthreads, COI, and a prototype for HSA (Heterogeneous System Architecture).

We start by motivating the derivation of the occa IR by comparing with prior approaches, identifying features used (or improved upon) together with disadvantages which were overcome. Next, we describe the programming model specification for the occa IR kernel specification. Additionally, we describe the device memory hierarchies found in the occa IR and their use in HPC applications.

## 2.2.1 Derivation

Key features found in GPU architectures, and later in the Intel's Knights Landing containing large on-chip memory storage, must be made accessible for the high performance focus of the project. Our programming model must be flexible in order to incorporate future architectures and language standards. Recalling section 1.3, portability approaches across multiple backends were categorized into directive, source-to-source, and wrapper approaches. Here we give short summaries of their advantages, which we adopt into the OCCA IR, as well as their disadvantages which we address through the OCCA project.

The directive approach, as seen in OpenMP and OpenACC, relies on a proper mapping between user code and its mapped compiler code transformation. Unfortunately, aside from trivial code snippets, directing proper code transformations tailored for the GPU requires the user to properly manage code transformations through additional #pragma's. In addition, interactions between the host and device such as data allocation, data movement and data freeing requires user management if performance is

of importance. This user management turns the directive approach usage of #pragma's to be equivalent to a library API combined with \_\_attribute\_\_ language extensions, in order to give compiler information about variables and statements. The adoption and improvements of automatic data movement is discussed in chapter 4 and automatic code transformation in chapter 5; however, the aim of the OCCA IR is that of creating a single programming format towards multiple devices.

The source-to-source approach, at least in the context of CUDA to OpenCL, has the advantage of assuming the user is writing in the GPU programming model. CUDA and OpenCL have options for low-level optimizations and multiple memory hierarchies, permitting the use of a higher descriptive language compared to traditional languages, such as C and Fortran. However, available source-to-source translators handle only a subset of CUDA or it's assembly language (PTX) as mentioned in section 1.3. Rather than relying on a proprietary programming language with no standard, a custom programming language became an appealing solution.

Lastly, the wrapper approach was not an option due to the limitation on their routines. However, being able to develop libraries and wrappers using OCCA was a requirement due to their use in application development.

The first step towards creating a custom programming language was to develop an intermediate representation. Developing the OCCA programming model started with a macro-based approach, covering major keywords used in supported modes and unraveling macros based on the chosen backend. By developing the OCCA IR as a macro-based language, there exists the option to further append additional backends. We introduce the OCCA IR through its programming model and specification.

# 2.2.2 Programming Model

Before covering the set of macros making up the OCCA IR, we introduce the programming model For a comprehensive list of the OCCA IR macros, the reader can refer to appendix A. While the OCCA IR programming model is based on the GPU programming model, the major difference is the inclusion of explicit loops to denote parallelism. As discussed in subsection 2.1.3, modern CPU and GPU architectures contain similar aspects in their programming models. Visually shown in figure 2.7 are the similarities between GPU work-group independence and CPU thread-independence, as well as the work granularity between GPU work-items operations and SIMD vector-lane operations. However, rather than imposing implicit iterations over work-groups and work-items as seen in OpenCL and CUDA, we expose work distribution with the for-loop-like macros seen in code listing 2.1 and code listing 2.2. Code listing 2.1 compares the OCCA IR mapping to CUDA and OpenCL while code listing 2.2 compares its mapping to OpenMP.

Figure 2.7: Aside from memory hierarchy similarities, current multicore processors equipped with vector instructions are similar to graphics processing units

```

// (1) CUDA:

// (2) OpenCL:

// (3) OCCA:

// Example kernel

Example kernel

// Example kernel

//

//

with a thread's

with a work-item's

//

showing different

scopes of

11

scope of work

//

scope of work

//

parallelization

__global__ void kern(){

__kernel void kern(){

occaKernel void kern(){

occaOuterForO{

// Work-group Scope

occaInnerFor0{

// Thread Work

// Work-item Scope

// Work-item Scope

}

}

}

}

```

Listing 2.1: Difference between implicit loops in CUDA and explicit loops in the OCCA IR.

```

// (1) OpenMP:

11

Example kernel

11

Example kernel

//

with OpenMP

//

showing different

//

scopes of

parallelization

extern ''C'' void kern(){

occaKernel void kern(){

#pragma omp for

for(int t = 0; t < 8; ++t){

occaOuterForO{

// Thread scope

// Thread scope

#pragma simd 8

for(int v = 0; v < 8; ++v){

occaInnerFor0{

// Vectorization Operations

// Vectorization Operations

}

}

}

}

```

Listing 2.2: Difference between implicit loops in CUDA and explicit loops in the OCCA IR.

We first discuss the OCCA IR for-loop keywords shown in code listing 2.1 and code listing 2.2. Similar to the current GPU programming models, the occaOuterForX loops iterate over independent groupings of compute units where  $X \in \{0, 1, 2\}$  allowing groupings of work-groups in up to three dimensions. Likewise, work-groups can be composed as 1, 2, or 3 dimensional groupings of work-items dictated by occaInnerForX where  $X \in \{0, 1, 2\}$ . If OpenCL and CUDA took this approach for their program-

ming models, the outcome would look similar to that seen in code listing 2.3 and code listing 2.4. The complete macro expansions for the OpenMP, CUDA, and OpenCL modes in OCCA IR for-loops are seen in code listing 2.5.

Listing 2.3: The code listing expands the implicit for-loops found in OpenCL kernels. Loop grouping (1) expands multidimensional work-groups and loop grouping (2) expands multidimensional work-items.

Listing 2.4: The code listing expands the implicit for-loops found in CUDA kernels. Loop grouping (1) expands multidimensional work-groups and loop grouping (2) expands multidimensional work-items.

```

//---[ (A) OpenMP Mode ]-----

extern ''C'' void kern(){

#pragma omp parallel for

for(int wgZ = 0; wgZ < occaOuterDim2; ++wgZ){</pre>

// Loop Grouping (1)

for(int wgY = 0; wgY < occaOuterDim1; ++wgY){</pre>

for(int wgX = 0; wgX < occaOuterDim0; ++wgX){</pre>

// Block Scope

for(int wiZ = 0; wiZ < occaInnerDim2; ++wiZ){</pre>

// Loop Grouping (2)

for(int wiY = 0; wiY < occaInnerDim1; ++wiY){</pre>

for(int wiX = 0; wiX < occaInnerDim0; ++wiX){</pre>

// Thread Scope

}}}

}}}

//---[ (B) CUDA Mode ]-----

__global__ void kern(){

{{{

// Block Scope

// Thread Scope

}}}

}}}

}

//---[ (C) OpenCL Mode ]------

__kernel void kern(){

}}}

// Work-group Scope

// Work-item Scope

}}}

}}}

}

```

Listing 2.5: The code listing shows simplified expansions of the OCCA-for loops for (A) OpenMP-mode, (B) CUDA-mode, and (C) OpenCL-mode.

To truly create a unified programming model that will maintain correctness across the supported backends, we introduce the OCCA IR specification. We begin by stating what is permitted and not permitted between scopes in an OCCA IR kernel as seen in code listing 2.6. More specifically, allowed statements in the following 6 specialized scopes:

- A) Kernel arguments

- B) Outside occaOuterFor loops

- C) Between occaOuterFor loops

- D) Between an occaOuterFor and occaInnerFor loops

- E) Between occaInnerFor

- F) Inside occaInnerFor.

```

occaKernel void kernelName(occaKernelInfoArgs, ... /* (A) */){

// (B)

occaOuterFor1{

// (C)

occaInnerFor1{

//(E)

occaInnerFor2{

// (F)

}

}

}

}

```

Listing 2.6: The code listing shows the specialized scopes inside an OCCA IR kernel.

#### 2.2.2.1 Kernel Arguments

The scope covered in this subsection is denoted by (A) in the code listing 2.6.

We aim to enable any type as a kernel argument, thus provided multiple keywords for describing kernel arguments. The CUDA specification and OpenCL standard contain routines for additional languages to utilize them and thereby allowing OCCA to generate and launch kernels with ease. With the CPU-based backends (serial, OpenMP, and Pthreads), however, we faced restrictions due to the C/C++ language. Two constraints appear: calling kernels with arbitrary arguments and seamlessly passing the occaOuterFor and occaInnerFor bounds.

Listing 2.7: The code listing shows the distinct kernel argument types, where A corresponds to arrays and B to arguments passed by value.

Similarly to Fortran, passing all arguments by reference allowed for a non-templated approach for launching kernels with varying arguments dynamically. While there exists branching to pick the correct function pointer which will launch the OCCA IR kernel, the portable method can be used with multiple frontend languages. Code listing 2.7 shows additional keywords (occaPointer and occaVariable) used to decorate kernel arguments, abstracting data types to control how they're treated by the compiler. occaPointer is used to declare the scope of the memory object in GPU-based modes, while it is mere decoration for CPU-based modes. On the other hand, occaVariable is used as decoration in the GPU-based modes, but allows arguments to be passed by their address in CPU-based modes.

The second requirement relevant to the kernel arguments is the addition of occaKernelInfoArgs. CUDA and OpenCL kernels require loop dimensions prior to launching, a trait lacking on CPU-based modes. In the occa IR expansions for CPU-modes, the occaOuterFor and occaInnerFor loops expand to for-loops whose bounds are passed through the occaKernelInfoArgs macro.

```

const int *occaKernelArgs, int occaInnerId0, int occaInnerId1, int occaInnerId2

```

where occaKernelArgs stores the loop bound information, and the variables occaInnerIdX are the inner loop iterators.

#### 2.2.2.2 Outside occaOuterFor

The scope covered in this subsection is denoted by (B) in the code listing 2.6.

Following the kernel arguments, the kernel usually begins with an occaOuterFor statement. Statements inside the occa IR kernel scope but outside of an occaOuterFor are restricted to constant variable definitions. Because the outer and inner scopes are emulated in GPU-modes, statements are executed once per work-item/thread while statements are only executed once for CPU-modes.

#### 2.2.2.3 Between occaOuterFors

The scope covered in this subsection is denoted by (C) in the code listing 2.6.

Between the occaOuterFor scopes, non-constant Variable definitions are supported with restrictions. Variables decorated with occaShared and occaPrivate can be defined in this scope but not initialized; definitions of these qualifiers are found in subsection 2.2.3. However, variables can only be initialized and not updated due to the emulated scopes in the GPU-modes.

Lastly, occaOuterFor loops are not guaranteed to be executed the given nesting in order. Hence, the iterator for the occaOuterForX loop which is denoted by occaOuterIdX where  $X \in \{0, 1, 2\}$  could execute in any permutation.

#### 2.2.2.4 Between occaOuterFor and occaInnerFor

The scope covered in this subsection is denoted by (D) in the code listing 2.6.

occaInnerFor loops are located inside occaOuterFor loop scopes, but more statements are allowed inside occaOuterFor loops. Declared variables are still required to be constant or decorated with occaShared or occaPrivate; however, conditional statements and loops are supported. The only limitation on conditional statements and loops is that each must contain an occaInnerFor.

#### 2.2.2.5 Between occaInnerFors

The scope covered in this subsection is denoted by (E) in the code listing 2.6.

Between occaInnerFor loops, variable declarations must be decorated with const, occaShared, or occaPrivate. No other statements are supported in this scope.

#### 2.2.2.6 Inside occaInnerFors

The scope covered in this subsection is denoted by (F) in the code listing 2.6.

Inside the inner-most occaInnerFor scope, anything supported by C is supported in the OCCA IR. Similar to occaOuterFor loops, occaInnerFor are not guaranteed to be executed in order. Hence, the iterator for the occaInnerForX loop which is denoted by occaInnerIdX where  $X \in \{0, 1, 2\}$  could execute in any permutation.

## 2.2.3 Device Memory Hierarchy

With the exposure of loop-structures already described, we begin to describe the memory hierarchy exposed by the OCCA IR. Recalling that memory has become one central issue in optimizing for performance, we emphasize memory hierarchy exposure in the OCCA programming model. There are three types of memory layers: global memory, shared memory and register memory; all which are exposed in the OCCA IR. The simplest level of memory to explain is global memory which represents data residing in RAM, be it CPU or GPU DRAM.

Because the concept of shared memory differs between CPU and GPU architectures, the mention of shared memory throughout the thesis proposal will correspond with the GPU shared memory terminology. Shared memory resides in the same physical location as cache for GPUs and can be described as a memory scratchpad found in fast-memory. Important features of shared memory include fast data fetching as well as a synchronization method between work-items in a work-group. By encompassing

work-items in a work-group in the shared memory scope, algorithms can make use of parallel data fetching and storage with visibility throughout the work-group. In the OCCA IR, we represent shared memory with the qualifier occaShared as seen in code listing 2.8. With shared memory being a supported feature in OCCA, we also include local and global barriers to synchronize across work-items in a work-group. An example is given in code listing 2.8.

Listing 2.8: Shown is the barrier implementation to synchronize across a work-group as splitting inner-loops, explicitly stating that all work-items have finished the instructions prior to the barrier.

Lastly, we will discuss registers and some issues surrounding their use. Data stored in registers utilize the fastest memory layer in the memory hierarchy for both CPU and GPU architectures. Hence programmers and compilers try to find a balance between data storage on registers and the amount of registers available to the hardware (for example, prefetching onto registers and reusing them as opposed to fetching from higher latency memory layers). However, the use of barriers causes an issue for OCCA-modes which treat inner-loops serially, such as OpenMP, Pthreads and COI. For example, in code listing 2.9, the variables reg and regArray would normally be overwritten in each loop iteration. In order to keep the code from overwriting reg and regArray, we implement a wrapper for types through the occaPrivate call. For OCCA IR, the

variable holds an array with an entry for each work-item, allowing mutual exclusion of variables through behaving as one in the kernel code.

```

occaKernel void kern(occaKernelInfoArgs){

occaOuterForO{

occaPrivate(int, reg);

// Register

occaPrivateArray(int, regArray, 2); // Register Array: int regArray[2];

occaInnerFor0{

reg = occaGlobalIdO; // reg would normally be overwritten by the loop

// regArray would also normally be overwritten

regArray[0] = 0;

regArray[1] = 1;

occaBarrier(occaLocalMemFence);

occaInnerFor0{

int i = reg;

// Allocating registers normally for only one scope

int d = regArray[0];

}

}

```

Listing 2.9: Shown is a simple example of private variable use to prevent overwriting during each loop iteration.

# 2.3 Application Programming Interface

Apart from the OCCA IR, OCCA implements an application programming interface (API) based on an offload model. This section introduces the abstractions used to generalize modern parallel architectures into an offload model containing features present in high performance computing. We begin with the device, memory, and kernel abstractions, followed by kernel compilation and concluding with additional HPC-related features.

#### 2.3.1 Offload Model and Device Abstractions

While section 2.2 discussed abstractions for programming current parallel architectures, this section discusses the API which make the offload model abstraction possible. The model consists on the three key components that influenced the OCCA host API development: the device, the device memory, and the device kernels.

#### 2.3.1.1 occa::device Class

An occa device acts as a layer of abstraction between the occa API and the API from supported languages. One of the essential features in occa is the ability to target a device at run-time. Choosing the preferred platform at run-time is possible due to just-in-time code generation as seen in code listing 2.10.

```

occa::device device1("mode = Serial");

occa::device device2, device3, device4, device5, device6;

device2.setup("mode = Pthreads, threadCount = 8, schedule = compact");

device3.setup("mode = OpenMP , threadCount = 8, schedule = compact");

device4.setup("mode = OpenCL , platformID = 0, deviceID = 0");

device5.setup("mode = CUDA , deviceID = 0");

device6.setup("mode = COI , deviceID = 0");

```

Listing 2.10: The code listing shows the occa::device class initialization, choosing a backend at run-time while providing a portable and modular method.

An occa device generates a self-contained context and stream from the chosen device, being a socketed processor, GPU or other OpenCL supported devices such as a Xeon Phi or an FPGA. Although multiple contexts within a device are not supported, asynchronous computations are supported through the use of multiple occa device instances. The device's main purpose is to allocate memory and compile kernels for the chosen device. Additional responsibilities of the device wrapper include stream management. Work enqueued onto a stream are launched sequentially, but streams give greater access to asynchronous work; examples can be seen in code listing 2.11.

```

occa::device device;

// ...

// Get current stream

occa::stream streamA = device.getStream();

// Generate a new stream

occa::stream streamB = device.createStream();

// Switch stream

device.setStream(streamB);

occa::streamTag startTag = device.tagStream();

// Work

occa::streamTag endTag = device.tagStream();

double timeTaken = device.timeBetween(startTag, endTag);

```

Listing 2.11: The code listing shows the occa::device class options for creating, updating, and destroying streams as well as timing work between streams.

#### 2.3.1.2 occa::memory Class

The OCCA memory class abstracts the different device memory handles and provides some useful information such as device array sizes. Although memory handling in OCCA facilitates host-device communication, the management of reading and writing between host and device, for performance reasons, currently requires programmer management. Chapter 4 describes an alternative to manual data management using emulated unified memory addressing and automatic data management.

Basic memory initialization, similar to malloc in C, and data transfer can be seen in code listing 2.12.

```

occa::device device;

// ...

// Allocate memory on the host

int *A = (int*) malloc(10 * sizeof(int));

// Allocate memory on the device

occa::memory memoryA = device.malloc(10 * sizeof(int), A);

occa::memory memoryB = device.malloc(10 * sizeof(int));

// Forms of transfering data between

// host and device

memoryA.copyTo(memoryB);

memoryB.copyTo(A);

memoryB.copyFrom(A, 10 * sizeof(int));

// Asynchronous data transfer

memoryA.asyncCopyTo(memoryB);

memoryB.asyncCopyTo(A);

memoryB.asyncCopyFrom(A, 10 * sizeof(int));

```

Listing 2.12: The code listing shows the occa::memory initialization and data transfer options.

#### 2.3.1.3 occa::kernel Class

The OCCA kernel class unites device function handles with a single interface, whether for a function pointer (CPU-based modes), cl\_kernel (OpenCL), or cuFunction (CUDA). When using the OpenCL and CUDA kernel handles, passing the arguments through their respective API is simple, but there are discrepancies when comparing to the OpenMP wrapper. For example, OpenCL and CUDA kernels work-items have access to work-group and work-item counts implicitly. However, C++ functions only have access to the function scope and global namespace, requiring the work-group and work-item counts to be passed as macros or as an argument to the kernel.

Two formats are available for launching occa::kernels, through the function-like () operator or with an argument list. Before launching a kernel, the user is required to pass the outer and inner loop bounds. Examples of kernel building and launching are given in code listing 2.13.

```

occa::device device;

// ...

// Allocate memory on the device

occa::memory memoryA = device.malloc(10 * sizeof(int));

// Build kernel from source