## **Master Thesis Report**

For the master thesis on

# Network Processor based Exchange Terminal – Implementation and evaluation

Department of Microelectronics and Information Technology, Royal Institute of Technology (KTH)

> Daniel Hedberg e98 dhe@e.kth.se

Stockholm, Sweden, 05 December 2002

## Examiner: Prof. Gerald Q. Maguire Jr. KTH Teleinformatics maguire@it.kth.se

#### **Supervisor:**

Markus Magnusson Ericsson Research Markus.Magnusson@uab.ericsson.se

Mikael Johansson Ericsson Research Mikael Johansson @uab.ericsson.se

#### **Abstract**

When communication nodes are connected to different networks, different kinds of Exchange Terminals (ETs) i.e., line card, are used. The different media we consider here have a bit rate between 1.5Mbps to 622Mbps and use protocols such as ATM or IP. In order to minimize the number of different types of ET boards, it is interesting to study the possibility of using Network Processors (NP) to build a generic ET that is able to handle several link layer and network layer protocols and operate at a wide variety of bit rates.

This report investigates the potential of implementing an ET board using a one-chip or two-chip solution using an Intel Network Processor (NP). The design is described in detail including a performance analysis of the different modules (microblocks) used. The report also provides an evaluation of the IXP2400 network processor and contrasts it to some other network processors. The detailed performance evaluation is based on a simulator of the IXP2400, which is part of Intel's Software Development Kit (SDK) version 3.0. In addition, I have investigated: the memory bus bandwidth, memory access latencies, and compared C-compiler against hand-written microcode. These tests were based on using an application for this ET board, which I have implemented.

It proved to be difficult to fit all the required functions into a single chip solution. The result is either one must wait for the next generation of this chip or one has to use a two-chip solution. In addition, the software development environment used in the project was only a pre-release, and not all services worked as promised. However, a clear result is that implementing an ET board, supporting the commonly desired functions, using a Network Processor is both feasible and straightforward.

## Sammanfattning

För att koppla ihop olika noder som befinner sig på olika nätverk, använder man sig av olika Exchange Terminal-kort (ET-kort), s.k. Linjekort. De olika media vi tar i beaktning har en linjehastighet mellan 1.5 Mbps och 622 Mbps och använder protokoll som exempelvis ATM och IP. För att minimera antalet olika ET-kort är det intressant att studera möjligheten att använda sig av Nätverksprocessorer som ett allmänt ET-kort som kan hantera flera olika länklager- och nätverkslager- protokoll, och samtidigt fungera över olika hastigheter.

Den här rapporten utreder möjligheten att implementera ett ET-kort för en eller två nätverksprocessorchip tillverkad av Intel, kallad IXP2400. Designen är beskriven i detalj och inkluderar även en prestandaanalys av flera olika moduler (mikroblock) som använts. Rapporten innehåller även en utvärdering av IXP2400 där den jämförs med en liknande nätverksprocessor från en annan tillverkare. Prestandaanalysen är baserad på en simulator av IXP2400 processorn, som är en del av Intels utvecklingsmiljö kallad IXA SDK 3.0. Slutligen har jag även utvärderat minnesbussarna, minnesaccessen och ett C-kompilatortest gjord med hjälp av assemblergenererad kod och C-kod. Dessa tester gjordes på en applikation av ET-kortet som jag själv har implementerat.

Det visade sig vara svårt att få in alla krav som ställts på bara en nätverksprocessor. Resultatet är antingen att vänta tills nästa version av simuleringsmiljön kommer ut på marknaden eller att använda sig av två nätverksprocessorer. Under projektet användes bara en betaversion av utvecklingsmiljön och det har inneburit att alla funktioner inte fungerar som förväntat. Resultatet visar ändå tydligt att användning av Nätverksprocessorer är både effektiv och enkel att använda.

## **Acknowledgements**

This report is a result of a Master's thesis project at Ericsson Research AB, in Älvsjö during the period of June to beginning of December 2002.

This project would not been successful without these persons:

- Prof. Gerald Q. Maguire Jr., for his knowledge and skills in a broad area of networking, rapid responses to e-mails, helpful suggestions, and genuine kindness.

- Markus Magnusson and Mikael Johansson, my supervisors at Ericsson Research, for their support and on helpful advising when I needed it.

- Magnus Sjöblom, Paul Girr, and Sukhbinder Takhar Singh, three contact people from Intel who supported me with help I needed to understand and program in their Network Processor simulation environment, Intel SDK 3.0

Other people that I want to mention includes Sven Stenström and Tony Rastas, two master thesis students at Ericsson Research that I worked with during my thesis.

Thank you all!

## **Table of Contents**

| 1 |         | ction                                   |    |

|---|---------|-----------------------------------------|----|

|   | 1.1 Ba  | ackground                               | 1  |

|   | 1.2 Pr  | oblem definition                        | 1  |

|   | 1.3 Ou  | utline of the report                    | 2  |

| 2 | Backgr  | ound                                    | 3  |

|   | 2.1 Da  | ata Link-layer Protocol overview        | 3  |

|   | 2.1.1   | HDLC: an example link layer protocol    | 3  |

|   | 2.1.2   | PPP: an example link layer protocol     | 4  |

|   | 2.1.3   | PPP Protocols                           | 5  |

|   | 2.2 PF  | PP Session                              | 6  |

|   | 2.2.1   | Overview of a PPP session               | 6  |

|   | 2.3 In  | ternet Protocol                         | 7  |

|   | 2.3.1   | IPv4                                    | 7  |

|   | 2.3.2   | IPv6                                    | 8  |

|   | 2.4 A   | ГМ                                      | 9  |

|   | 2.4.1   | ATM Cell format                         | 9  |

|   | 2.4.2   | ATM Reference Model                     | 10 |

|   | 2.5 Qu  | ueuing Model                            | 11 |

|   | 2.5.1   | Queues                                  | 12 |

|   | 2.5.2   | Scheduler                               | 12 |

|   | 2.5.3   | Algorithmic droppers                    | 13 |

|   | 2.6 Er  | icsson's Cello system                   | 13 |

|   | 2.6.1   | Cello Node                              | 13 |

|   | 2.6.2   | Exchange Terminal (ET)                  | 14 |

|   | 2.7 No  | etwork Processors (NPs)                 | 15 |

|   | 2.7.1   | Definition of a Network Processor       | 15 |

|   | 2.7.2   | Why use a Network Processor?            | 15 |

|   | 2.7.3   | Existing hardware solutions             | 15 |

|   | 2.7.4   | Network Processors in general           | 16 |

|   | 2.7.5   | Fast path and slow path                 | 17 |

|   | 2.7.6   | Improvements to be done                 | 18 |

|   | 2.8 No  | etwork Processor Programming            | 18 |

|   | 2.8.1   | Assembly & Microcode                    | 18 |

|   | 2.8.2   | High-level languages                    |    |

|   | 2.8.3   | Network Processing Forum (NPF)          | 19 |

|   | 2.9 In  | tel IXP2400                             | 19 |

|   | 2.9.1   | Overview                                | 19 |

|   | 2.9.2   | History                                 | 20 |

|   | 2.9.3   | Microengine (ME)                        | 20 |

|   | 2.9.4   | DRAM                                    | 21 |

|   | 2.9.5   | SRAM                                    | 21 |

|   | 2.9.6   | CAM                                     |    |

|   | 2.9.7   | Media Switch Fabric (MSF)               | 22 |

|   | 2.9.8   | StrongARM Core Microprocessor           |    |

|   | 2.10 In | tel's Developer Workbench (IXA SDK 3.0) |    |

|   | 2.10.1  | Assembler                               |    |

|   | 2.10.2  | Microengine C compiler                  |    |

|   | 2.10.3  | Linker                                  | 26 |

|   | 2.10.4  | Debugger                                | 27 |

|   | 2.10.5  | Logging traffic                         | 27 |

|   | 2.10.6     | Creating a project                                           | 27 |

|---|------------|--------------------------------------------------------------|----|

|   | 2.11 Prog  | gramming an Intel IXP2400                                    | 28 |

|   | 2.11.1     | Microblocks                                                  | 28 |

|   | 2.11.2     | Dispatch Loop                                                | 29 |

|   | 2.11.3     | Pipeline stage models                                        | 30 |

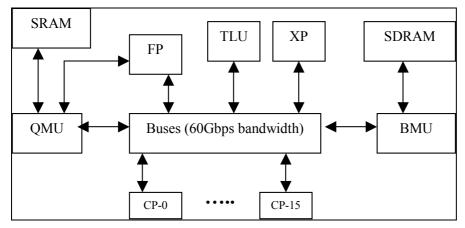

|   | 2.12 Mot   | orola C-5 DCP Network Processor                              | 30 |

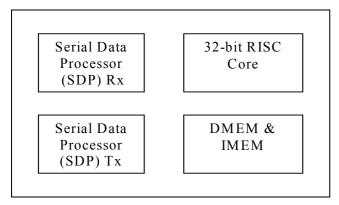

|   | 2.12.1     | Channel processors (CPs)                                     | 31 |

|   | 2.12.2     | Executive processor (XP)                                     | 32 |

|   | 2.12.3     | System Interfaces                                            | 33 |

|   | 2.12.4     | Fabric Processor (FP)                                        | 33 |

|   | 2.12.5     | Buffer Management Unit (BMU)                                 | 33 |

|   | 2.12.6     | Buffer Management Engine (BME)                               |    |

|   | 2.12.7     | Table Lookup Unit (TLU)                                      | 33 |

|   | 2.12.8     | Queue Management Unit (QMU)                                  | 33 |

|   | 2.12.9     | Data buses                                                   |    |

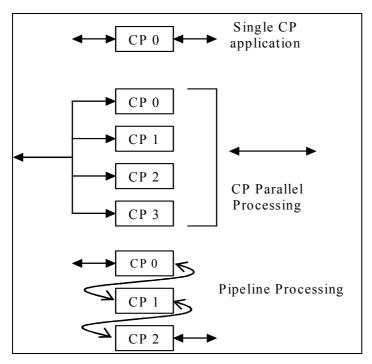

|   | 2.12.10    | Programming a C-5 NP                                         |    |

|   | 2.13 Con   | nparison of Intel IXP 2400 versus Motorola C-5               | 34 |

| 3 |            | solutions                                                    |    |

|   | 3.1 Alca   | atel solution                                                | 36 |

|   | 3.2 Mot    | orola C-5 Solution                                           | 37 |

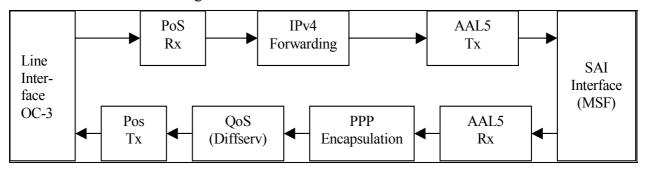

|   | 3.2.1      | Overview                                                     | 37 |

|   | 3.2.2      | Ingress data flow                                            | 38 |

|   | 3.2.3      | Egress data flow                                             | 38 |

|   | 3.3 Thin   | d parties solution using Intel IXP1200                       | 39 |

| 4 | Simulation | on methodology for this thesis                               | 40 |

|   | 4.1 Exis   | sting modules of code for the IXA 2400                       | 40 |

|   |            | sting microblocks to use                                     |    |

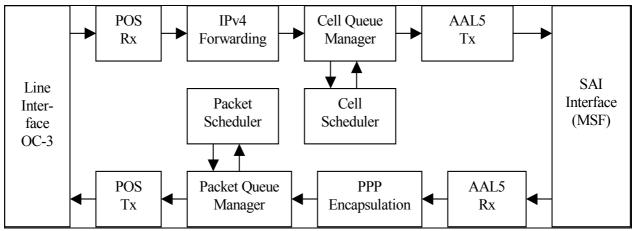

|   | 4.2.1      | Ingress side microblocks                                     | 42 |

|   | 4.2.2      | Egress side microblocks                                      | 46 |

|   | 4.3 Eva    | luating the implementation                                   | 47 |

| 5 | Performa   | nce Analysis                                                 | 49 |

|   | 5.1 Foll   | owing a packet through the application                       | 49 |

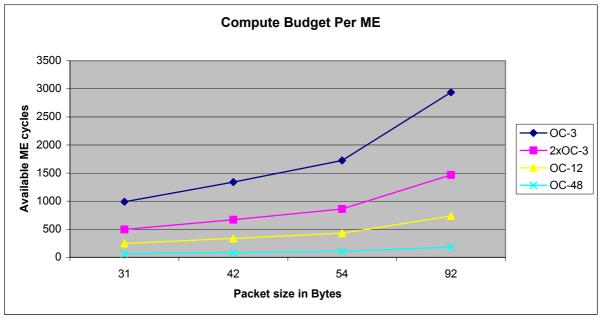

|   | 5.1.1      | Performance budget for microblocks                           | 51 |

|   | 5.1.2      | Performance Budget summary                                   | 54 |

|   | 5.2 Perf   | Formance of Ingress and Egress application                   | 54 |

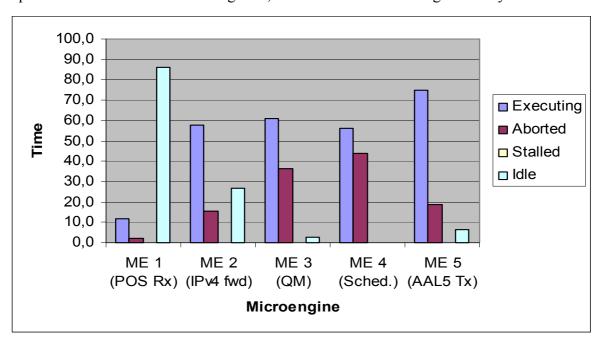

|   | 5.2.1      | Ingress application                                          |    |

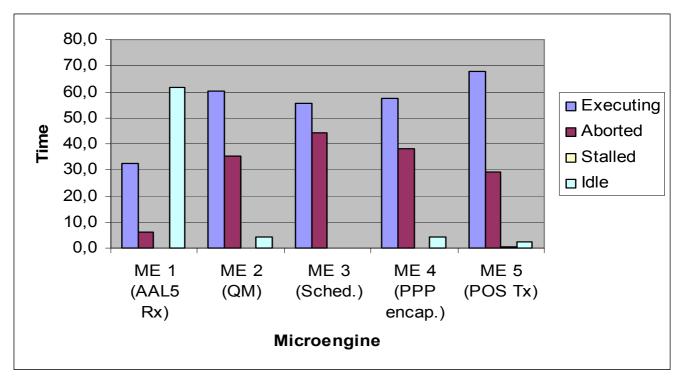

|   | 5.2.2      | Egress application                                           | 56 |

|   | 5.2.3      | SRAM and DRAM bus                                            | 58 |

|   | 5.2.4      | Summary of the Performance on Ingress and Egress application | 58 |

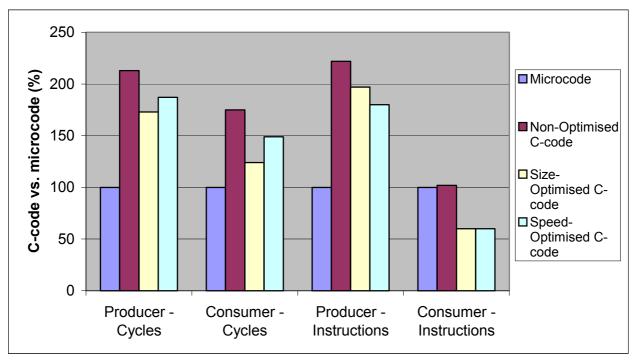

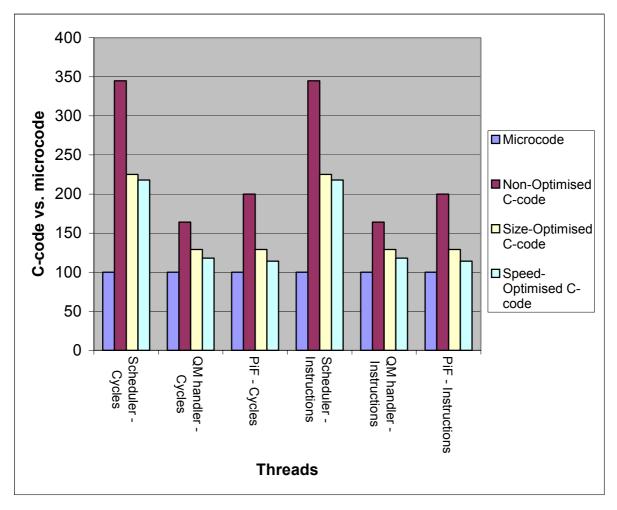

|   | 5.3 C-ce   | ode against microcode                                        | 59 |

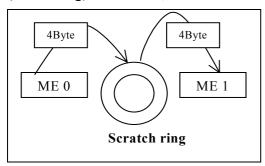

|   | 5.3.1      | Compiler test on a Scratch ring                              |    |

|   | 5.3.2      | Compiler test on the cell based Scheduler                    |    |

|   | 5.3.3      | Compiler test on the OC-48 POS ingress application           | 61 |

|   | 5.4 Mei    | nory configuration test                                      |    |

|   | 5.4.1      | DRAM test                                                    | 62 |

|   | 5.4.2      | SRAM test                                                    |    |

|   | 5.5 Fun    | ctionality test on IPv4 forwarding microblock                | 62 |

|   |            | p back: Connecting ingress and egress                        |    |

|   |            | umptions, dependencies, and changes                          |    |

|   | 5.7.1      | POS Rx.                                                      |    |

|   | 5.7.2      | IPv4 forwarding block                                        |    |

| 5.7.3 Cell Queue Manager                                        | 64 |

|-----------------------------------------------------------------|----|

| 5.7.4 Cell Scheduler                                            | 64 |

| 5.7.5 AAL5 Tx                                                   | 64 |

| 5.7.6 AAL5 Rx                                                   | 65 |

| 5.7.7 Packet Queue Manager                                      | 65 |

| 5.7.8 Packet Scheduler                                          | 65 |

| 6 Conclusions                                                   | 66 |

| 6.1 Meeting our goals                                           | 66 |

| 6.2 How to choose a Network Processor                           | 66 |

| 6.3 Suggestions & Lessons Learned                               | 67 |

| 7 Future Work                                                   | 69 |

| Glossary                                                        | 70 |

| References                                                      | 72 |

| Books                                                           | 72 |

| White papers & Reports                                          | 72 |

| RFC                                                             | 72 |

| Conference and Workshop Proceedings                             | 73 |

| Other                                                           |    |

| Internet Related Links                                          | 74 |

| Appendix A – Requirements for the ET-FE4 implementation         | 75 |

| Appendix B – Compiler test on a Scratch ring                    | 79 |

| Appendix C – Compiler test on Cell Scheduler                    | 82 |

| Appendix D – Compiler test on the OC-48 POS ingress application | 85 |

| Appendix E – Configure the Ingress Application                  | 87 |

| Appendix F – Configure the Egress Application                   | 89 |

| Appendix G – Stream files used in Ingress and Egress flow       | 91 |

| Appendix H – Test specification on IPv4 microblock              | 95 |

## 1 Introduction

## 1.1 Background

Traditionally, when nodes are connected to different networks, different kinds of Exchange Terminal (ETs) i.e., interface boards are used. The different media we will consider here can have a bit rate between 1.5Mbps to 622Mbps and use protocols like ATM or IP. In order to minimize the number of different boards, it is interesting to use Network Processors (NP) to build a generic ET that is able to handle several protocols and bit rates.

#### 1.2 Problem definition

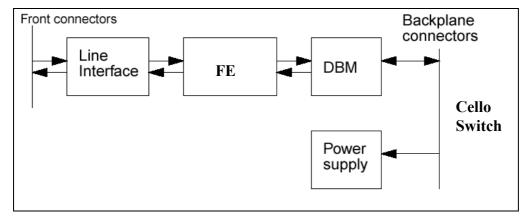

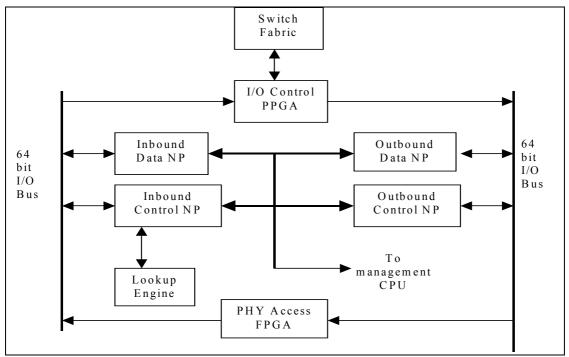

In this thesis, the main task is to study, simulate, and evaluate an ET board called ET-FE4 which is used as a plugin-unit in the Cello system (see section 2.6). Figure 1 below shows an overview of blocks that are included on this ET board. The data traffic is first interfaced via a Line Interface, in this case a Packet over SONET (POS) interface, as the board is connected to two SDH STM-1 (OC-3) links. Traffic is processed, just as in a router using a Forwarding Engine (FE) in hardware to obtain wire speed routing. Error packets or special packets, called exception packets are handled in software by an on-board processor of the Device Board Module (DBM). After it has been processed, the traffic is sent on the backplane, where it is connected to a Cello-based switch fabric.

Figure 1. Block diagram of ET-FE4

To run different protocols such as IP or ATM, it is usually necessary to add or remove hardware devices on the board or to reprogram them (as in the case of Field Programmable Gate Arrays (FPGA)). Because each of these protocols has specific functionality, it is therefore generally necessary that hardware differ between these ET boards. By using a Network Processor (NP), all the needed functionality can be implemented on the **same** board. It only requires changes in the software load, to define the specific functionality.

This thesis concentrates on the implementation of the Forwarding Engine (FE) block on the ET board (see Figure 1). To implement this block, a study of the existing forwarding functionality was necessary. Then all the requirements for the FE block functionality needed to be refined to fit within the time duration of this thesis project. All the necessary requirements and functionalities are listed in Appendix A. Once the implementation phase was completed, an evaluation was performed to verify that the desired result was achieved

(i.e., wire speed forwarding). To understand better how the networking processing technology works, a comparison between Motorola's Network Processor C-5 and Intel's IXP2400 was performed. Finally, to evaluate the workbench for the Network Processor, a memory test, and a C-compiler test was performed.

## 1.3 Outline of the report

Chapter 2 introduces the main protocols used during the implementation of the application. Then it states how Network Processor programming works with assembly and C programming. It follows with a description of Ericsson's Cello System used in mobile 3G platforms. Finally, the chapter describes two Network Processors, Intel IXP2400 and Motorola C-5, and a comparison of both processors. Moreover, readers who are familiar with HDLC, PPP, IP, and ATM can skip the first sections up to 2.5. A reader who is familiar with Network Processor Programming, Ericsson's Cello system, Intel IXP2400, and Motorola C-5 can skip the rest of the chapter.

Chapter 3 explains the existing solutions, both with other Network Processors and with third-part companies using Intel Network Processors.

Chapter 4 provides a detailed description of how to solve the problem stated with simulation methodologies. By using existing modules (i.e. microblocks), an application can be built to achieve the goals of the project. The chapter also describes a briefly overview of methods to use in the evaluation phase of the project.

Chapter 5 analyses the application to se if it reaches wire speed forwarding. It also provides some basics test of the C-compiler, where a test on both a small and a large program of C-code and microcode are compared. In the analyses, a performance test of the application is described and a theory study on how long a packet take to travel through the application.

Chapter 6 summarises the results of this work and compares with the stated goals. It provides suggestions and Lessons Learned for the reader.

Chapter 7 indicates a suggested future work of the thesis and if application upgrades are necessary and other investigation.

## 2 Background

This chapter starts with an overview of all the protocols used in the applications developed for this thesis. In following, there are sections about Network Processors in general and how to program them. Section 2.6 describes an important part of the project where it describes briefly how Ericsson's Cello system works and the Exchange Terminal that is going to be implemented. Finally, the section describes two examples of popular Network Processors, Intel IXP2400 and Motorola C-5 and a comparison between them.

## 2.1 Data Link-layer Protocol overview

## 2.1.1 HDLC: an example link layer protocol

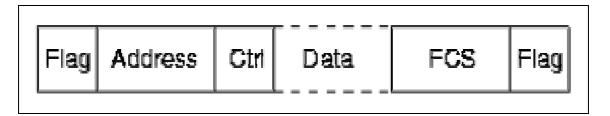

High-level data link control (HDLC) specifies a standard for sending packets over serial links. HDLC supports several modes of operation, including a simple sliding window mode (see section 7 in [4]), for reliable delivery. Since the Internet Protocol family provides retransmission via higher layer protocols, such as TCP, most Internet link layer usage of HDLC, use the unreliable delivery mode, "Unnumbered Information" (See [1]). As shown in Figure 2, the HDLC frame format has six fields. The first and the last field are the flag field, used for synchronising by the receiver so it knows when a frame starts and ends. The flag has normally "01111110" in binary and this sequence cannot appear in the rest of the frame, to enforce this requirement, the data may need to be modified by bit stuffing (described below).

Figure 2. HDLC's frame structure

The second field is the address field, used for identifying the secondary station that sent or will receive the frame. The third field is the Control field which is used for specifying the type of message sent. The main purpose of this field is to distinguish frames used for error and flow control, when using higher-level protocols. The fourth field is the Data field, also called the HDLC information field and is the actual payload data used for the upper layering protocols. The Frame Check Sequence (FCS) field is used to verify the data integrity of the frame and to enable error detection. The FCS is a 16 bit Cyclic Redundancy Check (CRC) calculated using the polynomial  $x^{16} + x^{12} + x^5 + 1$ .

## Bit stuffing

On bit-synchronous links, a binary 0 is inserted after every sequence of five 1s (bit stuffing). Thus, the longest sequence of 1s that may appear of the link is 0111110 - one less than the flag character. The receiver, upon seeing five 1s, examines the next bit. If zero, the bit is discarded and the frame continues. If one, then this must be the flag sequence at the start or end of the frame.

Between HDLC frames, the link idles. Most synchronous links constantly transmit data; these links transmit either all 1s during the inter-frame period (*mark idle*), or all flag characters (*flag idle*).

#### **Use of HDLC**

Many variants of HDLC have been developed. Both PPP protocol and SLIP protocol use a subnet of HDLC's functionality. ISDN's D channel uses a slightly modified version of HDLC. In addition, Cisco's routers use HDLC as a default serial link encapsulation.

## Transmission techniques

When transmitting over serial lines, two principal transmissions are used. First synchronous, which enables you to send or receive a variable length of bytes. The second transmission is asynchronous, which only sends or receives one character at a time.

These two techniques are used over a several different media types (i.e., physical layers), such as:

- EIA RS-232

- RS-422

- RS-485

- V.35

- BRI S/T

- T1/E1

- OC-3

For the ET Board used in this thesis, the media type will be OC-3. OC-3 is a standard for telecommunications running at 155.52 Mbps, it makes 149.76Mbps available to the PPP protocol that will be used.

## 2.1.2 PPP: an example link layer protocol

Point-to-point Protocol (PPP) is a method of encapsulating various datagram protocols into a serial bit stream so that it can be transmitted over serial lines. PPP is a HDLC like frame that uses a subnet of the functionalities that HDLC provides. Some of the restrictions for the PPP frame compared to the HDLC like frame are:

- The address field is fixed to the octet 0xFF

- The control field is fixed to the octet 0x03

- The receiver must be able to accept an HDLC information field size of 1502 octets

Another thing to remember is that the HDLC information field contains both the PPP Protocol field and the PPP information field (Data field). The PPP frame format is shown in Figure 3 below.

| 1    | 1       | 1       | 2        | Variable | 2 or 4 |

|------|---------|---------|----------|----------|--------|

| Flag | Address | Control | Protocol | Data     | FCS    |

Figure 3. PPP frame format

The Protocol field identifies the type of message being carried. This could be a PPP control message such as LCP, ECP, CCP, IP-NCP (described further below) or it could be network layer datagrams such as IP or IPX. The protocol field can be 1-2 bytes depending if it is

compressed or not. The PPP information field for PPP contains the protocol packet as specified in the protocol field. At the end of the PPP frame, there is a FCS field with the same functionality as the FCS described earlier.

There are three framing techniques used for PPP. The first one is Asynchronous HDLC (ADHLC) used for asynchronous links often used for modems on ordinary PC's. The second one is Bit-synchronous HDLC mostly used for media types such as T1 or ISDN links. It has no flow control, there is no escape character used, and the framing and CRC work is done by the hardware. The last technique is Octet-synchronous HDLC, similar to ADHLC with the same framing and escape codes. This technique is also used on special media with buffer-oriented hardware interfaces. The most common buffer-oriented interfaces are SONET and SDH. In this thesis, I have concentrated on a particular interface in the SDH family called OC-3 which operates at 152.52 Mbps.

#### 2.1.3 PPP Protocols

PPP contains several protocols such as LCP, NCP and IPCP (Described below).

#### **Link Control Protocol (LCP)**

Before a link is considered ready for use by network-layer protocols, a specific sequence of events must happen. The LCP provides a method of establishing, configuring, maintaining and terminating the connection. There are three classes of LCP packets:

- Link Configuration packets, establish and configure the link

- Link Termination packets, terminates the link

- Link Maintenance packets, manages and debugs a link

#### **Network Control Protocol (NCP)**

NCP is used to configure the protocol operating at the network layer. One example is to assign dynamic IP addresses to the connecting host.

#### **Internet Protocol Control Protocol (IPCP)**

The Internet Protocol Control Protocol is responsible for configuring, enabling, and disabling the IP protocol modules on both ends of the PPP link. PPP may not exchange IPCP packets until PPP has reached the Network Protocol Layer phase (described below). IPCP has the same functionality as the LCP protocol with the following exceptions:

- It supports exactly one IPCP packet included in the Information field. The Protocol field code is 0x8021

- Only codes 1-7 are supported in the code field. Other codes are treated as unrecognised.

- IPCP packets cannot be exchanged until PPP has reached the Network layer protocol state.

More details about IPCP are described in [13].

#### 2.2 PPP Session

A PPP session is divided into four main phases:

- Link establishment phase

- Authentication phase

- Network-layer protocol phase

- Link termination phase

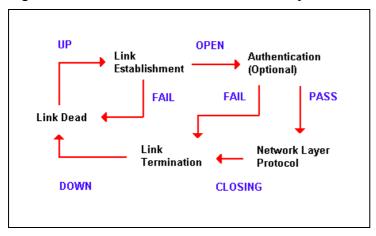

Figure 4 shows an overall view of these four phases including the link dead phase.

Figure 4. A link state diagram

#### 2.2.1 Overview of a PPP session

To establish communication over a point-to-point link, each end of the PPP link must first send Link Control Protocol (LCP) packets to configure and test the data link. Then an optional authentication phase can take place. To use the network layer, PPP needs to send Network Control Protocol (NCP) packets. After each of the network layer protocols has been configured, datagrams can be sent over this link. The link remains up as long as the peer does not send an explicit LCP or NCP request to close down the link.

## Link establishment phase

In this phase, each PPP device sends LCP packets to configure and test the data link. LCP packets contain a Configuration Option field which allows devices to negotiate the use of options, such as:

- Maximum Receive Unit (MRU) is the maximum size of the PPP information field that the implementation can receive.

- Protocol Field Compression (PFC) is an option used to tell the sender that it can receive compressed PPP protocol fields.

- FCS Alternatives, allows the default 16-bit CRC to be negotiated into either a 32-bit CRC or disabled entirely.

- Magic Numbering, is a random number which is used for distinguish the two peers and detect error conditions such as loop back lines and echoes. See section 3 in [1] for further explanation.

PPP uses messages to negotiate parameters between all protocols that are used. All these parameters are well described in [17]. We see that there are four of these parameters described that are used more than the others are and here is a short summary of them:

- Configure-Request, tells the peer system that it is ready to receive data with the enclosed options enabled

- Configure-Acknowledgement, the peer responds with this acknowledgement to indicate that all enclosed options are now available on this peer.

- Configure-Nack, responds with this message if some of the enclosed options were not acceptable on the peer. It contains the offending options with a suggested value of each of the parameters.

- Configure-Reject, responds with this message if it does not recognise one or more

enclosed options. It contains these options to let the sender now witch options to

remove from the request message.

## **Authentication phase**

The peer may be authenticated after the link has been established, using the selected authentication protocol. If authentication is used, it must take place before starting the network-layer protocol phase. PPP supports two authentication protocols, Password Authentication Protocol (PAP) and Challenge Handshake Authentication Protocol (CHAP) [21]. PAP requires an exchange of user names and clear-text passwords between two devices and PAP passwords are sent unencrypted. Instead, CHAP uses authentication agent (typically used by a server) to send to a client program using a random number and an ID value only once.

## **Network-layer protocol phase**

In this phase, the PPP devices send NCP packets to choose and configure one or more network layer protocols (such as IP, IPX, and AppleTalk). Once each of the chosen network-layer protocols has been configured, datagrams from this network-layer protocol can be sent over the PPP link.

## Link termination phase

LCP may terminate the link at any time when a request comes from a user or a physical event.

#### 2.3 Internet Protocol

Internet Protocol (IP) [13] is designed for use in packet switch networks. IP is responsible for providing blocks of data, called datagrams from a source to a destination. Source and destination are identified through fixed length IP addresses. IP also supports fragmentation and reassembling of large datagrams if transmission bandwidth is small on a network. Today, there exist two versions of the Internet Protocol, version 4 (IPv4) and version 6 (IPv6). IPv4 is the old protocol that now has been upgraded to a newer version, IPv6.

#### 2.3.1 IPv4

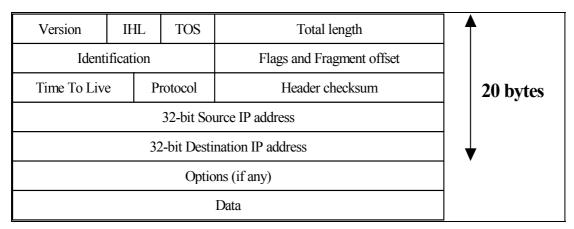

One IPv4 datagram consists of a fixed length header of 20 bytes and a variable-length payload part. Both destination and source addresses are 32-bit numbers placed in the IP header shown in Figure 5 on next page.

Figure 5. IP datagram

Here follows a short explanation of all the fields in the IP header:

- Version: Shows which version of the Internet Protocol a datagram belongs to

- Internet Header Length (IHL): Shows how long the header is. The minimum value is 5 bytes which is the length when no options in use

- Type of Service (TOS): Gives a priority to a datagram

- Total length: Includes both header and payload data of a datagram. The maximum value of packet size is 65 535 bytes

- Identification: Used for a destination to identify a fragment to the correct datagram

- Flags and Fragment offset: This field shows where in the datagram a certain fragment belongs to

- Time To Live: Maximum life time for a datagram in a network

- Protocol: Shows which IP User (Example TCP) is destined for

- Header checksum: Is calculated only for the IP header

- Source IP-address: Is the address where the datagram was sent from

- Destination IP-address: Shows the final destination address for the datagram

- Options: Shows different optional choices such special packet routes etc.

- Data: Actual user specific data

For more details of the IPv4 protocol, look at [2] and [3].

#### 2.3.2 IPv6

Internet Protocol version 6 (IPv6) [20] is known as the new version of the Internet Protocol, which is designed to be an evolutionary step from IPv4. It is a natural increment to IPv4 and one of the big advantages is the address space available. IPv4 had 32-bit address while IPv6 now uses 128-bit address. It can be installed as a normal software upgrade in Internet devices and is interoperable with the current IPv4. Its deployment strategy is designed to not have any flag days or other dependencies. A flag day means a software change that is neither forward-nor backward-compatible, and which is costly to make and costly to reverse. IPv6 is designed to run well on high performance networks (e.g. Gigabit Ethernet, OC-12, ATM, etc.) and at the same time still be efficient for low bandwidth networks (e.g. wireless). In addition, it provides a platform for new Internet functionality that will be required in the near future.

The feature of IPv6 includes:

- Expanded Routing and Addressing Capabilities

IPv6 increases the IP address size from 32 bits to 128 bits, to support more levels of addressing hierarchy and a much greater number of addressable nodes, and simpler auto-configuration of addresses. Multicast and anycast have been built in IPv6 as well. Benefiting from big address space and well-designed routing mechanism, for example, Mobile IP, it make it possible to connect anyone everywhere at any time.

- Simplified but Flexible IP Header

IPv6 has a simplified IP header, some IPv4 header fields have been dropped or made optional, to reduce the common-case processing cost of packet handling and to keep the bandwidth cost of the IPv6 header as low as possible despite the increased size of the addresses. Even though the Ipnv6 addresses are four times longer than the IPv4 addresses, the IPv6 header is only twice the size of the IPv4 header. To make it flexible enough to support new service in future, header options are introduced.

- Plug and Play Auto-configuration Supported

A significant improvement of IPv6 is that it supports auto-configuration in host. Every device can plug and play.

- Quality-of-Service Capabilities

IPv6 also designed for support QoS. Although there are no clear idea on how to implement QoS in IPv6, IPv6 reserve the possibility to implement QoS in future.

- Security Capabilities

IPv6 includes the definition of extensions, which provide support for authentication, data integrity, and confidentiality. This is included as a basic element of IPv6 and will be included in all implementations.

## 2.4 ATM

Asynchronous Transfer Mode, ATM is a proposed telecommunications standard for Broadband ISDN. The basic idea is to use small fixed packets (cells) and switch these over a high-speed network on a hardware level.

ATM is a cell-switching and multiplexing technology that combines the benefits of circuit switching and packet switching such as constant transmission delay, guaranteed capacity, flexibility and efficiency for intermittent traffic. ATM cells are delivered in order, but it is no guarantee for delivery. Line rate for ATM cells are 155 Mbps, 622 Mbps or more. This section describes briefly how ATM cells look like and which layers are used.

#### 2.4.1 ATM Cell format

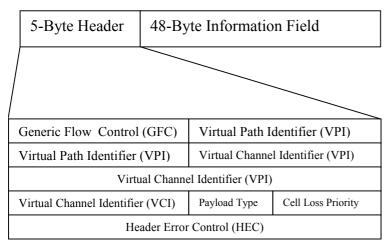

An ATM cell is a short fixed-length packet of 53 bytes. It consists of a 5-byte header containing address information and a fixed 48 bytes information field (See Figure 6 on next page). The ATM standards groups (ATM Forum) [52] have defined two header formats: The UNI header format (defined by the UNI specification) and the Network-Node Interface (NNI) header format (defined by NNI specification). The only difference between the two headers is the GFC field. This field is not included in the NNI header. Instead, the VPI field is increased to 12 bits.

Figure 6. ATM Cell

The ATM Cell header fields include following:

- *Generic Flow Control (GFC):* First 4 bits of the cell header contain the GFC, used for control traffic flow onto the ATM network by UNI.

- Virtual Path Identifier (VPI): Next 8 bits contain the VPI used to specify a virtual path on the physical ATM link.

- *Virtual Channel Identifier (VCI):* Next 16 bits contain the VCI used to specify a virtual channel within a virtual path on the physical ATM link.

- Payload Type (PT): Next 3 bits contain the PT used to identify the type of information the cell is carrying (For example, user data or management information).

- *Cell Loss Priority (CLP):* Last 4 bits indicate the CLP used to identify the priority of the cell and whether the network can discard it under heavy traffic conditions.

- *Header Error Control (HEC):* Last byte of the ATM header contains HEC used to guard against misdelivery of cells due to header or single bit errors.

All 48-bytes of payload (Information field) can be data or it can also be optionally 4 byte ATM adaptation layer and 44-bytes of actual data depending if a bit in the control field is set. This enables fragmentation and reassembly of cells into larger packets at the source and destination. The control field have also a bit to specify whether the ATM cell is a flow control cell or an ordinary cell.

The path of an ATM cell passing through the network is defined by its virtual path identifier (VPI) and virtual channel identifier (VCI), used in the ATM cell header above. Together, these fields specify a connection between two end-points in an ATM network.

#### 2.4.2 ATM Reference Model

In the reference model, ATM consists of four layers: Physical layer, ATM layer, ATM adaptation layer, and higher layers. First is the physical layer which controls the transmission and reception of bits on the physical medium. It also keeps track of ATM cell boundaries and it package cells into the appropriate type of frame for the physical medium being used.

Second layer is the ATM layer, defines how two nodes transmit information between them and is responsible for establishing connections and passing cells through the ATM network. Third layer is ATM adaptation layer (AAL) used to translate between larger Service Data Units (SDU) of upper layer processes and ATM cells.

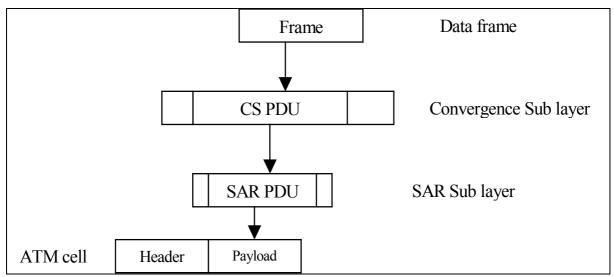

The AAL layer is divided into two sub layers: Convergence Sublayer (CS), Segmentation and Reassembly (SAR) Sub layer. These two layers convert variable-length data into 48-byte segments. ITU-T has defined different types of AALs, AAL3, AAL3/4, AAL4, and AAL5. These handle different kinds of traffic needed for applications to works with packets larger than a cell. Some other AAL services are flow control, timing control and handling of lost and bad inserted cell conditions. The most common AAL is AAL5, mostly used for UDP. Next section below describes AAL5 more briefly.

#### AAL5

AAL5 is the adaptation layer used to transfer data, such as IP over ATM and local-area network (See Figure 7). Packets to be transmitted can vary from 1 to 65,535 bytes. The Convergence Sublayer (CS) of AAL5 appends a variable-length pad and an 8-byte trailer to form a frame, creating a CS Protocol Data Unit (PDU). The pad is used to fill in if the data is not big enough to fit in a 48-byte payload of the ATM cell. The trailer includes the length of the frame and a 32-bit CRC computed across the entire PDU. The SAR layer segments the CS PDU into 48-byte blocks and the ATM layer places each block into the payload field of an ATM cell. For all cells except the last one of a data stream, a bit in the PT field is set to be zero to indicate that the cell is not the last cell in a frame. For the last cell, the bit is set to one. When the cell arrives to its destination, the ATM layer extracts the payload field from the cell, the SAR layer reassembles the CS PDU and uses the CRC and the length field to verify that the frame has been transmitted and reassembled correctly.

Figure 7. ATM Adaptation Layer 5

## 2.5 Queuing Model

Queuing is a function used in routers, line cards etc. The queuing lends itself to innovation due to it is design to allow a broad range of possible implementations using common structures and parameters [22].

Queuing systems perform three distinct functions:

- It store packets using queues

- Modulates the departure of packets belonging to various traffic streams using scheduler

- Selectively discards packets using algorithmic droppers

#### **2.5.1 Queues**

Queuing elements modulate the transmission of packets belonging to different traffic streams and determine ordering of packets, store them temporarily or discard them. Packets are usually stored either because there is a resource constraint such as available bandwidth, which prevents immediate forwarding, or because the queuing block is being used to alter the temporal properties of a traffic stream (i.e., shaping).

Packets are discarded for one of the following reasons:

- Buffering limitations

- A buffer threshold has exceeded (including shaping)

- A feedback control signal used to reactive control protocols such as TCP

- A meter exceeds a configured profile (i.e., policing).

#### **FIFO**

First in First out (FIFO) queue is the simplest queuing algorithm and is widely used over Internet. It leaves all the congestion control to the edger (i.e. TCP). When the queue gets full, packets are dropped.

#### 2.5.2 Scheduler

A scheduler is a queuing element, which gates the departure of each packet arriving on one of its inputs. It has one or more inputs and exactly one output. Each input has an upstream element to which it is connected, and a set of parameters which affects the scheduling of packets received at that input.

The scheduling algorithm might take any of the following as its input(s):

- Static parameters such as relative priority associated with each input of the scheduler

- Absolute token bucket parameters for maximum or minimum rates associated with each input of the scheduler

- Parameters, such as packet length or Differentiated Services Code Point (DSCP) associated with the packet currently present at input.

- Absolute time and/or local state

Here follows a short summary of common scheduling algorithms:

- Rate Limiting, packets from a certain traffic class are assigned a maximum transmission rate. The packets are dropped if a certain threshold is reached.

- Round Robin, All runnable processes are kept in a circular queue. The CPU scheduler goes around this queue, allocating the CPU each process for a time-interval.

- Weighted Round Robin (WRR), Works in same manner as Round Robin, where packets from different streams are queued and scheduled for transmission in an assigned priority order.

- Weighted Fair Queuing (WFQ) and Class Based Queuing (CBQ), when packets are routed to a particular output line-card interface, each flow receives an assigned amount of bandwidth.

- Weighted Random Early Detection (WRED), Packets from different classes are queued and scheduled for transmission. When packets from a low priority use too much bandwidth, a certain percentage of its packets are randomly dropped.

- First Come First Serve (FCFS)

Some scheduler uses Traffic Load Balancing, which is not really a scheduling algorithm. Traffic Load Balancing issues equal-size tasks to multiple devices. This involves queuing and fair scheduling of packets to devices such as database and web servers.

## 2.5.3 Algorithmic droppers

The algorithmic dropper is a queuing element responsible for selectively discard packets that arrive at its input, based on some discarding algorithm. The basic parameters used in the algorithmic droppers are:

- Dynamic parameters, using average or current queue length

- Static parameters, using threshold on queue length

- Packet-associated parameters, such as DSCP values

## 2.6 Ericsson's Cello system

The Cello system is a product platform for developing switching network nodes such as simple ATM switches, Radio Base Stations (RBS), or Radio Network Controllers (RNC). The Cello system has a robust real time distributed telecom control system which supports ATM, TDM [4], or IP transport. The Cello system is designed for interfaces that run at 1.5 Mbit/s – 155 Mbit/s. In the backbone, the limit is even higher (622 Mb/s). Therefore, there should not be a problem to upgrade card such as ET boards to run at 622 Mb/s.

To build a switching network node, we need both the Cello platform and a development environment. The platform consist of both hardware and software modules. To transport cells from one device to another, it uses a Space Switching System (SPAS). The SPAS switch is an ATM based switch which connects to internal interfaces, external interfaces, or both. Internal interfaces can be Switch Control Interfaces (SCIs), interfaces providing node topology, or interfaces to administer the protection switching of the internal system clock. External interfaces can be Switch Access Configuration Interfaces (SACI) or a hardware interface, Switch Access Interface (SAI) [37], which is used as an access point for data transfer through a switch.

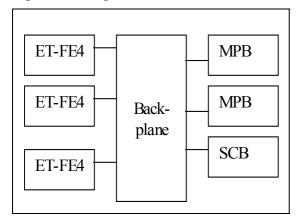

#### 2.6.1 Cello Node

A Cello node is simply a switching network node which can be scaled in both size and capacity. The Cello node scales in size depending on how many subracks it consists of. At least one subrack (see Figure 8) must be connected. A subrack has several Plugin-Units such as Main Processor Boards (MPBs), Switch Core Boards (SCBs), different ET boards, and device boards. All of these units are attached to a backplane (SPAS Switch) and a Cello node needs at least one processor board depending on the processing power needed and the level of redundancy desired. A bigger Cello node consists of several subracks that are connected together through SCB links.

Figure 8. A Single subrack configuration [5]

## 2.6.2 Exchange Terminal (ET)

Traditionally Ericsson produced several Exchange Terminal boards which handle both ATM and IP traffic. Different ET boards are necessary for implementing adaptations to different physical media and different link layer and network layer standards. Some of them are listed below:

- ET-M1, ATM board supports link speeds over 1.5 Mbit/s and interfaces to T1/E1 links, supports 8 ports

- ET-M4, ATM board supports link speeds over 155 Mbit/s and interfaces to STM-1/OC-3 optical or electrical links and supports 2 ports

- ET-FE1, IP forwarding board supports link speeds over 1.5 Mbit/s and interfaces to T1/E1 links

- ET-FE4 IP forwarding board supports link speeds over 155 Mbit/s and interfaces to 2 optical STM-1/OC-3 links

This thesis concentrates on the existing ET-FE4 board and specifically the forwarding engine block (see Figure 1) on it. As described in the figure, the ET-board consists of three main modules: Line Interface, Forwarding Engine, and the Device Board Module. Here follows a short description of these modules.

#### Line interface

The line interface performs clock recovery and data extraction. It consists of two optical modules and PMC-Sierra 5351chip [29], which processes duplex 155.52 Mbit data streams (OC-3). The PMC-Sierra chip is a STM 1 payload extractor sending out extracted data on a POS-PHY Lev 2 link connected to the forwarding engine.

## **Forwarding Engine**

The forwarding engine contains two Field Programmable Gate Arrays (FPGAs) [36]. One FPGA is used for manage IP forwarding and some QoS. For the ingress part, the FPGA handles IP forwarding using forwarding table lookup. On the egress part, the FPGA is used for some QoS functionality such as Diffserv queuing of packets. The second FPGA contains both a HDLC Protocol unit and a PPP protocol unit used for processing PPP packets and transmitting packets over serial links. It also has a Multilink Protocol unit for fragmenting packets and transmitting them over serial links.

## **Device Board Module (DBM)**

The Device Board Module (DBM) is a processor platform for the device boards used in Cello. It contains interfaces for test and debugging as well as a connector to the backplane. The DBM has one FPGA, used for segmentation and reassembly of AAL5 packets and AAL0 cells. It has also a main processor, PowerPC 403GCX [28], that handles all the instructions needed to handle the traffic from the ET board to the backplane.

## 2.7 Network Processors (NPs)

#### 2.7.1 Definition of a Network Processor

A Network Processor (NP) is a programmable (processor) integrated as a single semiconductor device which is optimised to primarily handle network processing tasks. These processing tasks include: receiving data packets, processing them, and forwarding them.

## 2.7.2 Why use a Network Processor?

Today, the networking communication area is constantly changing. The bandwidth grows exponentially and will continue for many years ahead. The growing bandwidth of optical fibre results to even grow faster than the speed of silicon. For example, the CPU clock speed grows with a factor of 12 and the network speed increases with a factor of 240. Higher bandwidth results in more bandwidth-hungry services on Internet, such as Voice over IO (VoIP), streaming audio and video, Peer-to-Peer (P2P) applications, and many others which we have not yet thought of. For networks to effectively handle these new applications, new protocols need to be supported to fulfil new requirements including differentiated services, security, and various network management functions.

To implement all these changes in hardware would be both inefficient and costly for both developer and customer. For example, when developing a new protocol, hardware needs to be developed to handle this protocol and the hardware development cycle is often much longer than the software development cycle. Therefore, a programmable configuration would be preferred, as it only needs to be modified or reprogrammed and then restarted. This saves both time and money for both developer and customers. This software implementation can be done for a Network Processor and are specially designed to handle networking tasks and algorithms such as packet processing.

A network processor is often used as a development tool but it can also be used for debugging and testing. Most of the NPs focus on processing headers, processing the packet contents is an issue for the future

Some of the Network Processor vendors such as Intel, Motorola, and IBM provide a Workbench for a simulator of their Network Processors. A Network Processor simulator is always released before the actual hardware is shipped out. A good benefit is then to start developing software on the simulator, where it easily to debug and optimise using cycleaccurate simulation. If the application works on the simulator, there is compatible to be used in the hardware.

## 2.7.3 Existing hardware solutions

Today, most of the hardware implementations of switches are based on Field Programmable Gate Arrays (FPGAs) for low level processing and General Purpose Processors (GPPs) for higher level processing. Here are some of the existing system implementations:

- General Purpose Processor (GPP), used for general purpose processing such as protocol processing on desktop and laptop computers. They are inefficiently due to the control overhead for each instruction since it must be fetched and decoded, although some of the processors may use very large caches.

- Fixed Function ASIC (Application Specific Integrated Circuit), designed for one protocol only. They work at speeds round OC-12 and OC-48. Their major problem is their lack of flexibility, for example with longer time and cost to implement a change. ASICs are widely used for MAC protocols such as Ethernet. ASICs are expensive to develop therefore they are low cost only for very large sales volume.

- Reduced Instruction Set Computer (RISC) with Optimised Instruction Set [9], is a microprocessor architecture similar to an ASIP except that it is based on adding some instructions to the RISC core instruction set. The program memory is separated from the data memory allowing fetch and executes to occur in the same clock cycle with on stage pipelining. The RISC design generally incorporates a large number of registers to prevent in large amounts of interactions with memory.

- Field Programmable Gate Array (FPGA) [36], is a large array of cells containing configurable logic, memory elements and flip flops. Compared to an ASIC, the FPGA can be reprogrammed at the gate level, where the user can configure interconnection between the logical elements, or configure functions on each element. Therefore, the FPGA has a better flexibility with shorter time-to-market and less design complexity than an ordinary ASIC. However it has still lower performance than an ASIC and higher performance compared to a GPP.

- Application Specific Instruction Processor (ASIP), has instructions that map well to an application. If some pairs of operations appear often, it may be useful to cluster these operations into a single operation. It is specialised for a particular application domain. Normally, it has better flexibility than a FPGA but lower performance than a hardwired ASIC.

In September 2001, Niraj Shah at University of California in Berkeley compared the different system implementations above, using metrics such as flexibility, performance, power consumption, and cost to develop [39]. The results showed a clearly, that using an ASIP would be the best approach for most network system implementations. It provides the right balance of hardware and software to meet all the necessary requirements.

This thesis uses a Network Processor which is basically a reprogrammable hardware architecture concept using the ASIP technology. To gain further information about the different hardware solutions, see [6]. To gain knowledge about flexibility and performance differences between the solutions above, see [39].

#### 2.7.4 Network Processors in general

A Network Processor's main purpose is to receive data, operate on it, and then send out the data on a network at wire speeds (i.e., only limited by the link's speed). They aim to perform most network specific tasks, in order to replace custom ASICs in any networking device.

A NP plays the same role in a network node as the CPU does in a computer. The fundamental operations for packet processing consist of following operations:

- *Classification*, parsing of (bit) fields in the incoming packet and table lookup to identify the incoming packets, followed by a decision based regarding the destination port of the packet.

- Modification of the packet, data fields in the header are modified/updated. Headers

may be added or removed and this usually entails recalculation of CRC or

checksum.

- Queuing and buffering, packets are placed in an appropriate queue for the outgoing port and temporary buffered for later transmission. The packet may be discarded if the capacity would be exceeded.

- *Other operations*, such as security consideration, policing compression, traffic metrics.

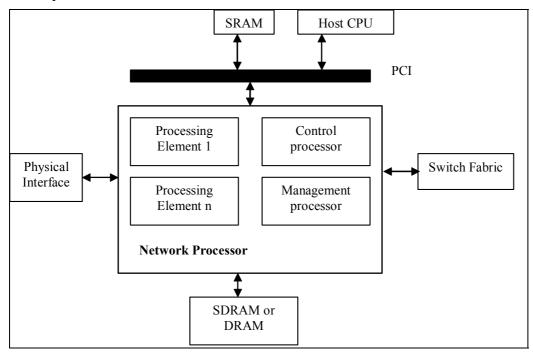

## **Network Processor Composition**

A typical architecture of a Network Processor is shown in Figure 9. One central theme, when creating a Network Processor is employing multiple processors than instead of a large processor. A Network Processors contains of many Processing Elements (PEs), which perform most of the functions such as classification, forwarding, computation and modification, etc.

A Network Processor contains a Management processor, which handles: off-loaded packet processing, loading object code to the Processing Elements, and communicates with host-CPU. A Network Processor can also contain a Control processor, which are specialised for a specific task such as pattern matching, traffic management, and security encryption.

Network Processors interfaces host-CPU through PCI or similar bus interface. They also interfaces SRAM/DRAM/SDRAM memory units to implement lookup tables, and PDU buffer pools.

Figure 9. Typical Network Processor Architecture

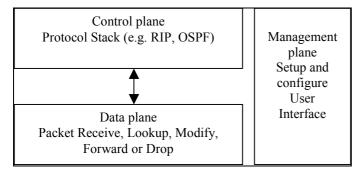

#### Data plane vs. Control Plane

The network processing tasks are divided into two kinds of tasks: Data plane and Control Plane tasks. Data plane tasks handle time-critical duties in the core design. Less time critical tasks that fall outside the core processing or forwarding requirements of a network device are called Control Plane tasks. Another way to distinguish between these to types of tasks is to look at each packet's path. Packets handled by the data plane usually travel through the device, and the packets that are handled by the control plane usually originate or terminate at the device.

## 2.7.5 Fast path and slow path

The data plane and the control plane are processed over a fast path or a slow path depending on the packet. As a packet enters a networking device, it is first examined and processed further on either the fast path or slow path. The fast path (most data plane tasks) is used for minimal or normal processing of packets and the slow path are used for the unusual packets and control plane tasks that needs more complex processing. After processing, packets from both slow and fast path may leave via the same network interface.

#### 2.7.6 Improvements to be done

Today a Network Processor moves packets surprising well, but still the processors can be improved to achieve better performance. An important thing to remember is that all the control of the traffic flowing through a NP should be implemented in software. Otherwise the flexibility is no better than a common ASIC [41]. According to a white paper written by O'Neill [40], today there are three main issues to improve the performances for a NP:

- Deeper pipelines, the relatively infrequent branches and their high degree of predictability can be exploited.

- Higher clock rate, can be reached if more effective using of caching on application is done and this improves the traditional path allowing it to be more effective.

- A multi-issue out-of-order architecture, with larger basic blocks loaded into the system improves the performance.

## 2.8 Network Processor Programming

Today, many network processors only have capacity for a few kilobytes of code. Intel still recommends writing in assembly code until their C-compiler has been further developed. Some NPs use functional languages to produce smaller programs with fewer lines of code. These languages are more complex, but programming effort can be saved.

#### 2.8.1 Assembly & Microcode

Assembly, or microcode, is the native language for a NP. Although microcode for different NPs may look the same, there are huge differences. Each network processor has its own architecture and instruction set. Thus programs for the same purpose are quite different between different NPs. Therefore, the NP industry is heading for a serious problem for the future, how to standardize coding, so programs can be reused in another NP.

## 2.8.2 High-level languages

Most vendors supply code libraries and C-compilers to use for their NP. A code library usually covers basic packet processing code needed for IPv4 forwarding or ATM reassembling. There are significant advantages to use high-level languages such as C instead of microcode:

- C is the most common choice for embedded system and network application developers.

- A high-level language is much more effective at abstracting and hiding details of used instructions

- It is easier and faster to write modular code and maintain it in high-level language with support for data types, such as type checking.

One of the upcoming programming techniques is functional programming where the languages describe the protocol rather than a specific series of operations. For example, Agere Systems NPs (see [33]) are supported with functional languages used for classification.

To read more about Assembly and high-level languages, see [7].

#### 2.8.3 Network Processing Forum (NPF)

There have been steps towards standardized code for general interfaces. In February 2001, almost all Network Processor manufacture companies gathered together to found an organization, called Network Processing Forum (NPF) [50]. NPF establishes common specifications for programmable network elements to reduce time-to-market and instead increase the time-in-market. The desired norm should be rapid product cycles and in-place upgrades to extend the life of existing equipment. This also reduces the manufacturers' design burden, while still providing the flexibility enabled by using their own components to meet the requirements. Since 2001, NPF has grown to almost 100 members around the world.

#### 2.9 Intel IXP2400

#### 2.9.1 Overview

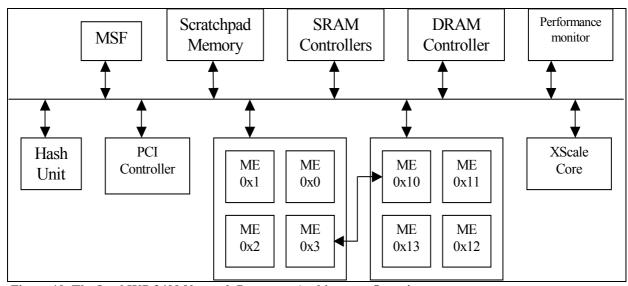

The Intel IXP 2400 chip has eight independent multithreaded 32-bit RISC data engines (microengines). These microengines are used for packet forwarding and traffic management on chip. IXP 2400 consists of these functional units:

- 32-bit XScale processor, used to initialise and manage the chip and for higher layer network processing tasks, and for general purpose processing. It runs at 600 MHz

- 8 Microengines, used for processing data packets on the data plane

- 1 DRAM Controller, used for data buffers

- 2 SRAM Controllers, used for fetching and storing instructions

- Scratchpad Memory, general purpose storage

- Media Switch Fabric Interface (MSF), used by the NP to interface POS-PHY chips, CSIX Switch Fabrics, and other IXP 2400 processors.

- Hash unit, XScale and microengines can use this when hashing is necessary

- PCI Controller, can be used to connect to host processors or PCI devices

- Performance Monitor, counters that count internal hardware events, which can be used to analyse performance

All these functional units are shown in Figure 10.

Figure 10. The Intel IXP 2400 Network Processor Architecture Overview

## 2.9.2 History

On April 1999 Intel Corporation announced that they would release their first Network Processor called Intel IXP 1200. It consisted of one StrongARM processor (predecessor of the XScale), six microengines, and interfaces to SRAM/SDRAM memory, FIFO Bus Interface (FBI), and PCI bus. The StrongARM processor is used for slow path processing, and the six microengines with four threads each handle fast processing. The IXP 1200 was intended for layers 2-4 processing and it supports data rates up to 2.5 Mbps. Today Intel is working on two Network Processors (Intel IXP 2400 and Intel IXP 2800) and a development toolkit called IXA 3.0. These are all still under development, therefore Intel has only a prerelease of the development toolkit, which is available for testing. In this thesis, I am currently using the pre-release 4 of the toolkit. The final release of the toolkit is planned for the first quarter of 2003. Both Network Processors are expected to be shipped sometime late in 2003.

## 2.9.3 Microengine (ME)

In the IXP 2400, there are eight Microengines (sixteen in IXP 2800) in one Network Processor. Each ME has eight threads each providing an execution context. It contains following features:

- 256 32 bits General Purpose Registers

- 512 Transfer Registers

- 128 Next Neighbour Registers

- 640 32-bit words of Local Memory

- 4 K instructions in the Control Store

- 8 Hardware Threads

- Arithmetic Logic Unit

- Event signals

## **General Purpose Registers (GPRs)**

These registers are used for general programming purposes. They are read and written exclusively under program control. When a GPR are used as source operand in a instruction, it supplies operands to the execution datapath.

## **Transfer Registers**

Transfer registers are used for transferring data to/from a Microengine, and to locations external (for example, SRAMs, DRAMs, etc.) to the Microengine.

## **Next Neighbour Registers**

Next Neighbour (NN) registers are used as a source register in an instruction. They are written either by an adjacent Microengine or by the same Microengine. This register can rapidly pass data between two neighbour Microengines using NN ring structure (Same as dispatch loop, see 2.11.2), and when a Microengine write to its own neighbour register, it must wait 5 cycles (or instructions) before it can write new data. The NN registers can also be configured to act as a circular ring instead of addressable registers. The source operands are now popped from the head of the ring and the destination results are pushed to the tail of the ring.

## **Local Memory (LM)**

The Local Memory is an addressable local storage in the Microengine used for read and write exclusively under program control and it can be used as source operand or destination operand for an ALU operation. Each thread on a Microengine has two LM address registers, which are written by special instructions. There is a 3 cycles latency between local memory address allocation and its de-allocate of the same address.

### **Hardware Threads (contexts)**

Each context has its own register set, program counter and controller specific local registers. Using fast context swapping allows another context to do computation while the first context waits for an I/O operation. Each thread (context) can be in one of four different states:

- Inactive, used if applications don't want to use all threads

- Ready, this thread is ready to execute

- Execute, this is the executing state, a thread stays in this state until a instruction causes it to go to next state (Sleep) or a context swap is made

- Sleep, this state the thread waits for external events to occur

When one context is in the executing state, all others must be in another state, since only one context can be in the executing state (as it is a single processor).

#### **Event signals**

The Microengines supports event signalling. These signals can be used to indicate occurrence of some external events such as, when a previous thread goes to a state of "sleeping". Typical use of event signals includes completion of an I/O operation (such as DRAM) and signals from other threads. Each thread has 15 event signals to use, and each signal can be allocated and scheduled by the compiler in the same manner as a register and allows a large number of outstanding events. For example, a thread can start an I/O to read packet data from a receive buffer, start another I/O to allocate buffer from a free list, and start a third I/O to read next task from a scratch ring. These three I/O operations can be executed in parallel using threads with signalling.

Many microprocessors schedules multiple outstanding I/Os, normally handled by the hardware. By using event signals, the Microengine places much of the burden on the compiler instead of hardware. This simplifies the hardware architecture of a processor.

#### 2.9.4 DRAM

The IXP2400 have one channel of industry standard DDR DRAM running at 100/150 Mhz providing 19.2 Gb/s of peak DRAM bandwidth. It supports up to 2 Gb of DRAM and is primary used to incoming buffer packets. All DRAM memory is spread out on four memory banks, where the DRAM addresses are interleaved and different operations on DRAM can be performed concurrently. There is no DRAM used in IXP1200 network processor, instead it uses SDRAM.

#### 2.9.5 SRAM

The IXP 2400 provides two channels of industry standard QDR SRAM running at 100-250 MHz providing 12.8 Gb/s of read/write bandwidth and a peak bandwidth of 2.0 Gbytes/sec per channel. These two channels can use up to 64 MB of SRAM memory per channel. The SRAM is primary used for packet descriptors, queue descriptors, counters, and other data structures. In the SRAM controller, access ordering is guaranteed only for read coming after write.

#### 2.9.6 CAM

Many of the network designers are discovering that the fastest and easiest way to process a packet is to offload the packet classification function to a co-processor. One of the best co-processors today is Content Addressable Memory (CAM) [10] [45]. CAM is a memory device to accelerate applications that requires fast searches of database, list, or pattern in communication networks. It improves a usage of multiple threads on same data and the result can be used to dispatch to the proper code. It performs a parallel look-up on 16 entries of 32-bit value. This allows a source operand to be compared against 16 values in a single instruction. All entries are compared in parallel giving a result of the loopback written into the destination register. It reports one of two outcomes: a hit or a miss. A hit indicates that the lookup was found in CAM. The result also contains the entry number that holds the lookup value. A miss indicates that the lookup value was not found in CAM. The result also contains the entry of the Least Recently Used (LRU) entry, which holds can be suggested to use as a replace entry.

## 2.9.7 Media Switch Fabric (MSF)

The MSF is used to connect an IXP 2400 processor to a physical layer device and/or to a switch fabric. It contains of separate receive and transmit interfaces. Each of these interfaces can be configured for UTOPIA (Level 1, 2, and 3), POS-PHY (Level 2 and 3) or CSIX protocols. UTOPIA [37] is standardized data path between the physical layer and the ATM layer. The ATM Forum defines three different levels of UTOPIA. Common Switch Interface for Fabric Independence and Scalable Switching (CSIX) [38] is a detailed interface specification between port/processing element logic and interconnect fabric logic. The IXP 2400 Microengines communicated with the MSF with the Receive Buffer (RBUF) or the Transmit Buffer (TBUF). RBUF is a RAM memory used to store received data from the MSF in sub-blocks referred as elements. The RBUF contains a total of 8 KB data and it is possible to divide it into 64, 128, or 256 byte elements. For each RBUF element there exist a 64-bit receive status word to describe the contents and status of the contents of the receive element. Content status such as a byte counts for a packet, or a flag to indicate if the received packet is the beginning or end of a packet. TBUF acts the same way as RBUF, except that it stores data to be transmitted instead of receiving data and it is divided in TBUF elements. A TBUF element is associated with a 64-bit control word used to store: packet information such as, payload length, flag indication if it is the beginning or end of a packet.

Looking at IXP1200 network processor, there is no MSF used, instead it uses a FIFO Bus Interface (FBI) unit. The FBI contains receive and transmit buffers (RFIFO and TFIFO), scratchpad RAM, and a hash unit.

#### 2.9.8 StrongARM Core Microprocessor

The StrongARM core is a general-purpose 32-bit RISC processor. XScale and StrongARM are compatible with the ARM instruction set, but only implement the ARM integer instruction set, thus do not provide floating-point instruction support.

The XScale core supports VxWorks (v.5.4), and embedded Linux (kernel v.2.4) as an operating system to control the Microengine threads. Each microengine contains a set of control and status registers. These registers are used by the StrongARM core to program, control, and debug the Microengines. The XScale has uniform access to all system resources, so it can effectively communicate with the Microengine through data structures in shared memory.

## 2.10 Intel's Developer Workbench (IXA SDK 3.0)

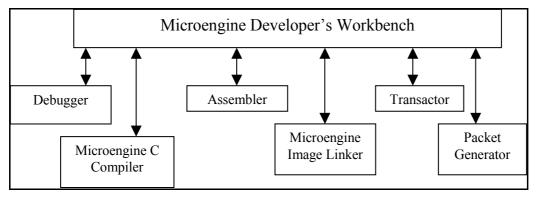

To program the Intel Network Processor IXP2400, Intel has developed a workbench/transactor called Intel IXA SDK 3.0 (see Figure 11) used for assembling, compiling, linking, and debugging microcode that runs on the NPs Microengines [31]. The workbench is graphical user interface tool running on Windows NT and Windows 2000 platforms. The workbench can be run either from the development environment or as a command line application. The microengine development environment has some important tools such as:

- Assembler, used to assemble source files

- Intel Microengine C Compiler, generates microcode images

- *Linker*, links microcode images generated by the compiler or assembler to produce an object file

- *Debugger*, used for debug microcode in simulation mode or in hardware mode. (Hardware mode is not supported in the pre-release versions)

- *Transactor*, when debugging, the transactor provides debugging support for the Developers workbench. The transactor executes the object files built by the linker to show the functionality, statistics for Microengines, behaviour and performance characteristics of a system design based on the IXP2400.

Figure 11. Overview of Intel IXA SDK 3.0 workbench

In this development toolkit, three data plane libraries are available. First, it has a Hardware Abstraction Library (HAL). This library provides operating system-like abstraction of hardware assistant functions such as memory and buffer management, and critical section management. The second library contains Utilities to provide range of data structures and algorithm support, such as: generic table lookups, byte field handling and endian swaps. The third library is a Protocol Library, used to provide an interface supporting link layer and network layer protocols through combinations of structures and functions.

IXA SDK 3.0 also includes other functionalities such as:

- *Execution History*, this show execution coverage on all thread in each used Microengine.

- *Statistics*, this shows statistics data from threads, Microengines, SRAM controllers, DRAM controller, and more. For example it can show how much time a certain Microengine has been executing or being idle.

- Media bus device and network traffic simulator

• Command line interface for the network processor simulators, this enables a user to specify options for commands to execute in a certain way.

#### 2.10.1 Assembler

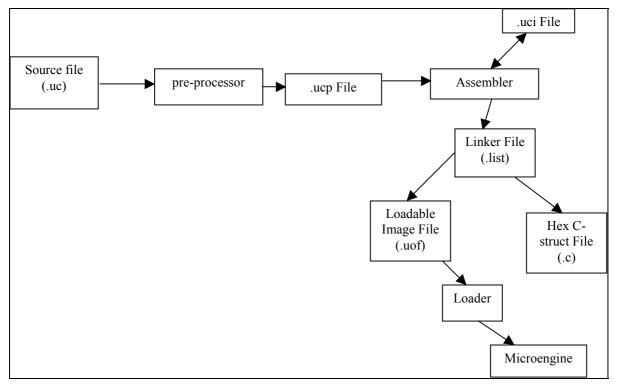

The Assembler is a fully compliant superset of a processor manufacturer's recommended Assembly Language. The Assembler recognizes conditional assembly directives which can be used to efficiently tail or code to multiple execution environments. One way to implement assembly language code is to use Macros. Macros (#macro, #endm, etc.) are a series of directives and instructions grouped together as a single command. Optional parameters can be passed to the macro for processing. To write macros is useful when writing in modular and readable code.

The assembler has a built-in facility implementing parameter substitution by a variable number of arguments and, as an extension to the language, allows the omission of any argument. Macros and repeat blocks may be nested. Macro constructs may contain local labels and the scope of these labels is selected through a command-line option.

The assembler has functionalities included such as:

- Processes directives flow can be seen in Figure 12 below

- Performs macro inline expansion

- Processes loop, conditional expressions

- Low-level syntax check

- Assign symbolic variables to GPRs, Xfer Register, signals

- Branch optimisation

Before an assembly process begins, a source file (.uc) needs to be created. This file contains three types of elements:

- Instructions, consists of opcode and arguments generate microwords in the ".list"- file

- Directives, it passes information either to the pre-processor, assembler, or to the downstream components (such as linker).

- Comments, used for have a clean code to understand

The pre-processor is automatically invoked by the assembler to transform to a program before the actual assembling. The pre-processor provides these operations:

- *Inclusion of files*, these files can be substituted into the main code.

- *Macro expansion*, the pre-processor replaces instants of macros with their definitions.

- *Conditional compilation*, it enables including or excluding code based on various conditions.

- *Line control*, used to inform the assembler of where each source file came from.

- *Structured assembly*, it organises the control flow of ME instructions into structured blocks.

- *Token replacement*, it causes instances of an identifier to be replaced with a token string.

Figure 12. Assembly flow

The pre-processor takes the source file and creates an ".ucp"-file for the assembler. Now, the assembler takes this file and creates intermediate file with the filename extension of ".uci". The .uci file is used by the assembler to create the ".list"- file and provides error information, used for debugging. To convert an ".uc"-file to a ".list"-file, it process following functions:

- Checks instruction restriction

- Resolves symbol names to physical locations

- Optimises the code, by inserting defer[] optional tokens

- Resolves label addresses

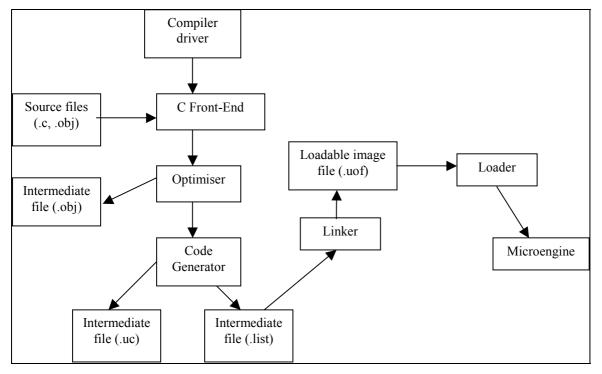

#### 2.10.2 Microengine C compiler

Intel's Microengine C compiler provides high-level language through C and it is specially optimised for the network processors IXP2400 and IXP2800. Some of the special features for these NPs are:

- The compiler allows the programmer to specify which variables must be stored in registers and which may be stored in memory.

- The compiler allows the programmer to specify which type of memory (SRAM, DRAM) to be used to allocate a specific variable.