# AN ABSTRACT MACHINE BASED EXECUTION MODEL FOR COMPUTER ARCHITECTURE DESIGN AND EFFICIENT IMPLEMENTATION OF LOGIC PROGRAMS IN PARALLEL

Manuel V. Hermenegildo

Department of Computer Sciences The University of Texas at Austin Austin, Texas 78712-1188

TR-86-20 August 1986

Copyright © 1986 Manuel V. Hermenegildo

# AN ABSTRACT MACHINE BASED EXECUTION MODEL FOR COMPUTER ARCHITECTURE DESIGN AND EFFICIENT IMPLEMENTATION OF LOGIC PROGRAMS IN PARALLEL

by

MANUEL V. HERMENEGILDO, E.E., M.S.

# DISSERTATION

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY

THE UNIVERSITY OF TEXAS AT AUSTIN

August, 1986

Copyright

by

Manuel V. Hermenegildo

1986

### ACKNOWLEDGEMENTS

I would first like to thank my advisor, Professor G. J. Lipovski, for his continuous support and guidance. He brought the subject to my attention and has always made himself available for discussion and advice. I would also like to thank the members of the Committee, Professors J. C. Browne, J. K. Aggarwal, C. K. Leung, and R. M. Jenevein, for their helpful observations, interest and encouragement, and for the time devoted to the reading of this document.

I am also indebted to Richard Warren and Roger Nasr for many hours of interesting discussion and for their friendship. Richard Warren's implementation of the model described in this document was very useful in proving its viability and in providing performance data. I am grateful to all the other members of the MCC Parallel Processing and Artificial Intelligence groups for their encouragement and to Steve Lundstrom (MCC) and the Fulbright Foundation for their support.

Special thanks to Professor David H. D. Warren for many interesting discussions, for his perceptive comments and suggestions, and for his hospitality. He has been a continuous source of encouragement and inspiration for me.

Finally I would like to thank the many friends who have helped me and encouraged me during these years at The University of Texas. I am very specially indebted to Ian Walker, Pat Cericola, and Evan Tick for their patience in wading through so many earlier drafts of this document and, most importantly, for their invaluable friendship.

Manuel V. Hermenegildo

The University of Texas at Austin August, 1986

# PREFACE

"Sorry to interrupt the festivities", said HAL, "but we have a problem." Arthur C. Clarke; 2001, A Space Odyssey

# A Word for the Non-Initiated

Scientific reports have an unmistakable tendency to be of a very detailed nature and limited scope. This is largely a consequence of the fact that as our knowledge is broadened we only seem to further unveil reality's inherent complexity. It is in order to confront this complexity that scientific research has moved more and more towards superspecialization. However, even though superspecialization seems to be here to stay, the activities of the researcher are hard to justify unless they are motivated (secretly or openly) by some higher-level goal. Of course, such higher level goals often appear obvious to most researchers in their respective fields (in the case in hand, those of Computer Engineering and Computer Science). Computer Scientists and Engineers are therefore urged at this point to skip the rest of this preface and jump with the author into the first chapter. This preface is not intended for them. Instead, it will attempt to offer the "uninitiated" reader in the mysteries of computers, declarative languages and parallelism, both a simple introduction to the subjects treated in the rest of this document and, hopefully, some justification as to why it may make sense to explore these subjects at all.

# Computers Need to be Faster and Easier to Use

It is perhaps the fact that computers offer promise to one day mimic at least some of the simpler functions of the human mind (itself undoubtedly one of the most

intriguing "mechanisms" with which we are confronted) that has always drawn our attention towards them. However, computer research is, as so many areas of science and engineering, still far from its most idealistic goals, and, in particular, from that of achieving any kind of "intelligent" behavior from an automaton. Research in "Artificial Intelligence" is faced today with a number of limitations. Firstly, we still lack a clear understanding of how such behavior could be obtained from a machine. Secondly, we do not know how to build computers that are fast enough that they could provide responses according to that behavior in a reasonable amount of time, and which are at the same time easy enough to use that the associated programming tasks would represent feasible endeavors.

The first of the problems mentioned above is one of the many subjects of artificial intelligence research. Instead, and as the subject of this dissertation, we will be interested in addressing the second of those limitations, i.e. providing computers that are at the same time more powerful, and friendlier to the user. Fortunately enough, we do not need to resort to any futuristic quest for intelligence to understand the usefulness of such an endeavor: we already need faster, easier to use machines today, not only for the advancement of artificial intelligence, but also in most other current computer application areas.

#### 1.- Making Computers Easier to Use

Let us consider the issue of making machines easier to use first<sup>1</sup>. At our (relatively modest) current state of development in human interaction with computers, our main means for instructing them what to do is by writing a program, i.e. a list of instructions which are to be executed by it. These instructions are expressed in a particular language that the computer can understand: a programming language.

Conventional programming languages generally express these instructions as a series of precise "actions" that are to be performed by the computer one after the

<sup>&</sup>lt;sup>1</sup>We will treat the issue of computational power in the next section.

other<sup>2</sup>. This is known as an *imperative* style, a program being a sequence of commands or statements. Programs today come in this format largely as a consequence of the fact that the first computers were no more than the equivalent of one of today's hand-held calculators and that early programs were just sequences of the basic instructions that a particular machine could directly execute<sup>3</sup>. Programming languages then emerged as a tool for making it it easier for a human being to express the actions required from the computer. However, it is a fact that computers already existed in a particular form before these languages were designed, and this undoubtedly invited a "machine-oriented" style in these designs which still lingers in today's programming languages. These languages are often so apart from the natural way in which humans think and express themselves that programming a computer is frequently a difficult and error-prone task for any sizeable problem.

The question of course is, can we design a computer language which is free

This would be expressed in less verbose terms (in a conventional programming language) more or less as follows:

```

Number = 0;

loop: Square = Number * Number;

print( Number );

Number = Number + 1;

goto loop:

```

<sup>3</sup>For example, for an actual hand-held calculator a "program" for adding "4" and "3" would be:

```

press 3

press +

press 4

press =

```

<sup>&</sup>lt;sup>2</sup>For example, suppose that we want to program the computer to simply generate the squares of all positive integers. One way of doing this is by specifying the *actions* that may be involved in obtaining such a list:

<sup>1.</sup> Start with the number 0,

<sup>2.</sup> find the square of the number by multiplying it by itself,

<sup>3.</sup> print the square,

<sup>4.</sup> compute the next number by adding 1 to the previous number,

<sup>5.</sup> go to step 2.

from the *imperative* style? If we avoid any machine oriented considerations, the first language to come to mind is, of course, the human natural language: the user's mother tongue. Such a language though presents a number of serious drawbacks. These drawbacks include its verboseness, only made worse by its vagueness and ambiguity if not provided with a suitable context or a great deal of (normally assumed) knowledge. This fact was already realized by mathematicians long before computers came to being and they devised "Logic" as a means of clarifying and/or formalizing the human thought process. Logic lets us express facts and rules about the world in a precise and concise way and draw conclusions from them which can be formally proven to be correct. Thus, Logic would tells us, for example, that the assumptions

Aristotle makes cookies, and

Plato is a friend of anyone who makes cookies.

imply the conclusion

Plato is a friend of Aristotle.

Symbolic logic is simply a shorthand for expressing conventional Logic: if we agree that  $\mathbf{makes}(\mathbf{X}, \mathbf{cookies})$  means "X makes cookies",  $\forall$  X means "for all X", X  $\rightarrow$  Y means "if X then Y", and  $\mathbf{friend}(\mathbf{X},\mathbf{Y})$  means "X is a friend of Y", then the example above can be expressed in symbolic logic as

makes(Aristotle, cookies)

$\forall X, makes(X, cookies) \rightarrow friend(Plato, X)$

and the conclusion as

friend(Plato, Aristotle)

Clearly, one can mechanically translate from Symbolic Logic to natural language by using a "conversion table" for the symbols like the one provided above.

It is this ability of symbolic logic to express knowledge in a way that is very precise and compact, while at the same time close to the natural way in which humans express themselves that led to the concept of using Logic as a means for

Kowalski [39] not many years ago and has since received wide acceptance as one of the most promising programming paradigms for future computers<sup>4</sup>. Logic provides more concreteness than a natural language, but it is also far less machine oriented than conventional computer languages. The main difference with them is its "declarative" nature: in logic, statements express facts, knowledge about the problem to be solved, rather than precise instructions to be followed step by step<sup>5</sup>.

• 0 is a positive integer.

Now let us define "square":

• Y is the square of X if it is the same as the result of multiplying X by itself.

Note that these statements provide our *knowledge* about the problem, rather than a sequence of instructions to be followed step by step. This is much closer to the way things are explained to humans. Just for reference, here is the listing of the same program written in Prolog [58] (a practical, though still far from perfect, "logic programming" language):

```

pos_integer(0).

pos_integer(X) IF pos_integer(Y) AND X=Y+1.

square(Y, X) IF Y=X*X.

```

Now we can ask the Prolog system for the squares of all positive integers:

```

pos_integer(X) AND square(Y, X)?

and Prolog will try to find them. One of the interesting things that we also can do now is ask

other types of questions. For example, the answer to

```

```

square(Y, 4)? is "Y=16". Surprisingly enough, the answer to

```

pos\_integer(X) AND square(4, X)?

is "X=2": the same program can be used (even though only in limited cases) to find square

roots!

<sup>&</sup>lt;sup>4</sup>For example, Logic Programing is the language of choice in the Japanese Fifth Generation Computer Project.

<sup>&</sup>lt;sup>5</sup>A "declarative" description of the problem proposed previously would be the following. First, let us *define* the positive integers:

<sup>•</sup> X is (also) a positive integer if it is the result of adding 1 to another positive integer Y.

Logic is (with functional languages) part of the reduced class of **declarative** languages. It is hoped that the advantages that these languages offer over conventional ones will make computer programming an easier and less prone to error job. It was mentioned how this was one of our objectives. In this dissertation Logic (and, to some extent, functional languages) is chosen as a convenient programming paradigm for new, easier to use computers.

### 2.- Making Computers Faster

From the early days of computing, the quest for faster machines has been one of the driving forces of computer engineering research. The availability of the computer made it possible to create applications that were unimaginable before its birth. These applications in turn suggested others which were more and more demanding on computer power, thus producing a snowball effect which today seems to put no end on the demands for computer speed and power.

There are many ways in which a particular machine can be enhanced, but there are always physical limits to the speed at which a given machine can operate: the speed of light and the size of the computer dictate the ultimate limitation, the time involved in moving information from one part of the machine to the other. But even before the limits of a given technology are reached, there is also the question of cost-effectiveness: a point is eventually arrived at in which a moderate increase in performance demands an enormous increase in cost. A concept which can offer a cost-effective increase in performance which can go beyond the limits of sequential systems is parallelism: the subdivision of a problem into subtasks which can be executed simultaneously by different agents.

Parallelism is not a concept particular to computers: it is a constant in nature and in the organization of human societies. For example, if a company having only one engineer needs to have a project finished by a given date but the engineer estimates that it will be impossible to complete the project in the given time, the obvious solution (short of firing the engineer, of course) is to hire *more* engineers to work on the project simultaneously and cooperatively so that it can be finished in

time<sup>6</sup>. Such a basic everyday idea can also be applied to computers: if one computer cannot perform a given task in a certain amount of time, a number of computers can be set to work on the task simultaneously.

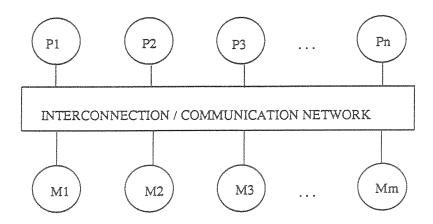

Current parallel computers consist of a number of processors (each of them more or less a complete computer in itself) linked by some kind of interconnection network which makes it possible for information to be interchanged between them (much in the same way as telephone lines -or simply the human speechare used by the engineers of the example above). Another typical organization is to provide all processors with common access to the information they are all working on (a Shared Memory). This is equivalent to having all the engineers (again in the example above) work on the same set of diagrams simultaneously.

If the task in hand can be separated into relatively independent parts, parallelism can be a simple matter. If the parts of the task are more interrelated, efficiently coordinating the actions of the different processors involved will be a more complicated issue, since there will have to be substantial communication between them in order to inform each other of their current results. This is similar to the periodic meetings that engineers working on a project need to have in order to keep the project well coordinated. The overhead involved in this communication is an important factor to take into account: it is clear that two engineers will probably not solve the problem in half the time because of the time lost interchanging results (or, if they are working on the same set of diagrams, waiting for the other to finish working with the particular sheet needed). These considerations will be of the utmost importance in the design of parallel computers.

Despite the problems involved, parallelism offers an enormous potential in high-performance, cost-effective computer design and is already a reality in the form of many commercial products. Parallelism will also be one of the central subjects of this document.

<sup>&</sup>lt;sup>6</sup>The human brain is another notable example of parallelism: it is built out of a multitude of relatively slow elements, but the whole system has an unequaled information storage and processing power.

# Executing Logic Programs in Parallel

In consequence with the considerations presented in the previous sections, this dissertation deals with both the ideas of parallelism and logic programming. It will try to provide guidelines in the design of computers that can execute programs which are easier to create (because they are written declaratively, using "Logic"), and which are fast enough (because they use parallelism extensively) to cope with truly demanding applications. Although we still are far from our ultimate goals, these new computers could represent an important step in our quest for intelligence. In the meantime, they will provide a friendly and powerful tool to help us cope with our current applications and everyday duties. Let me leave you with this idea for now. I need to go and chat with HAL [1], and thank him for so much inspiration.

#### ABSTRACT

The term "Logic Programming" refers to a variety of computer languages and execution models which are based on the traditional concept of Symbolic Logic. The expressive power of these languages offers promise to be of great assistance in facing the programming challenges of present and future symbolic processing applications in Artificial Intelligence, Knowledge-based systems, and many other areas of computing. The sequential execution speed of logic programs has been greatly improved since the advent of the first interpreters. However, higher inference speeds are still required in order to meet the demands of applications such as those contemplated for next generation computer systems. The execution of logic programs in parallel is currently considered a promising strategy for attaining such inference speeds. Logic Programming in turn appears as a suitable programming paradigm for parallel architectures because of the many opportunities for parallel execution present in the implementation of logic programs.

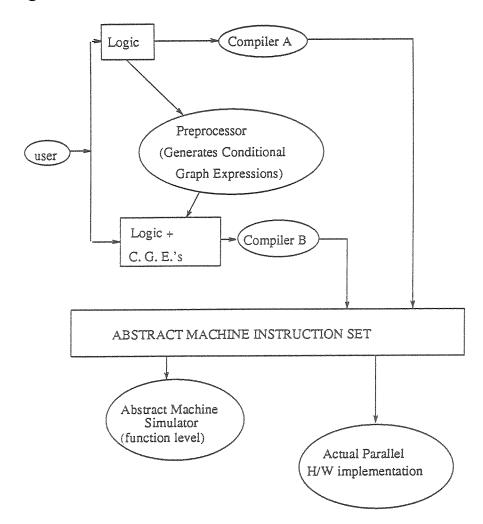

This dissertation presents an efficient parallel execution model for logic programs. The model is described from the source language level down to an "Abstract Machine" level suitable for direct implementation on existing parallel systems or for the design of special purpose parallel architectures. Few assumptions are made at the source language level and therefore the techniques developed and the general Abstract Machine design are applicable to a variety of logic (and also functional) languages. These techniques offer efficient solutions to several areas of parallel Logic Programming implementation previously considered problematic or a source of considerable overhead, such as the detection and handling of variable binding conflicts in AND-Parallelism, the specification of control and management of the execution tree, the treatment of distributed backtracking, and goal scheduling and memory management issues, etc.

A parallel Abstract Machine design is offered, specifying data areas, operation, and a suitable instruction set. This design is based on extending to a parallel environment the techniques introduced by the Warren Abstract Machine, which have already made very fast and space efficient sequential systems a reality. Therefore, the model herein presented is capable of retaining sequential execution speed similar to that of high performance sequential systems, while extracting additional gains in speed by efficiently implementing parallel execution. These claims are supported by simulations of the Abstract Machine on sample programs.

# TABLE OF CONTENTS

| Acknowledgements                                      |     |

|-------------------------------------------------------|-----|

| Preface                                               | vi  |

| Abstract                                              | xiv |

| Table of Contents                                     | xv  |

| Chapter 1. Introduction                               | 1   |

| 1.1. Computers Today and Tomorrow                     | 1   |

| 1.1.1. The Top-Down Approach to Computer Architecture | 2   |

| 1.1.2. Improving Programming Environments             | 5   |

| 1.1.2.1. Procedural vs. Declarative Languages         | 5   |

| 1.1.2.2. Logic Programming                            | 7   |

| 1.1.2.3. Logic and Control                            | 9   |

| 1.1.3. Improving Computer Power vs. Cost              | 10  |

| 1.1.4. Parallelism, Logic Programming, and Synergy    | 12  |

| 1.2. The Dissertation                                 | 14  |

| 1.2.1. Research Approach                              | 15  |

| 1.2.2. Purpose of the Dissertation                    | 19  |

| 1.2.3. Contributions                                  | 20  |

| 1.2.4. Dissertation Outline                           | 21  |

| Chapter 2. Logic Programming                          | 23  |

| 2.1. Logic                                            | 23  |

| 2.1.1. Clausal Form                                   | 24  |

| 2.1.2. Resolution                                     | 27  |

| 2.1.3. Horn Clauses                                   | 32  |

| 2.2. Logic as a Programming Language                  | 32  |

| 2.2.1. Syntax of Horn Clause Programs                 | 33  |

| 2.2.2. Declarative Semantics                          | 34  |

| 2.2.3. Procedural Semantics                           | 35  |

| 2.2.4. Non-Determinism and the Control Strategy       | 36  |

| 2.2.5. The AND/OR Tree Representation of the Search Space   | 38 |

|-------------------------------------------------------------|----|

| 2.2.6. The Logical Variable                                 | 39 |

| 2.2.7. Transparent Control                                  | 40 |

| 2.2.8. Prolog                                               | 41 |

| 2.3. Chapter Summary                                        | 48 |

| Chapter 3. Parallelism and Logic Programs                   | 49 |

| 3.1. Parallelism in Logic Programs                          | 49 |

| 3.1.1. Sources of Parallelism                               | 50 |

| 3.1.2. An Example Showing Different Types of Parallelism    | 51 |

| 3.2. Logic Programs and Parallelism in Practice             | 55 |

| 3.3. Pure OR-Parallelism                                    | 57 |

| 3.4. AND-Parallelism                                        | 58 |

| 3.4.1. All Solutions AND-Parallelism                        | 58 |

| 3.4.2. Variable Binding Conflicts in AND-Parallelism        | 60 |

| 3.4.2.1. Dealing with Variable Binding Conflicts            | 62 |

| 3.4.2.2. Detecting Variable Binding Conflicts               | 63 |

| 3.4.3. Proposed Systems Supporting AND-Parallelism          | 65 |

| 3.4.3.1. Committed Choice Systems                           | 65 |

| 3.4.3.2. Conery's AND/OR process model                      | 66 |

| 3.4.3.3. Static Data Dependency Analysis                    | 67 |

| 3.4.3.4. Restricted AND-Parallelism                         | 68 |

| 3.5. Chapter Summary: A Proposed Approach to Parallel       |    |

| Logic Programming Implementation                            | 71 |

| Chapter 4. A High-Level Execution Model for                 |    |

| AND-Parallelism:                                            |    |

| Procedural Semantics                                        | 74 |

| 4.1. A General Model for AND-Parallelism: Goal Independence | 75 |

| 4.1.1. Conditional Graph Expressions                        | 77 |

| 4.1.2. Forward Execution                                    | 78 |

| 4.1.3. Backward Execution                                   | 81 |

| 4.1.3.1. Backtracking Cases                                 | 82 |

| 4.1.3.2. Determinate Execution                              | 85 |

| 4.1.3.3. A General Algorithm                                | 88 |

| 4.1.3.4. Point Backtracking vs. Streak Backtracking         | 90 |

| 4.1.4. Correctness of Conditional Graph Expressions         | 91 |

| 4.2. Programmer's View of the RAP System                    | 94 |

| 4.3. Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 97    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Chapter 5. A High-Level Execution Model for AND-Parallelism:  Mamory Management and Cool Schoduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 98    |

| Memory Management and Goal Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30    |

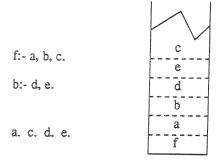

| 5.1. A Simplified Model of Logic Programming Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 99    |

| 5.2. Towards Parallelism                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101   |

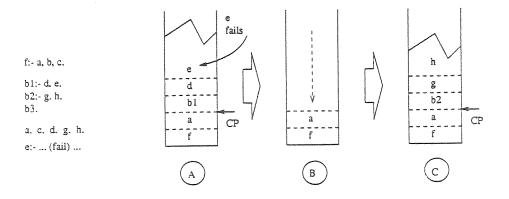

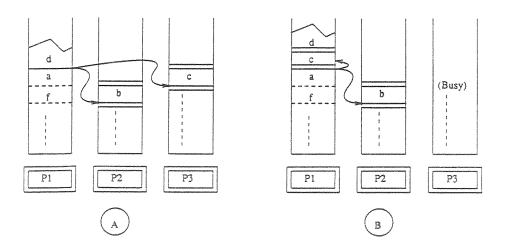

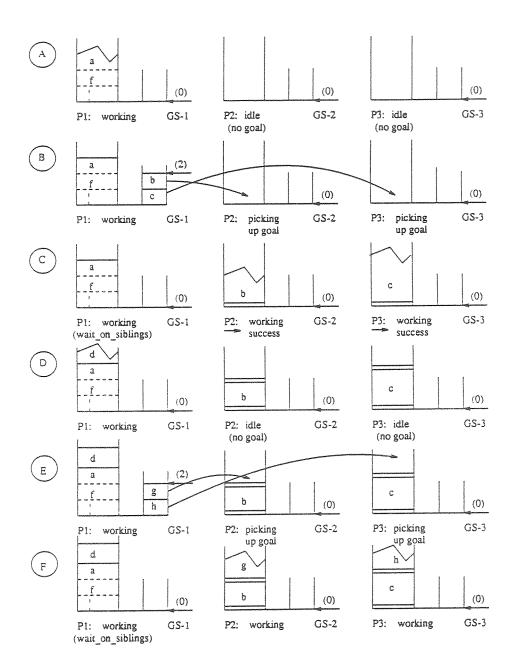

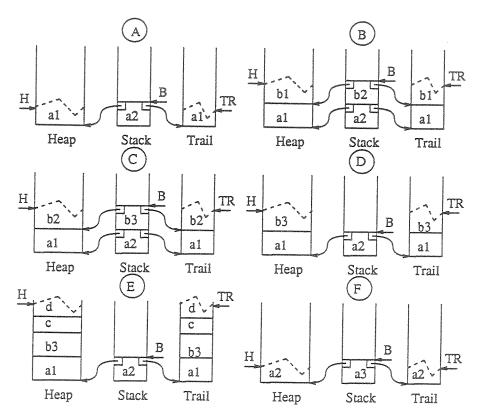

| 5.2.1. A Simple, Distributed Stack Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 102   |

| 5.2.2. A Simple Goal Scheduling Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105   |

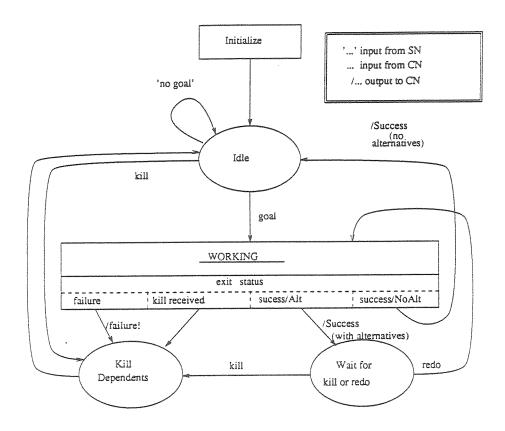

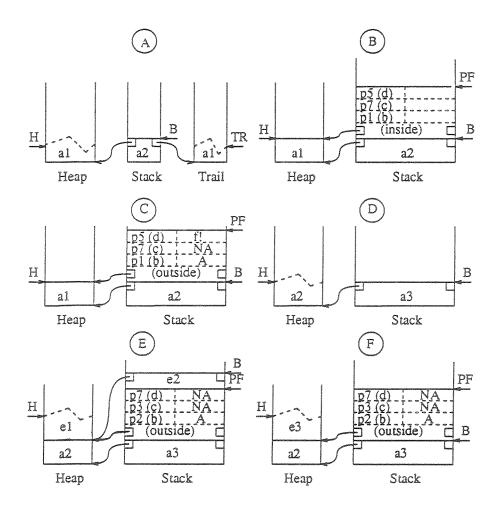

| 5.2.3. A More Efficient Goal Scheduling Strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108   |

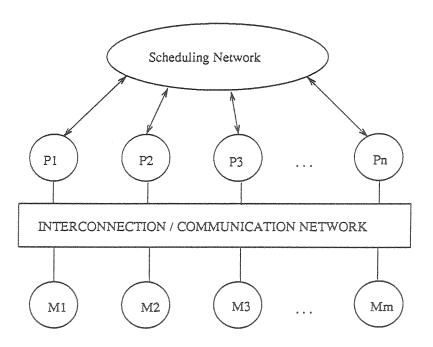

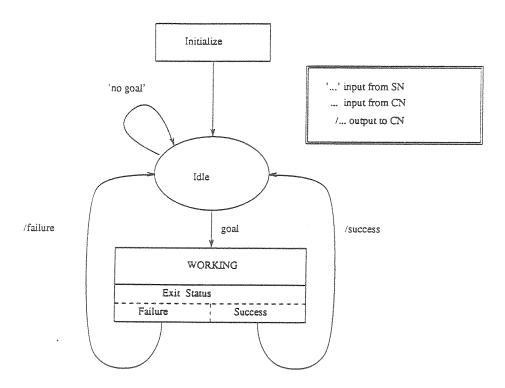

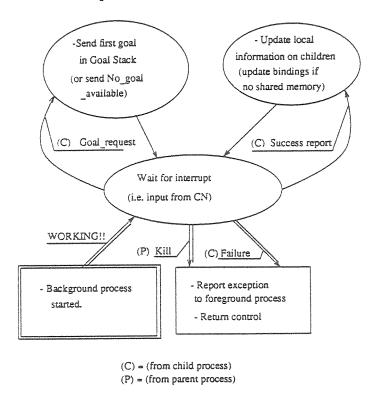

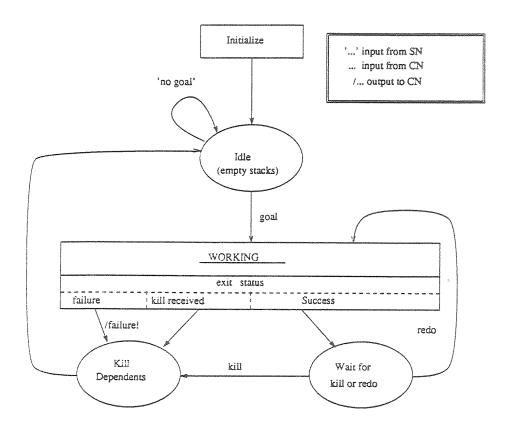

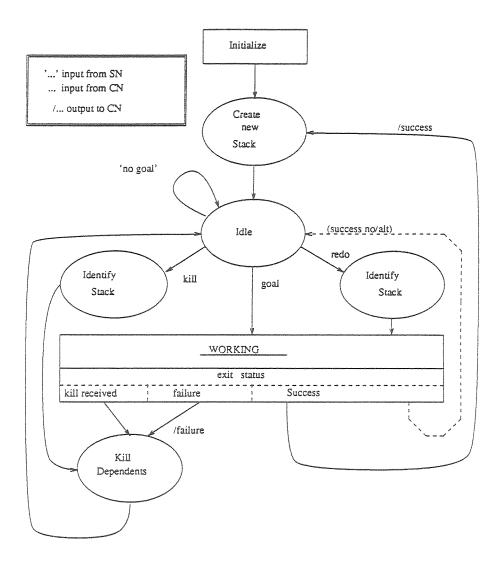

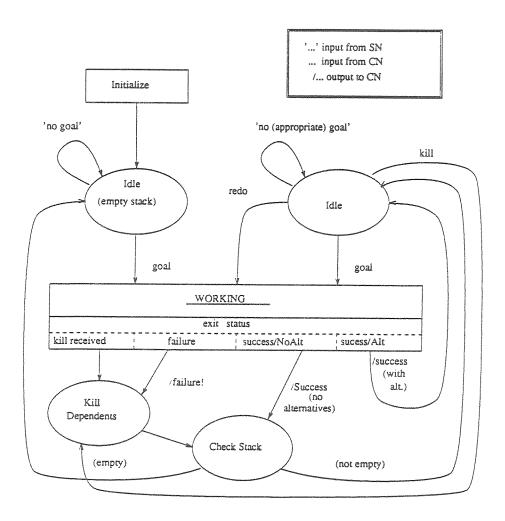

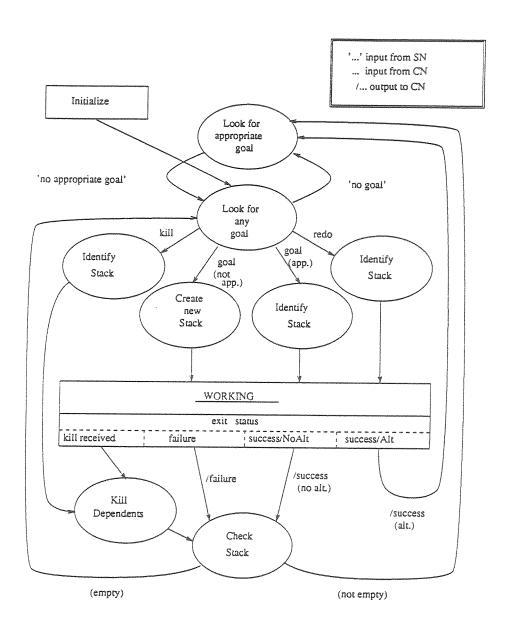

| 5.2.4. A Simple Processor State Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7 1 1 |

| 5.3. Memory Management and Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 114   |

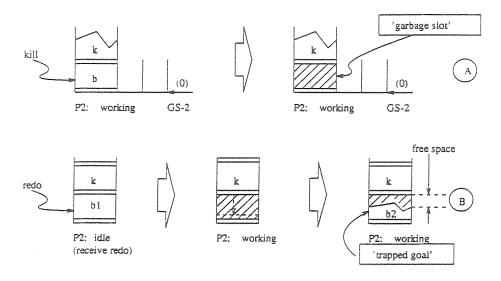

| 5.3.1. Memory Management Problems Associated with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |

| Distributed Backtracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 117   |

| 5.3.2. The Idle Processor Solution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 120   |

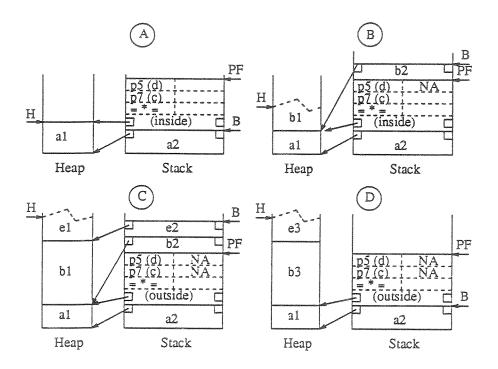

| 5.3.3. The Idle Processor Solution - Some Improvement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 123   |

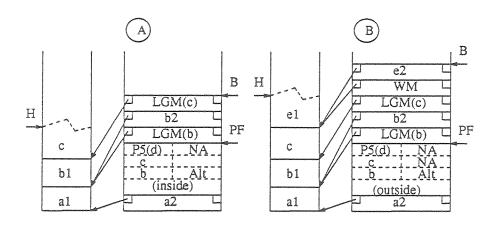

| 5.3.4. Multi Stack Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125   |

| 5.3.5. Goal Restriction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 128   |

| 5.3.6. A Combined Approach                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 131   |

| 5.4. Chapter Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 133   |

| Chapter 6. Implementing Distributed Backtracking at the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

| Abstract Machine Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 135   |

| 6.1. Implementing Sequential Logic at the Abstract Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| Level: The WAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 136   |

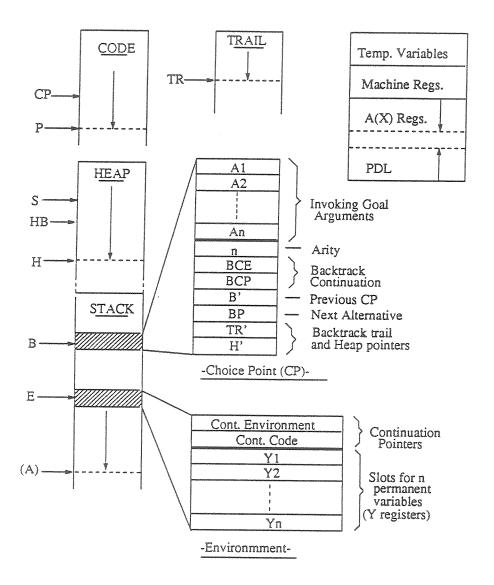

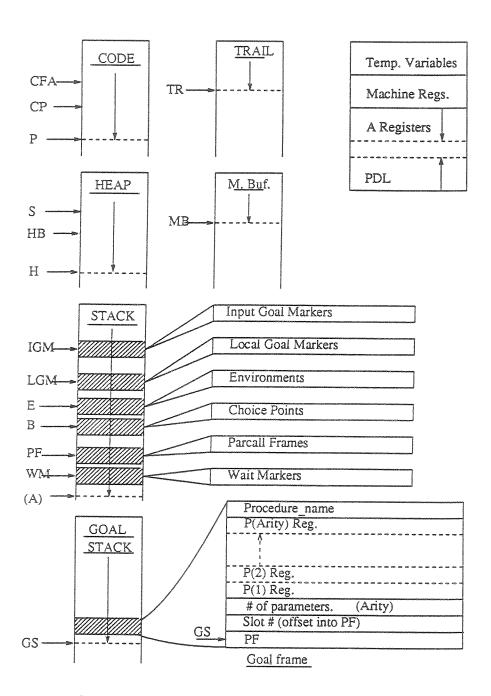

| 6.1.1. Data Areas and General Operation of the WAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 136   |

| 6.1.2. Backtracking in the WAM Revisited                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 140   |

| 6.2. Implementing Distributed Backtracking in AND-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2.20  |