# Comparative study for delay & power dissipation of CMOS Inverter in UDSM range

Jagannath Samanta, Bishnu Prasad De, Banibrata Bag, Raj Kumar Maity

Abstract— Delay and power are two major issues in design and synthesis of VLSI circuits which depends on different design parameters. In this paper, the relative study of propagation delay and power consumption of UDSM CMOS inverter is found considering the channel length below 100nm. The simulation results are taken for different technology (32nm, 45nm, 65nm and 90nm) with the help of Tanner (T-spice) simulation tool. The values of model parameters are used from current Berkeley Predictive Technology Model (PTM). Also the results are analyzed by varying load capacitance, supply voltage & transistor widths.

Index Terms— UDSM, T-Spice, BPTM, Delay, Power dissipation, PDP, CMOS Inverter.

# I. INTRODUCTION:

MOSFETs are continuously scaled to smaller dimensions to reduce the space complexity. UDSM (Ultra Deep Sub-Micron) Technology deals with MOS devices with channel length in the order of 0.25 µm to 0.022 µm or even less. The integration of nanostructures at room temperature smaller than 10nm is far too sensitive to size variations of even a few atomic widths [1]. Propagation delay and power dissipation are two major roles for design & synthesis of any VLSI circuits in this range. There are different secondary effects like Body Bias effect, Channel Length Modulation Effect (CLM), Velocity Saturation

## Manuscript received December 09, 2011.

**Jagannath Samanta,** Electronics & Communication Engineering, Haldia Institute of Technology, Haldia, West Bengal, India (e-mail: jagannath19060@gamil.com).

**Bishnu Prasad De,** Electronics & Communication Engineering, Haldia Institute of Technology, Haldia, West Bengal, India (e-mail: bishnu ece@yahoo.co.in)

**Banibrata Bag,** Electronics & Communication Engineering, Haldia Institute of Technology, Haldia, West Bengal, India (e-mail: bani305@gmail.com).

**Raj Kumar Maity**, Electronics & Communication Engineering, Haldia Institute of Technology, Haldia, West Bengal, India (e-mail: hitece.raj@gmail.com).

effect, Drain Induced Barrier Lowering (DIBL), etc which will modify the delay and power models.

There are lots of researches on delay model for CMOS inverter is given in [2,4-6,11,18]. The most popular delay model is descried in nth power law [12] where velocity saturation is main consideration. A closed form expression to accurately estimate the delay of a CMOS deep submicron (DSM) inverter is presented in [14] where a large interconnect RLC load is driven. Accurate drain current and propagation delay modeling for DSM CMOS circuits is essential in the design and analysis of high performance digital integrated circuits in [16]. The expression for power dissipation of CMOS inverter is presented in [2,4-6,11,18].

But all the above models are only valid upto DSM range. In this paper, the simulation of a CMOS Inverter is done considering the channel length in the order of 32nm, 45nm, 65nm and 90nm. The results show that how these two major factors will depends on different design parameters for different channel length. It is also observed the Power Delay Product (PDP) and threshold voltage of CMOS Inverter circuit. It can be easily analyzed the characteristic of the UDSM CMOS Inverter and their application in the field of VLSI.

The rest of paper is organized as follows. The section-II & section-III presents the brief description of the delay and power modeling of CMOS Inverter. Simulation results & Discussions are given in section-IV. Summery & Conclusion are presented in section-V.

# II. DELAY MODELING OF CMOS INVERTER

Based on nth power law [12], delay model of CMOS **inverter** includes for both very fast input as well as very slow input signal. The critical input transition time  $t_{T0}$

$$t_{T0} = \frac{C_0 V_{DD}}{2I_{D0}} \frac{(n+1)(1-v_T)^n}{(1-v_T)^{n+1} - (v_V - v_T)^{n+1}}$$

# Comparative study for delay & power dissipation of CMOS Inverter in UDSM range

Where  $v_T = V_{T0} / V_{DD}$  and  $v_V = V_{INV} / V_{DD}$ . Then the delay  $t_d$ , the delay from  $0.5 V_{DD}$  of input to  $0.5 V_{DD}$  of output, and the effective output transition time  $t_{TOUT}$  can be expressed as follows.  $t_{TOUT}$  can be used as  $t_T$  for the next logic gate;

$(t_T \le t_{T0}$ : for the faster input)

$$\begin{split} t_{d} &= t_{T} \left\{ \frac{1}{2} - \frac{1 - v_{T}}{n + 1} + \frac{\left(v_{V} - v_{T}\right)^{n + 1}}{\left(n + 1\right)\left(1 - v_{T}\right)^{n}} \right\} + \frac{1}{2} \frac{C_{0}V_{DD}}{I_{D0}} \\ t_{OUT} &= \left\{ \frac{C_{0}V_{DD}}{0.7I_{D0}} \frac{4{v_{D0}}^{2}}{\left(4v_{D0} - 1\right)} \right\} \end{split}$$

$t_T > t_{T0}$  for the slower input

$$t_{d} = t_{T} \left[ v_{T} - \frac{1}{2} + \left\{ \left( v_{V} - v_{T} \right)^{n+1} + \frac{\left( n+1 \right) \left( 1 - v_{T} \right)^{n}}{2 t_{T} I_{D0} / C_{0} V_{DD}} \right\}^{\frac{1}{n+1}} \right]$$

$$t_{OUT} = \left\{ \frac{C_{0} V_{DD}}{0.7 I_{D0}} \left( \frac{1 - v_{T}}{t_{d} / t_{T} + 1 / 2 - v_{T}} \right)^{n} \right\}$$

Where  $C_0$  is an output capacitance,  $v_{D0}=V_{D0}/V_{DD}$  and n=velocity saturation index.

# III. POWER MODELING OF CMOS INVERTER

Three types of power dissipation occur in CMOS inverter circuits, which are given below:

- **A.** Leakage power Dissipation: In OFF-state, the main components of leakage currents are sub-threshold leakage ( $I_{sub}$ ), gate induced drain leakage ( $I_{GIDL}$ ), gate tunneling leakage ( $I_{GATE}$ ) and band-to-band tunneling ( $I_{BTBT}$ ).

- **B.** Short-circuit Power: From the  $\alpha$ -power law[1] the short circuit power dissipation model is

$$\begin{split} P_{Sht\_ckt\_pw} &= V_{DD}t_TI_{DO} \frac{1}{\alpha+1} \frac{1}{2^{\alpha-1}} \frac{\left(1-2v_T\right)^{\alpha+1}}{\left(1-v_T\right)^{\alpha}} \\ Where \quad v_T &= \frac{V_{TH}}{V_{DD}} \end{split}$$

# C. DYNAMIC POWER OR SWITCHING POWER:

This type of power dissipation occurs due to the charging and discharging of load and parasitic capacitors.

$$P_{dynamic} = \alpha \cdot C_L \cdot V_{DD}^2 \cdot f + \sum_{i=1}^{n} \alpha_i \cdot C_i \cdot V_{DD} \cdot (V_{DD} - V_T)$$

Dynamic power expression indicate that the average dynamic power of a complex gate due to the output load capacitance.

Where,  $C_L$ =Load Capacitance,  $V_{dd}$ =Supply Voltage, f=Operating Clock Frequency and  $\alpha \rightarrow$  switching activity of gate (the probability of a 0-1 switch in a cycle.

### IV. SIMULATION RESULTS & DISCUSSIONS

All simulations are done in TANNER EDA Tool using the PTM technology of level 54 [8] for 32nm, 45nm, 65nm

and 90nm. Model parameters are extracted from BSIM4.6.1 user manual [9 & 10].

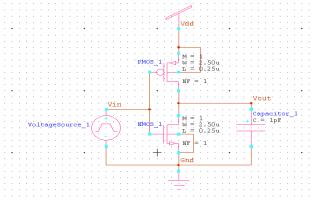

Fig-1: Schematic diagram of CMOS Inverter

The fig-1 shows the snapshot of CMOS inverter which is taken from EDA Tanner simulation tool.

The results clearly show how power dissipation and delay relate to the different design parameters like supply voltage, load capacitance, width of PMOS & NMOS transistor. In all the cases the pulse type {PULSE (0V 1V 0NS 10NS 10NS 100NS 250NS)} input signal is used with rise time (tr=10ns), fall time (tf=10ns) and initial delay time (td=0ns), pulse width (tpw=100ns) and time period (tper=250ns). We compare our results in 32nm, 45nm, 65nm and 90nm for a UDSM CMOS Inverter. The threshold voltage of CMOS inverter is varying with supply voltage and Transconductance ratio.

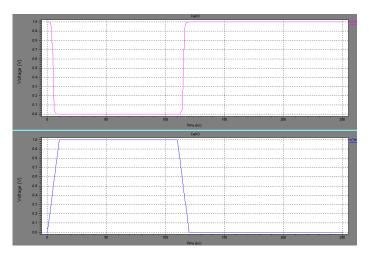

Since the output waveform expression for each of the regions of operation is known, propagation delay can be calculated as the time from the 50% of the rising /falling input to 50% of the falling/rising of the output waveform.

Fig-2: Transient Characteristics of CMOS Inverter

Transient response of CMOS inverter is showing in Fig-2 i.e. input and output waveform w.r.t time in ns.

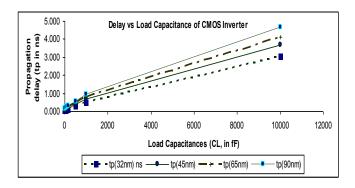

Fig-3: Propagation Delay time (tp in ns) vs. Load capacitance (CL in fF) when Vdd=1V, Wp=5um, Wn=2.5um.

By increasing the load capacitance (CL) of CMOS inverter the Propagation delay time is linearly increased. Fig-3 shows that lowest delay occurs in 32nm technology where as highest delay occurs in 90nm technology.

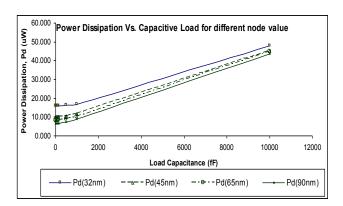

Fig-4: Power Dissipation (Pd in uW) vs. Load capacitance (CL in fF) when Vdd=1V, Wp=5um, Wn=2.5um.

By increasing the load capacitance (CL) of CMOS inverter the power dissipation is linearly increased. Fig-4 shows that lowest power dissipation occurs in 90nm where as highest occur in 32nm.

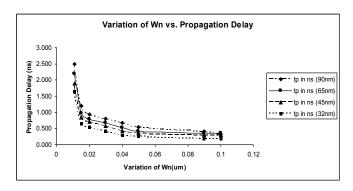

Fig-5: Propagation Delay time (tp in ns) vs. Variation of Wn (um) when Vdd=1V, CL=10fF

Fig-5 shows that the propagation delay is changing with variation of width of NMOS for 32nm, 45nm, 65nm & 90nm.

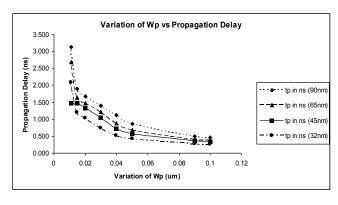

Fig-6: Propagation Delay time (tp in ns) vs. Variation of Wp (um) when Vdd=1V, CL=10fF

Fig-6 shows that the propagation delay is changing with variation of width of PMOS for 32nm, 45nm, 65nm & 90nm.

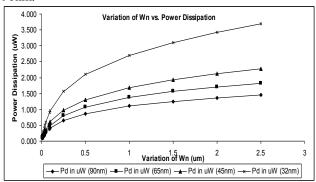

Fig-7: Power Dissipation (Pd in uW) vs. Variation of Wn (um) when Vdd=1V, CL=10fF  $\,$

Fig-7 shows that the power dissipation is changing with variation of width of NMOS for 32nm, 45nm, 65nm & 90nm.

# Comparative study for delay & power dissipation of CMOS Inverter in UDSM range

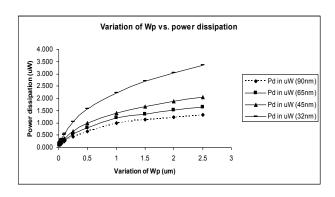

Fig-8: Power Dissipation (Pd in uW) vs. Variation of Wp (um) when Vdd=1V, CL=10fF  $\,$

Fig-8 shows that the power dissipation is changing with variation of width of PMOS for 32nm, 45nm, 65nm & 90nm.

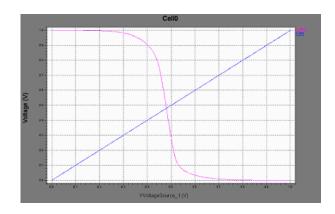

Fig-9: DC Characteristics of CMOS Inverter

Fig-9 shows the DC or transfer characteristic of UDSM CMOS inverter. From this graph we measure the threshold voltage (Vth) (Cross section of the two graphs).

The table-1 shows that variation of supply voltage Vdd how delay and power dissipation will change for different technology. Power dissipation (Pd) will decrease by decreasing supply voltage (i.e. Pd is proportional to the square of the Vdd). In case of propagation delay (tp) is inversely proportional to the supply voltage. From this table we also calculate the Power Delay Product ((PDP=average power consumed \* propagation time delay), in fJ  $(10^{-15})$ ).

Table-1: Delay, power dissipation and PDP relate with supply voltage (CL=10fF, Wp=0.5um, Wn=0.25um)

| Vdd<br>(V) | 32nm    |         |             | 45nm       |         | 65nm        |            |         | 90nm        |            |         |             |

|------------|---------|---------|-------------|------------|---------|-------------|------------|---------|-------------|------------|---------|-------------|

|            | PD (uW) | tp (ns) | PDP<br>(fJ) | PD<br>(uW) | tp (ns) | PDP<br>(fJ) | PD<br>(uW) | tp (ns) | PDP<br>(fJ) | PD<br>(uW) | tp (ns) | PDP<br>(fJ) |

| 0.5        | 0.02    | 116.07  | 2.68        | 0.02       | 4.60    | 0.10        | 0.02       | 4.55    | 0.10        | 0.02       | 4.45    | 0.09        |

| 1          | 1.56    | 0.13    | 0.21        | 0.98       | 0.19    | 0.19        | 0.81       | 0.26    | 0.21        | 0.66       | 0.31    | 0.20        |

| 1.5        | 119.85  | 0.11    | 13.63       | 8.66       | 0.13    | 1.14        | 6.16       | 0.19    | 1.15        | 4.62       | 0.21    | 0.96        |

| 2          | 183.19  | 0.08    | 14.19       | 44.90      | 0.07    | 2.97        | 22.19      | 0.25    | 5.53        | 14.62      | 0.33    | 4.90        |

| 2.5        | 930.46  | 0.03    | 25.82       | 436.40     | 0.01    | 6.02        | 176.54     | 0.14    | 25.50       | 77.43      | 0.04    | 2.89        |

Table-2: Threshold voltage of CMOS Inverter varying with supply voltage for different technology. (CL=10fF, Wp=5um, Wn=2.5um)

| Vdd<br>(V) | vth (mV)<br>(32nm) | vth (mV)<br>(45nm) | vth (mV)<br>(65nm) | vth (mV)<br>(90nm) |

|------------|--------------------|--------------------|--------------------|--------------------|

| 1          | 482.07             | 478.48             | 483.86             | 480.28             |

| 1.5        | 712.36             | 706.97             | 720.41             | 712.34             |

| 2          | 964.14             | 960.55             | 971.31             | 960.55             |

| 2.5        | 1220               | 1220               | 1400               | 1200               |

Inverter threshold voltage will dependent on supply voltage. The table-2 shows the variation of threshold voltage with supply voltage for different technology. We assuming the value of CL=10fF, Wp=5um, Wn=2.5um.

Table-3: Threshold voltage of CMOS Inverter varying with load capacitance for different technology. (Vdd=1V, Wp=5um, Wn=2.5um)

| CL(fF) | vth (mV)<br>32nm | vth (mV)<br>45nm | vth (mV)<br>65nm | vth (mV)<br>90nm |

|--------|------------------|------------------|------------------|------------------|

| 10     | 482.07           | 478.48           | 483.86           | 480.28           |

| 100    | 482.07           | 478.48           | 483.86           | 480.28           |

| 500    | 482.07           | 478.48           | 483.86           | 480.28           |

| 1000   | 482.07           | 478.48           | 483.86           | 480.28           |

| 10000  | 482.07           | 478.48           | 483.86           | 480.28           |

From the above table-3, it is clearly seen that the threshold voltage is independent to the Load Capacitance.

Trans-conductance ratio (Kr=Kn/Kp≈2\*Wn/Wp) and corresponding Wn, Wp values are given in the table-4, shows how threshold voltage depends on Kr value.

Table-4: Threshold voltage of CMOS Inverter varying with transconductance ratio for different technology. (Vdd=1V, CL=10fF)

| Kr(Wn/Wp)                    | vth<br>(mV)<br>(32nm) | vth<br>(mV)<br>(45nm) | vth<br>(mV)<br>(65nm) | vth<br>(mV)<br>(90nm) |

|------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 4 (Wp=5u,<br>Wn=10u)         | 419.31                | 415.72                | 410.34                | 404.97                |

| <b>2</b> (Wp=5u, Wn=5u)      | 451.59                | 446.21                | 446.21                | 442.62                |

| 1 (Wp=5u,<br>Wn=2.5u)        | 482.07                | 478.48                | 483.86                | 480.28                |

| <b>0.5</b> (Wp=10u, Wn=2.5u) | 516.14                | 415.14                | 525.1                 | 451.52                |

| <b>0.25</b> (Wp=20u Wn=2.5u  | 548.41                | 451.64                | 559.17                | 564.55                |

# V. Summary & conclusion

In this paper, basically compare the results of delay and power dissipation of CMOS inverter in UDSM range and also how these are related with different design parameters. From the simulation it has been seen that when channel length less than or equal to 10nm then output waveform are not appeared due to in this range size of the channel length below atomic width. This is the limitation of Nano range [1]. Threshold voltage and Power Delay Product (PDP) are shown in the table form. This work will help to proper characterize and analyze of the CMOS inverter in the Nano range.

# VI. REFERENCES

- [1] A. Ghosh, D. Ghosh, "Optimization of Static Power, Leakage Power and Delay of Full Adder Circuit Using Dual Threshold MOSFET Based Design and T-Spice Simulation" IEEE Computer society, Advances in Recent Technologies in Communication and Computing, 2009, PP-903-905.

- [2] T. Sakurai and A.R. Newton, "Alpha-power Law MOSFET Model and its applications to CMOS Inverter Delay and Other Formulas", IEEE J. Solid-state circuits, vol. 25, no.2, pp. 584-594, April 1990.

- [3] T. Sakurai, A. R. Newton, "Delay analysis of series-connected MOSFET circuits", IEEE J. Solid-State circuits, vol. 26, pp. 122-131, Feb. 1991.

- [4] S. H. K. Embabi, R. Damdaran, "Delay Models for CMOS, BiCMOS, BiNMOS circuits and their applications for timing simulations", IEEE trans. Computer-Aided Design, vol. 13, pp. 1132-1142, Sept. 1994.

- [5] L. Bisdounis, S. Nikolaidis and O. Koufopavlou, "Analytical Transient Response and Propagation Delay Evaluation of the CMOS inverter for short-channel Devices", IEEE J. Solid-state Circuits, vol. 33, no. 2, pp. 302-306, February 1998.

- [6] V. Adler and E. G. Friedman, "Delay and Power Expressions for a CMOS Inverter driving a Resistive-Capacitive Load", Proc. of IEEE Int. Symp. On Circuits and systems (ISCAS), pp. 101-104, 1996

- [7] F. Dartu, N. Menezes, J. Qian, and L.e T. Pillage," A Gate-Delay model for High-Speed CMOS circuits", Proc. ACM/IEEE Design Automation Conference, pp. 576-580, 1994.

- [8] ASU, Berkeley Predictive Technology Model (BPTM) Dept. of EE, Arizona State Univ., Tempe, AZ, 2006 [Online].

- [9] W. Liu et al., BSIM3v3.2.2 MOSFET Model User Manual, Department of Electrical and Computer Engineering, University of California, Berkeley, 1999.

- [10] X. Xi et al., BSIM4.6.1 MOSFET Model User Manual, Department of Electrical and Computer Engineering, University of California, Berkeley, 2007.

- [11] S. Dutta, Shivaling S. M Shetti, and Stephen L. Lusky, "A Comprehensive Delay Model for CMOS Inverters" IEEE Journal of Solid-State Circuits, Vol. 30, No. 8, August 1995.

- [12] T. Sakurai. and R. Newton. "A simple short-channel MOSFET model and its application to delay analysis of Inverters and series-connected MOSFETs," Proceedings of IEEE International Conference on Circuits and Systems, pp. 105-108. 1990.

- [13] A.I. Kayssi, K.A. Sakallah, and T. M. Burks, "Analytical Transient Response of CMOS Inserters," IEEE transactions on Circuits and Systems-I CAS I-39, 42 (1992).

- [14] C. Datta, M. Datta, S. Sahoo, R. Kar, "A Closed Form Delay Estimation Technique for High Speed On-Chip RLC Interconnect Using Balanced Truncation Method", IEEE International Conference on Devices and Communications (ICDeCom-11), Feb 24-25, 2011, pp. 1-4, BIT Mesra, India.

- [15] Makram M. Mansour, Mohammad M. Mansour, Amit Mehrotra, "Modified Sakurai-Newton Current Model and its applications to CMOS Digital Circuit Design", Proceedings of the IEEE Computer Society Annual Symposium on VLSI (ISVLSI'03).

- [16] Hamoui and N. Rumin, "An analytical model for current, delay and power analysis of submicron CMOS logic circuits, "IEEE Trans. Circuits Syst.-II: Analog and Digital Signal\_Processing, vol. 47, pp. 999-1007, Oct. 2000.

- [17] L. Bisdounis, S. Nikolaidis, and O. Koufopavlou, "Analytical transient response and propagation delay evaluation of the CMOS for short-channel devices," IEEE Journal of Solid State Circuits, vol. 33, pp. 302-306, Feb. 1998.

- [18] B Amelifard, M Taherzadeh Sani, H Iman-Eini and A. Kush, "Delay and power estimation of CMOS inverters" 11th ICEE, May 2003, Vol. 1, pp-458-464.

Jagannath Samanta has received his Bachelors Degree B.Tech in Electronics and Communication Engineering under West Bengal University of Technology, Kolkata, West Bengal, in the year 2005, and achieved his Master's Degree M.Tech in Embedded System under West Bengal University of Technology, Kolkata, West Bengal, in year 2008. He has awarded Gold Medal in Master's Degree. His research

interest in Digital VLSI Design, Network-on-chip (NOC) Design etc. He has more than 5 years experience in teaching undergraduate as well as post graduate students. Presently Mr. Samanta is serving as a faculty in the Department of Electronics and communication Engineering, Haldia Institute of Technology, Haldia, West Bengal, India. He has more than 5 international publications.

Bishnu Prasad De has received his Bachelors Degree B.Tech in Electronics and Communication Engineering from Jalpaiguri Government Engineering College, West Bengal, in the year 2007, and achieved his Master's Degree M.Tech in VLSI Design from Bengal Engineering & Science University, Howrah, West Bengal in year 2009. His research interest in VLSI Physical Design, System-on-chip (SOC) Design etc. Presently he is serving as faculty in the

Department of Electronics and communication Engineering, Haldia Institute of Technology, Haldia, West Bengal, India. He has more than 4 international publications.

Banibrata Bag, received the B.E. from Burdwan University in 2004 and M.Tech under WBUT (West Bengal University of Technology) in 2009. He has worked as a software engineering (from 2005 to 2007), and currently working as an assistant professor (from 2010) in the Dept. of Electronic and

Communication Engineering, Haldia Institute of Technology, Haldia, WB, India. His

research interest includes embedded system and processor architecture for multimedia application. He is a professional member of ACM (Association for Computing Machinery).

Raj Kumar Maity, received his B.Tech. & M Tech degrees in Communication Engineering from West Bengal University of Technology, in the years 2005 & 2008 respectively. He has more than five years of teaching experience in different technical colleges under West Bengal University of Technology, and currently working as an assistant professor (from 2010) in the Dept. Electronic and Communication of Engineering, Haldia Institute

Technology, Haldia, WB, India. His research interest includes optical communication networking, Wireless networking, Cryptography & network security etc.