### Software Methods for Improvement of Cache Performance on Supercomputer Applications

Allan K. Porterfield

CRPC-TR89009 May 1989

> Center for Research on Parallel Computation Rice University P.O. Box 1892 Houston, TX 77251-1892

|  |  |  |  | A.,      |

|--|--|--|--|----------|

|  |  |  |  | <b>.</b> |

|  |  |  |  |          |

|  |  |  |  |          |

|  |  |  |  |          |

# Software Methods for Improvement of Cache Performance on Supercomputer Applications

## Allan Kennedy Porterfield

#### Abstract

The performance of many supercomputer programs is limited by the ability to get data from the memory to the processing elements. Increasing bandwidth and decreasing the latency of memory are major concerns of supercomputer architects. Compiler techniques to improve the memory performance of some memory levels have been developed, but no study of the performance and methods to improve the performance of data caches has been reported.

Measuring actual supercomputer cache performance has not been accomplished with previous cache simulation methods. Trace files for programs that take any significant execution time are too large to store. PFC-Sim is a program-driven event tracing facility that can simulate data cache performance of very long programs. PFC-Sim simulates cache concurrently with program execution, allowing very long traces to be used, since the trace entries are discarded as quickly as they are generated. Some of these programs have traces in excess of 4 billion entries.

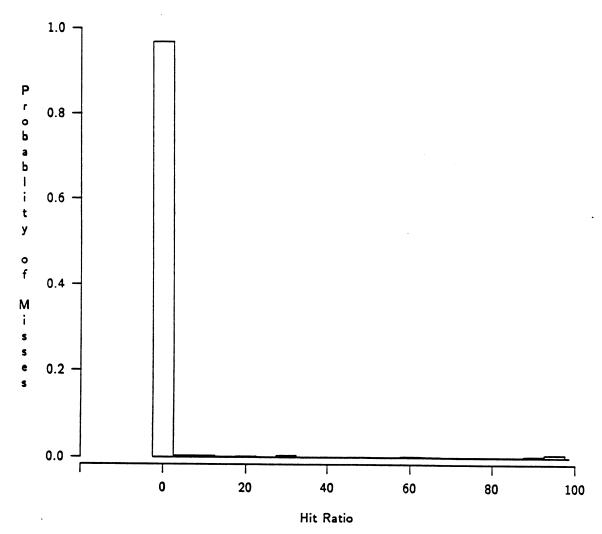

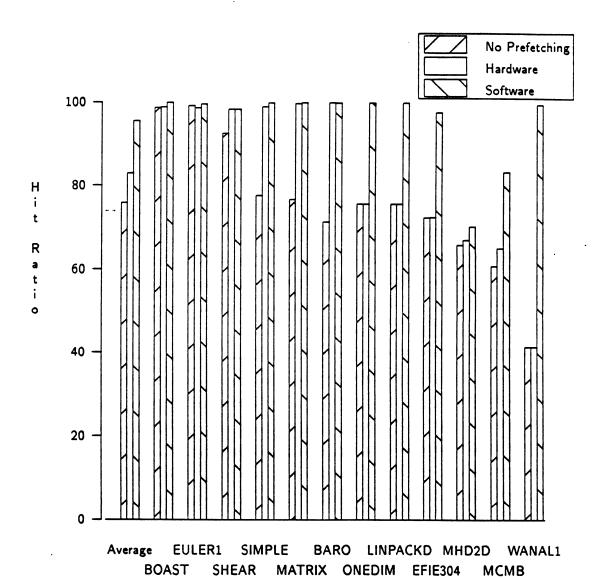

In this work, PFC-Sim is used to measure the cache performance of array references in a benchmark set of supercomputer applications, RiCEPS, gathered at Rice University. Data cache hit ratios varied between 44 and 99% (average 70%) for a 16K cache and 48 and 99% (average 91%) for a 256K cache. Some of the programs have very large working sets, yielding poor cache performance even with large caches. PFC-Sim also determines the cache performance for each memory reference in the original program. The hit ratios were clustered around either 100% or 0%.

By locating the references that miss, attempts to improve memory performance can focus on references where improvement is possible. The compiler can estimate the number of loop iterations which can execute without filling the cache, the overflow iteration. The overflow iteration combined with the dependence graph can be used to determine at each reference whether execution will result in hits or misses. Using this

estimate of dynamic memory performance, two methods for improving performance are examined, program transformation and software prefetching.

Program transformation can be used to improve cache performance by reordering computation to move references to the same memory location closer together, thereby eliminating cache misses. Many programs have been transformed by hand to improve their memory performance. Using the overflow iteration, the compiler can often do this transformation automatically. Automatic blocking has advantages in correctness and portability. Standard blocking transformations cannot be used on many loop nests that contain transformation preventing data dependences. A new version of blocking transformations is defined, wavefront blocking, which allows any loop nest to be blocked, if the components of dependence vectors are bound between the references in the loop nest.

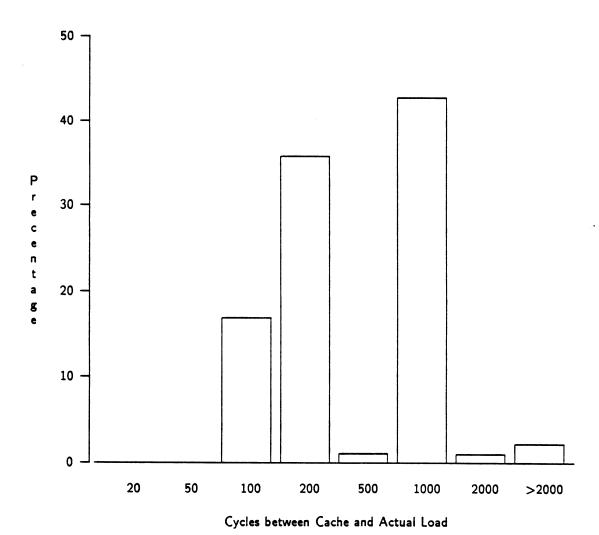

When the cache misses cannot be eliminated, software prefetching can overlap the miss delays with computation. Software prefetching uses a special instruction to preload values into the cache. A cache load resembles a register load in structure, but does not block computation. It only moves the address into cache where a later register load will be required to bring the value into the processor. Using a simple heuristic, the compiler can inform the cache (on average) over 100 cycles before the process will require a load of the value. This allows the cache misses to be serviced in parallel with the computation.

# Contents

|   | Abs             | stract                |                                    | i   |  |  |  |  |

|---|-----------------|-----------------------|------------------------------------|-----|--|--|--|--|

|   | Acknowledgments |                       |                                    |     |  |  |  |  |

|   |                 | List of Illustrations |                                    |     |  |  |  |  |

|   |                 | of Tab                |                                    | vii |  |  |  |  |

|   | List            | or lac                | Dies                               | 2   |  |  |  |  |

| 1 | Int             | rodu                  | ction                              | 1   |  |  |  |  |

|   | 1.1             | Overv                 | view                               |     |  |  |  |  |

|   |                 | 1.1.1                 | Cache Memories                     | 2   |  |  |  |  |

|   | 1.2             | Deper                 | ndence Theory                      | -   |  |  |  |  |

|   |                 | 1.2.1                 | Data Dependence Analysis           | -   |  |  |  |  |

|   |                 | 1.2.2                 | Data Dependence Analysis of Arrays | 5   |  |  |  |  |

|   |                 | 1.2.3                 | Cache Dependence                   | 10  |  |  |  |  |

|   |                 | 1.2.4                 | LC(x) and $D(x)$                   | 11  |  |  |  |  |

|   |                 | 1.2.5                 | Uniformly Generated Dependences    | 12  |  |  |  |  |

|   | 1.3             | Previo                | ous Work                           | 13  |  |  |  |  |

|   |                 | 1.3.1                 | Cache Performance Studies          | 13  |  |  |  |  |

|   |                 | 1.3.2                 | Improving Memory Performance       | 14  |  |  |  |  |

| 2 | Da              | ta Ca                 | ache Performance                   | 21  |  |  |  |  |

|   | 2.1             |                       | luction                            | 21  |  |  |  |  |

|   | 2.2             |                       | Compiler Evaluation Program Suite  |     |  |  |  |  |

|   | 2.3             |                       | Sim                                | 25  |  |  |  |  |

|   |                 | 2.3.1                 | PFC-Sim Preprocessor               | 27  |  |  |  |  |

|   |                 | 2.3.2                 |                                    | 28  |  |  |  |  |

|   |                 | 2.3.3                 | Memory Simulation                  | 30  |  |  |  |  |

|   |                 | 2.3.4                 | Visualization Tools                | 34  |  |  |  |  |

|   | 2.4             |                       | Potential Uses of PFC-Sim          | 34  |  |  |  |  |

|   | 4.4             | 2.4.1                 | iments                             | 36  |  |  |  |  |

|   |                 |                       | Cache Size                         | 36  |  |  |  |  |

|   |                 | 2.4.2                 | Set Associativity                  | 11  |  |  |  |  |

|   |               | 2.4.3 Write Policy                        | 44         |

|---|---------------|-------------------------------------------|------------|

|   |               | 2.4.4 Prefetching                         | 47         |

|   |               | 2.4.5 Hit Ratios of Individual References | 53         |

|   |               | 2.4.6 Processor Performance               | 56         |

|   | 2.5           | Summary                                   | 60         |

| 3 | Sta           | atic Model of Memory Performance          | 62         |

|   | 3.1           | Introduction                              | 62         |

|   | 3.2           | Overflow Iteration                        | 63         |

|   | 3.3           |                                           | 03<br>74   |

| 4 | $\mathbf{Pr}$ | ogram Transformation                      | <b>7</b> 0 |

|   | 4.1           | Introduction                              | <b>76</b>  |

|   | 4.2           | Loc Fusion                                | 76<br>75   |

|   | 4.3           | Loop Distribution                         | 77         |

|   | 4.4           | Loop Interchange                          | 83         |

|   |               | 4.4.1 Example                             | 86         |

|   | 4.5           | Strip Mine and Unroll                     | 90         |

|   | 4.6           | Peel and Jam                              | 90         |

|   |               | 4.6.1 Safety                              | 92         |

|   |               | 4.6.2 Example                             | 93         |

|   | 4.7           | Loop Skew and Interchange                 | 94         |

|   | 4.8           | Blocking Transformations                  | 98         |

|   |               | A S 1 String Mingray I Take 1             | 100        |

|   |               | 489 IIII II                               | 100        |

|   |               | 4.8.3 Wavefroot Displan                   | 104        |

|   |               | 181 Charing the December 11               | 108<br>111 |

|   | 4.9           | F. ffeetiveness                           | 113        |

|   |               | 401 Transformable D                       | 113        |

|   |               | 4.0.9 Non-American 11 D                   | 115        |

|   |               | 402 Somithments 11 D                      | 115        |

|   |               | 404 Automotic D1 1: ( 1D 11 )             | 117        |

|   | 4.10          | Conclusions                               | .13        |

| 5 | Sof | ftware Prefetching                   | 122                    |

|---|-----|--------------------------------------|------------------------|

|   | 5.1 | Introduction                         | 122                    |

|   | 5.2 | Cache Load Instruction               |                        |

|   | 5.3 | Insertion of Cache Load Instructions | 123                    |

|   | 5.4 | Effectiveness                        | 124                    |

|   | 0.1 | Effectiveness                        | 126                    |

|   |     |                                      | 126                    |

|   |     |                                      | 130                    |

|   | 5.5 |                                      | 133                    |

|   |     | 5.5.1 Data Traffic                   | 133                    |

|   |     | 5.5.2 Dun time Ohard                 | 135                    |

|   | 5.6 | Mothods to Poduce Costs              | 137                    |

|   |     | 5.6.1 Dradiation of Misses           | 137                    |

|   |     | 5.6.9 Designa Allegation             |                        |

|   | 5.7 | Conclusions                          | 139                    |

|   | J., |                                      | 141                    |

| 6 | Co  | nclusions                            | .42                    |

|   | 6.1 | Overvious                            | . <del>42</del><br>142 |

|   | 6.2 | Future Work                          |                        |

|   |     |                                      | 144                    |

|   |     |                                      | 144                    |

|   |     | 6.2.2 Multiple Levels of Cache       | 145                    |

|   | Bib | oliography                           | 46                     |

# Illustrations

| 1.1  | Types of Data Dependences                                   | 7  |

|------|-------------------------------------------------------------|----|

| 2.1  | PFC-Sim                                                     | 23 |

| 2.2  | Matrix Multiply - Before and After PFC-Sim                  | 31 |

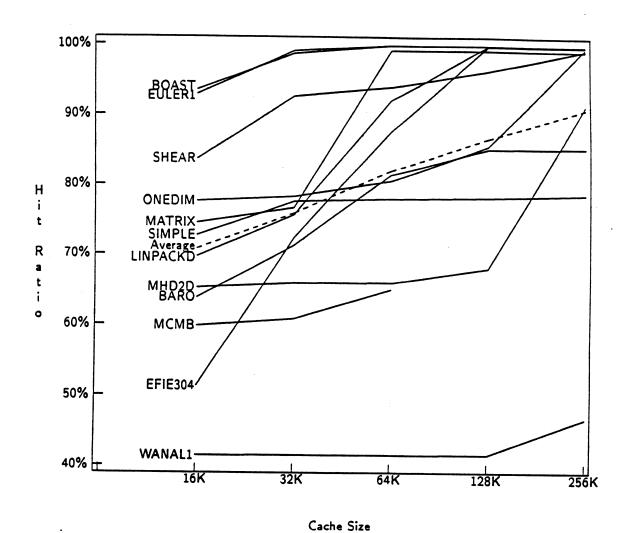

| 2.3  | Effects of Cache Size - Hit Ratios                          | 37 |

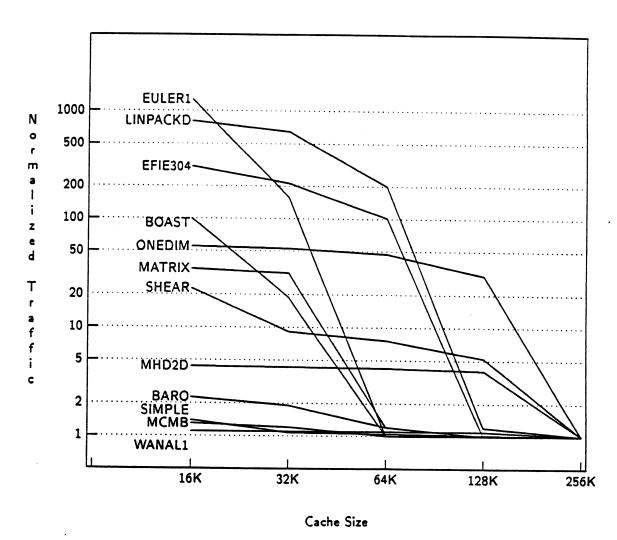

| 2.4  | Effects of Cache Size - Normalized Data Traffic             | 4( |

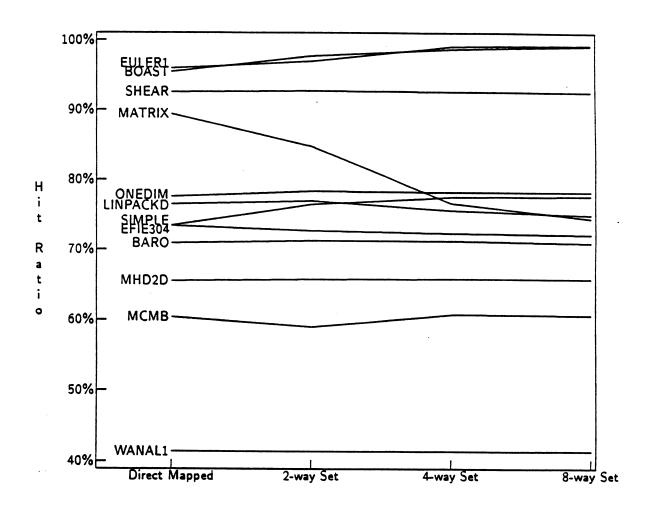

| 2.5  | Effects of Set Associativity - Hit Ratios                   | 42 |

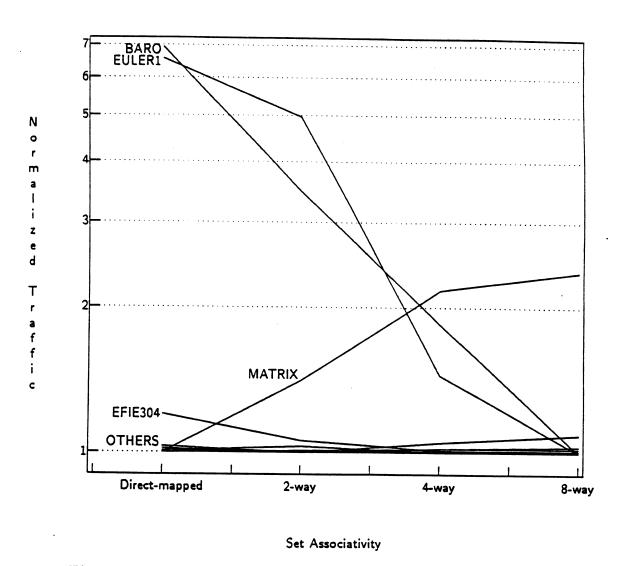

| 2.6  | Effects of Set Associativity - Normalized Data Traffic      | 43 |

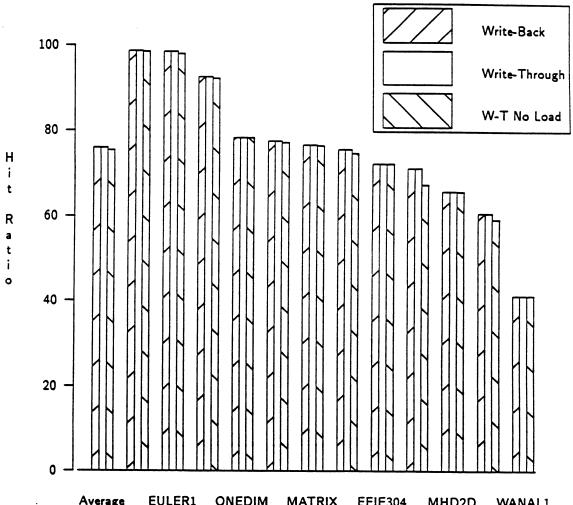

| 2.7  | Effects of Various Write Policies - Hit Ratios              | 45 |

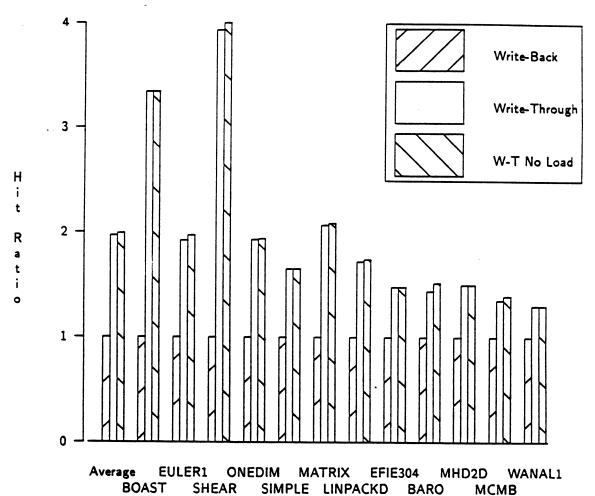

| 2.8  | Effects of Various Write Policies - Normalized Data Traffic | 46 |

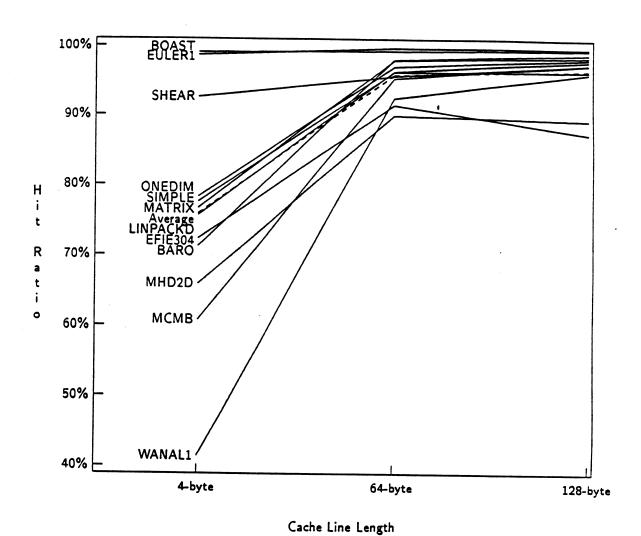

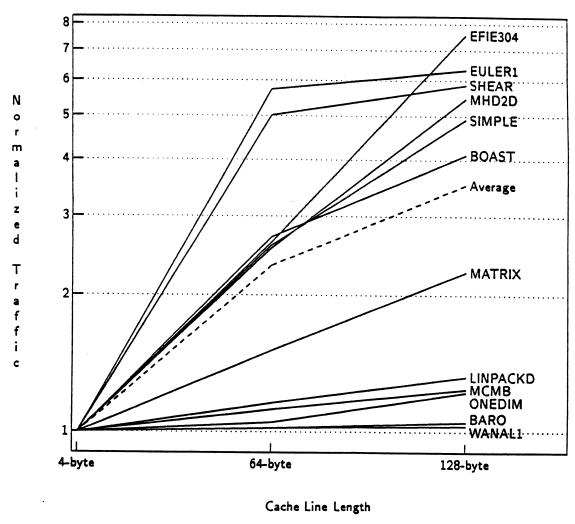

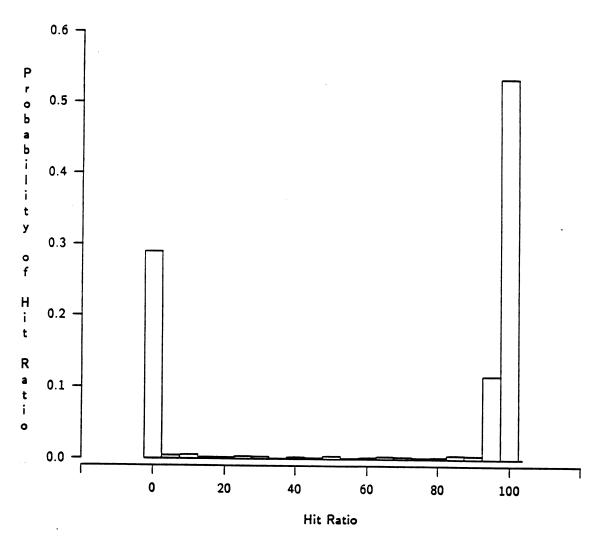

| 2.9  | Effects of Cache Line Lengths - Hit Ratios                  | 48 |

| 2.10 |                                                             | 49 |

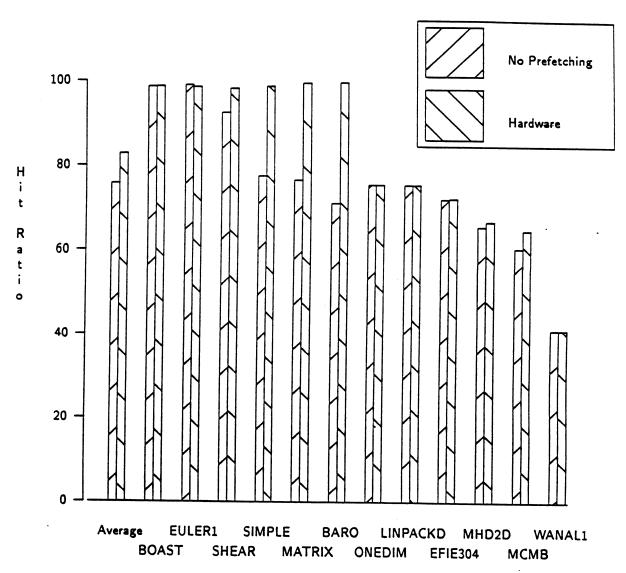

| 2.11 |                                                             | 51 |

| 2.12 | Effects of Hardware Prefetching - Normalized Data Traffic   | 52 |

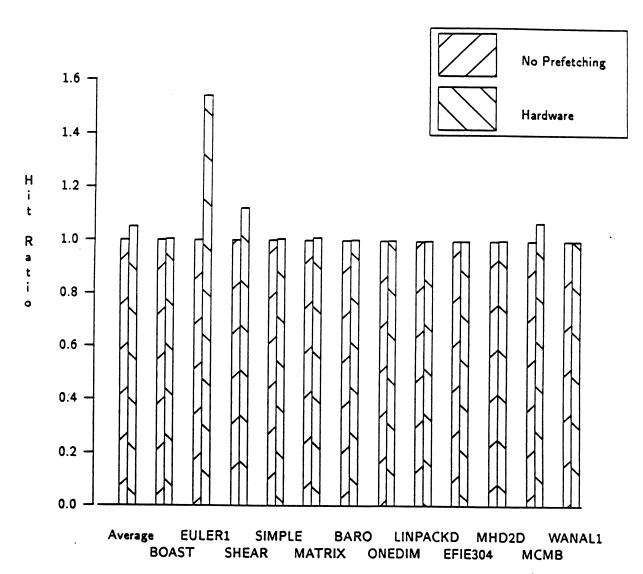

| 2.13 | Individual Hit Ratio Distribution                           | 54 |

|      | Hit Ratios Weighted by Number of Misses                     | 55 |

|      | Percentage of Execution Time Spent in Miss Delays           | 58 |

| 3.1  | Computing the Overflow Iteration, O                         | 67 |

| 3.2  | Computing the Misses in a Code Segment                      | 68 |

| 4.1  | Loop Fusion                                                 | 77 |

| 4.2  | Profitability of Loop Fusion                                | 82 |

| 4.3  | Loop Distribution                                           | 83 |

| 4.4  | Profitability of Loop Distribution                          | 85 |

| 4.5  | Loop Interchange                                            | 87 |

| 4.6  | Profitability of Loop Interchange                           | 89 |

| 4.7  | Strip Mining                                                | 91 |

| 4.8  | Unrolling                                                        | 91  |

|------|------------------------------------------------------------------|-----|

| 4.9  | Peel and Jam                                                     | 9:  |

| 4.10 | Application of Peel and Jam to WANAL1                            | 96  |

| 4.11 | Application of Peel and Jam to SIMPLE                            | 97  |

| 4.12 | Loop Skew                                                        | 99  |

| 4.13 | Strip Mine and Interchange                                       | 101 |

| 4.14 | Strip Mine Width Computed during Execution                       | 104 |

| 4.15 | Unroll and Jam                                                   | 105 |

| 4.16 | Unroll and Jam Example                                           | 107 |

| 4.17 | Unroll Factor Computed during Execution                          | 108 |

| 4.18 | Wavefront Blocking: Strip Mine, Skew and Interchange             | 109 |

| 4.19 | Wavefront Blocking: Unroll, Peel and Jam                         | 110 |

| 4.20 | Profitability of Blocking                                        | 112 |

| 4.21 | LINPACKD — Pivoting Preventing Transformation                    | 116 |

| 4.22 | FTRVMT — Linearization Preventing Transformation                 | 118 |

| 5.1  | Insert Prefetch Instructions                                     | 125 |

| 5.2  | PFC-Sim with Prefetching — Matrix Multiplication                 | 123 |

| 5.3  | PFC-Sim with Prefetching - a portion of SHEAR                    | 127 |

| 5.4  | PFC-Sim with Prefetching — Index Array                           | 127 |

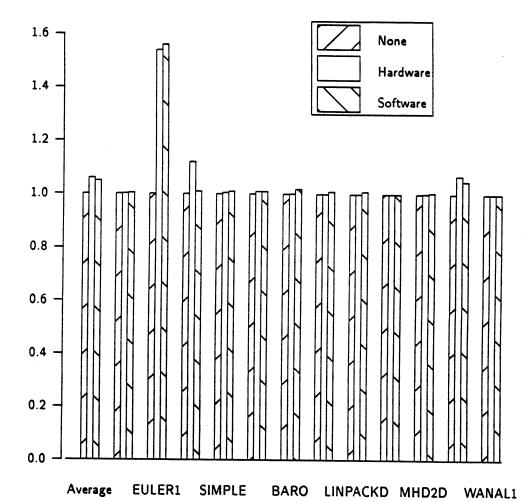

| 5.5  | Effect of Software Prefetching - Hit Ratios                      |     |

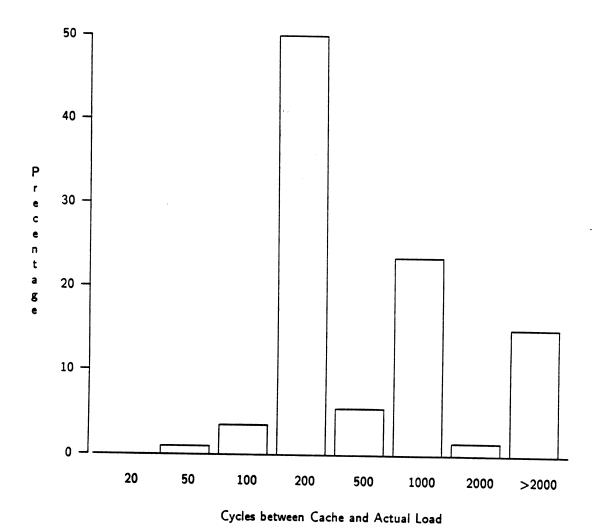

| 5.6  | Software Prefetching - Time Between Prefetch and Use (Absolute   | 129 |

|      | Totals)                                                          | 131 |

| 5.7  | Software Prefetching - Time Between Prefetch and Use (Normalized | 191 |

|      | Totals)                                                          | 132 |

| 5.8  | Effect of Software Prefetching - Data Traffic                    | 134 |

| 5.9  | Insert Prefetch Instructions (Estimated Misses Only)             | 134 |

|      |                                                                  | TOO |

# Tables

| 2.1 | Data Traffic per Floating Point Operation                    | 60  |

|-----|--------------------------------------------------------------|-----|

| 3.1 | Matrix Multiply (100 x 100) — $F$ , $\Delta$ , and $O$       | 72  |

|     | Matrix Multiply — Computed Cache Performance of Dependences  |     |

|     | Matrix Multiply — Computed and Actual Hit Ratios (32K cache) |     |

| 5.1 | Useful Prefetches                                            | 136 |

| 5.2 | Execution Time with and without Software Prefetching         |     |

| 5.3 | Useful Prefetches — After Using Overflow Iteration           |     |

# Acknowledgments

No dissertation is written without a great deal of help and this one is no exception. First and formost, I would like to thank Ken Kennedy for it was his faith in my ability that allowed me to return to school, and his direction that guided this dissertation. David Callahan was the source of many valuable discussions in all areas of compiler optimization and helped immensely throughout the writing of this dissertation. I also want to thank the friends that maintained my sanity throughout graduate school, David Harper, Alan Carle, Jerry Fowler and the entire PFC group. Burton Smith and Tera Computer Company provided the time that was required to finish.

Thank you, Beth and Suzie, for being much better kids than I could ever have been. And finally, thank you Carrie, without whom I could never have gone back to school and maintained the lifestyle to which I had grown accustomed. Thanks also for providing motivation when it was lacking.

# Chapter 1

# Introduction

#### 1.1 Overview

A major limitation of supercomputers today is the inability to get data to the processing units fast enough to keep the units busy. Vector and parallel processors replicate arithmetic units, dramatically increasing the number of operations that can be performed during any time period. Vector and shared memory multiprocessors, however, still have (at some point in the memory hierarchy) a single memory to support the increase in computational power. This has placed a substantial burden on computer architects to increase bandwidth between the memory and the processing units. Doubling the number of processing units is much easier than doubling the amount of data that main memory can supply during a given time period. As less bandwidth per processor is available, it becomes increasingly important to understand how the bandwidth is used and to define mechanisms to improve its effectiveness.

In von Neumann and data-flow architectures, data must be moved to each processing element before it can be manipulated. Computation may be abstractly modeled as a flow of data between the processor and the memory. In an abstract model, the processor makes requests to a black box, known as the memory, which returns values at some rate (the bandwidth) after a delay (average memory latency). When modeling computation, the boundary between memory and the processor is flexible. Several natural locations to measure the flow of data are between the registers and cache, between cache and main memory, and between main memory and backing store. If the processor includes the registers but not the cache, the memory requests are the loads and stores in the program. When the processor is defined to include the main memory but not backing store, the memory requests are the virtual page misses generated.

Execution time in this model is not time required to do the computation,  $T_c$ , plus the time waiting for the data to arrive,  $T_m$ . The time spent waiting for data to arrive

is the number of memory requests, R, times the average memory latency. If this is broken into components for a three-level memory hierarchy, total execution time is  $T_c + T_{m_{cache}} + T_{m_{main}} + T_{m_{backing}}$ .

Most compiler optimization research has studied methods to reduce  $T_c$ , since it typically encompasses the majority of the total execution time. Register allocation has been the major research area addressing the time spent waiting at any memory level. Register allocation reduces  $T_{m_{cache}}$  by reducing the number of requests to cache. Virtual memory systems attempt to reduce  $T_{m_{backing}}$  by minimizing the number of virtual page misses that occur across all active programs. Little research has been done on how a compiler can reduce the amount of time spent waiting on requests to either main memory or the backing store [AS79],[Tha81].

The amount of time spent waiting on memory can be reduced in two ways. Either the number of requests can be reduced or the average latency can be reduced. When possible, reducing the number of requests may also reduce the average latency. Memory latency is a function of the rate of requests,  $R/(T_c+T_m)$ . When the number of requests exceeds the bandwidth of the memory, average latency will increase until the average rate of requests can be satisfied by the bandwidth. Saturation of the memory bandwidth increases  $T_m$  until it is a significant fraction of the total execution time. Reducing execution time for a program that saturates the memory bandwidth will require either more memory bandwidth or fewer memory requests.

Previous work in reducing the traffic between a cache and main memory has mainly involved studies of different cache architectures. Natural program locality is high enough to ensure that caches are effective and the cache-main memory interface rarely if ever saturates on non-vector uni-processors. As vector and parallel processors become more common, this will no longer be true. Their multiple processing elements can manipulate much more data in a given time period, greatly increasing the probability that the bandwidth between the cache (or caches) and the main memory becomes saturated. (Note that in the abstract model, multiple computational elements can be represented by lowering the computation time,  $T_c$ , allowing a very simple method of simulating the effect of parallel or vector processors.) A second effect of parallel processors comes from parallel programming. For many problems, extracting parallelism decreases locality of reference of each processor. Thus, the

total number of references per time unit is rising and processor reference locality is falling, greatly increasing the strain on memory hierarchies.

This dissertation studies the amount of data that flows across the cache-main memory boundary for supercomputer applications. The focus of this work is computationally intensive programs. These programs are the most likely to access large amounts of data, stressing the memory system. Computationally intensive programs are also likely to use highly optimizing compilers to produce the fastest executables possible. Scientific programs that are typically run on supercomputers require a large number of floating point operations. Smaller programs on medium or small computers may benefit from the techniques developed in this thesis, but the focus of this work is on the programs that require Cray-class computers. Methods to reduce the amount of data traffic by increasing the average number of references to each item while it resides in the cache are explored. Increasing the average number of references to each cache item reduces the number of memory requests.

When a memory location is requested, most architectures wait for the value to return before continuing. Certain architectures and operating systems have tried to hide memory latency from the processor. Almost every virtual memory system transfers control to another process during a page miss. This allows the processor to do productive work on other jobs while the backing store produces the page. Some RISC architectures (e.g. IBM's RT) attempt to hide the delay between the registers and the memory by allowing several instructions to execute between a register load and the arrival of data in the register. The Denelcor HEP and HORIZON [KS88] architectures hide main memory latency by switching instruction streams every cycle. If enough instruction streams are available, the processor never delays waiting for memory to return a value. Since the HORIZON is, for the time being, a paper architecture, and few, if any, HEPs are still running, supercomputers today generally wait for the memory on every main memory access.

People seem to believe that the amount of processing lost during these delays,  $T_{m_{main}}$ , does not significantly slow uni-processors. Otherwise, more work on methods to improve cache performance would exist today. Architects of shared-memory MIMD machines have found memory latency problems to be the principal difficulty in effectively utilizing their machines [KS88]. Cedar[GKLS83] and RP3[PBG+85] compilers go to some effort to localize a processor's memory accesses (both spatially

and temporally) to reduce the memory latencies. If memory latency has such an effect on multiprocessors, the assumption that the time spent waiting for memory on uni-processors is insignificant may not be correct.

This dissertation examines that assumption and explores methods to help all programs reduce average memory latency by separating cache and register loads. Separating cache and register loads allows memory latency to be overlapped with execution, reducing the average amount of time spent waiting for each memory request. The next section gives some background on cache memories and dependence analysis. This is followed by a discussion of the previous work in this area.

#### 1.1.1 Cache Memories

Cache memories are high-speed buffers used to hold portions of the main memory believed to be in use. Values in a cache can be accessed in much less time than would be required to access main memory. When a significant fraction of the references are found in the cache, the total memory delay during execution is reduced. The effectiveness of cache has been explained by the "property of locality" [Den72]. Over short periods of time, references are accessed non-uniformly over its address space. References to be used in the near future are likely to be values used in the recent past or those values that are close to the present values.

Cache design has several performance criteria. A cache should maximize the probability that it contains a requested value (the hit ratio). The cache should also be as simple as possible to minimize cache hit access time. Their are other criteria, but these are normally the two most important.

The design of a cache involves a number of decisions. This work examines the benefits (in terms of increasing the hit ratio) and costs (in terms of the total data traffic required) of a number of potential cache structures. The cache parameters discussed in this work are cache size, cache associativity, cache replacement policy, main memory update policy, line size and hardware prefetching.

#### Cache Size

The first parameter of a cache normally given is its size. The more values that are kept in cache, the higher the probability that the requested value is present. Caches cannot be expanded without limit because of cost, physical size constraints and limited access

time. A design may attempt to use the smallest cache that provides a certain level of performance.

#### Cache Associativity

The user cannot directly address the cache, but rather the cache serves as a buffer for addresses in the main memory. The mapping of addresses into the cache is determined by the associativity of the cache. A fully associative cache can map an address in main memory to any cache block. This requires that the cache maintain a very large associative memory. Each time a block is accessed, the address must be compared against the associative memory to determine if the address is present in the cache. At the other end of the spectrum are direct mapped caches, which map each address to a unique cache block. During a lookup, only one location must be checked to determine if the value is present in the cache. Between the two extremes are set associative caches. A set associative cache can map an address into a limited number of locations. The number of potential cache locations for an address is determined by the degree of set associativity, 2 for 2-way, 4 for 4-way, etc. Most computer caches designed today are set associative.

A tradeoff exists between the number of sets and set size. A direct mapped cache will have four times as many sets that are one-quarter the size of sets in a 4-way associative cache. Poor performance occurs when programs cyclically reference more elements than can be kept in a set. For a direct mapped cache, two elements that are accessed alternately and map to the same slot produce no hits. For larger set sizes, the number of items in the rotation can be larger before performance degrades.

#### Cache Replacement Policy

When a value is requested from the cache which is not present and the cache is full, some block in the cache must be removed so that the requested block can be brought into the cache. The goal of a replacement policy is to remove values that will not be used in the future.

## Main Memory Update Policy

There are two basic methods that memory buffers use to update the backing memory. The buffer either waits as long as possible before writing a value back to the

memory hoping to reduce the number of writes, or it passes modified values through immediately, reducing coherency problems and the maximum time to satisfy a miss. Delaying the write to the backing memory is called a write-back (or copy-back) write policy. Immediately passing the value through to the next memory is a write-through policy. The advantage of the write-back method is a much lower volume of memory traffic. For multiprocessors, where the volume of memory traffic will be crucial, the write-through memories have the advantage of maintaining consistency between processors. Write-through memories are further broken into two groups depending on whether it is believed that a value that is written will be used again before it is flushed from the memory. The write-through no-load on write-miss policy speculates that it will not be used again so it does not save the block in the cache after storing the value in main memory. While the standard write-through policy loads the block into the cache on a write miss.

#### Line Size

To improve the probability that a value is in the cache when requested, there are several mechanisms to prefetch memory locations. Prefetching (fetching before the actual request) allows the cache to guess what values will be needed in the near future and bring them into the cache. The cache line is the fixed-sized unit of information transfer between the main memory and the cache. The most common prefetching mechanism is the multi-word cache line. The presence of adjoining items increases the number of hits whenever locality of reference exists in the accesses.

## Hardware Prefetching

A second form of prefetching that can be implemented is hardware prefetching. In a hardware prefetching scheme, whenever the first word of a cache line is accessed, the next sequential cache line is fetched from the main memory. For example, if address 100400 were accessed (either loaded from or stored into), then the hardware would request that the block starting at 100404 be brought from main memory to the cache (assuming one word cache lines). Hardware prefetching is very effective when FORTRAN arrays are accessed along columns.

## 1.2 Dependence Theory

To correctly determine if an address is in the cache when it is accessed, it is necessary to know the last time that it was used. In conjunction with the development of restructuring compilers for vectorization and parallelization, a method for describing the constraints on execution order, called data dependence analysis, has been developed. The constraints identify the potential last accesses of any memory location in the program. A conservative set of dependences is built during the analysis. There are four types of dependences: true, anti, output and input [Kuc78][KKP+81].

#### 1.2.1 Data Dependence Analysis

The four types of data dependences are shown in Figure 1.1. To have a true dependence between two statements, a value defined in statement  $S_1$  must be used in statement  $S_2$ . A true dependence can be viewed as a requirement that a producing statement execute before the consuming statement. A second type of constraint occurs when a statement  $S_1$  uses a value, and a later statement  $S_2$  redefines that value. Statement  $S_1$  must be executed first to ensure that the value produced by  $S_2$  is not used in  $S_1$ . This is an anti-dependence. A third ordering constraint occurs when statement  $S_1$  defines a value and a later statement  $S_2$  also defines the value. For the value to be correct upon completion of both statements,  $S_2$  must follow  $S_1$ . Dependences of this type are called output dependences. An input dependence is not a constraint on execution order but does indicate a reuse of a memory location. Since both  $S_1$  and  $S_2$  only use the same value, they can execute in any order and produce correct results.

Data dependences do not specify all of the constraints on statement ordering. Control flow through the program affects which statements are actually executed.

$$S_1$$

A = ... = A A = ... = A  $S_2$  ... = A A = ... A = ... = A true anti output input

Figure 1.1 Types of Data Dependences

For instance, in the following example, statement  $S_2$  depends on which branch is taken in statement  $S_1$ .

$$S_1$$

IF (I.EQ.0) GOTO 10

$S_2$  ANS = ANS / I

$S_3$  10 CONTINUE

$S_2$  is said to be control dependent [KKP+81] on  $S_1$ . To avoid dealing with control dependences as a separate form of dependence, a process called IF-Conversion [AKPW83] has been developed to convert all control dependences into data dependences. IF-Conversion removes all control flow by replacing forward branches with guards on the affected statements. Backward branches are replaced with guards and explicit WHILE loops. IF-Conversion allows us to focus only on data dependences.

Data dependences in the presence of DO loops can be characterized as either loop carried or loop independent [All83]. A loop carried dependence is simply a dependence that exists between separate iterations of a loop. Each loop carried dependence is associated with a particular loop in the program. A loop independent dependence is a dependence within a single iteration of the loop. Any dependence that is not surrounded by a loop (i.e., exists if all loops are removed) is also loop independent.

# 1.2.2 Data Dependence Analysis of Arrays

When array references are treated as single scalar variables, very imprecise information is generated. If different elements of an array are being accessed, memory is not being reused and no dependence exists. By determining when the iteration space of array references does not overlap, a much more accurate dependence graph can be built. To make data dependence information on arrays more precise, several tests have been developed to determine if a dependence exists between two array references. For a majority of array references, these tests precisely determine whether dependences exists. For example, in the following loop,

| $(S_1)$ | DO I = 1,30      |

|---------|------------------|

| $(S_2)$ | A(I) = A(I)*B(I) |

| $(S_3)$ | C(I) = A(I+1)    |

| $(S_4)$ | ENDDO            |

if arrays A, B and C were treated as scalar variables, a loop independent true dependence would exist from  $S_2$  to  $S_3$  on A. Additionally, four loop carried dependences would be identified: (1) a true dependence from  $S_2$  to  $S_2$  on A, (2) an anti-dependence from  $S_3$  to  $S_2$  on A, (3) an output dependence from  $S_2$  to  $S_2$  on A and (4) an output dependence from  $S_3$  to  $S_3$  on C. The multiple cycles in the dependence graph would mark this loop as unparallelizable.

However, if we consider the arrays on an element by element basis, a more precise picture emerges. Since no memory location is modified more than once in the loop, no output dependences actually exist.  $S_2$  and  $S_3$  use the value of A present before the loop starts execution, eliminating both true dependences. The only dependence that remains is the loop carried anti-dependence from  $S_3$  to the next iteration's  $S_2$  on the variable A. With only a single dependence to guarantee, a restructuring compiler can attempt to produce a parallel or vector version of this loop.

A statement in a loop actually represents a large collection of executable statements, one executable statement per iteration. A direction vector [Wol82] relates references to the same memory location according to which iterations of the enclosing loops cause the overlap. The direction vector is formed from the distance vector, which is the pairwise difference of the overlap of the iteration space that causes the two references to access the same data. The distance vector represents the number of iterations of a loop that a dependence must cross. This will be an important value in determining if a requested value is present in the cache.

Much research has been done to determine when data dependences exist between statements with arrays [Ban76] [Ban79] [AK84] [Kuh80] [Wol82] [All83] [TIF86]. The problem can be stated as, "Given two array references and information about which loops contain them, do they ever refer to the same storage location?"

A data dependence exists between two array references  $A(f(\vec{i_1}))$  and  $A(g(\vec{i_2}))$  if, and only if, for some vector  $\vec{i_1}$  and  $\vec{i_2}$

$$f(\vec{i}_1) - g(\vec{i}_2) = 0$$

Bernstein proved that this problem is undecidable for arbitrary functions f and g [Ber66]. Knuth showed that for real programs, the expressions are generally simple [Knu71]. Therefore, placing restrictions on f and g is reasonable. In order to solve

the problem, functions have been restricted to affine functions in the loop control variables, i.e.,

$$f(\vec{i}) = a_0 + a_1 \cdot i^1 + \dots + a_k \cdot i^k$$

where  $a_j$  is constant.

Making this restriction, two tests have been developed to determine data dependences, the gcd test [Coh73][Ban76] and Banerjee's Inequality[Ban76][Wol82] [AK84]. The gcd test determines whether any integer solutions exist for f - g = 0. Banerjee's Inequality determines whether there are any solutions to the same equation (integer or real) within the area specified by the loop bounds. Both of the tests are conservative. If either determines that a dependence does not exist, there is no dependence. There are cases where both tests determine that a dependence could exist when there is actually no dependence.

Before applying the gcd or Banerjee's test, the optimizing compiler at Rice University, PFC, uses a separability test. The separability test is quick and accurate, but works only on a restricted set of subscript expressions<sup>1</sup>. If a pair of subscripts are of the form  $ai + b_1$  and  $ai + b_2$ , then a dependence exists if either (1) a = 0 and  $b_1 = b_2$  or (2)  $\frac{b_1 - b_2}{a}$  is an integer and is less than or equal to the upper bound of a normalized loop. Separability is much faster than the other tests and works on at least 50% of the expression pairs in a group supercomputer applications. For some of the programs in the group, over 95% of the expression pairs are separable [Ros88].

Kuhn and Triolet [Kuh80][TIF86] describe the region of memory references by a set of linear inequalities. If the sets of linear inequalities overlap, then a dependence exists. This method is more accurate, but potentially much slower.

#### 1.2.3 Cache Dependence

When dealing with cache, there is no distinction between types of references. A load has the same effect as a store — both cause the item touched to become the "most recently used" (ignoring, for the time being write-through no-load on miss). Thus there need be only one type of cache dependence — from reference to reference. An important effect of this observation is that variable uses as well as variable assignment

<sup>&</sup>lt;sup>1</sup>Randy Allen developed PFC's separability test after studying Lamport's paper on Parallel Execution of Do-Loops [Lam74]

|  |   |  | · |     |

|--|---|--|---|-----|

|  |   |  |   |     |

|  |   |  |   | •.  |

|  |   |  |   | ÷ _ |

|  | • |  |   |     |

become "kills", where a kill terminates all outstanding dependences. Hence, there may be many fewer cache dependences than data dependences.

To see the difference between the two graphs, observe that the following code fragment has six data dependences and only three cache dependences.

$$(S_1)$$

$A = ...$   $(S_2)$   $... = A$   $ENDDO$

The six data dependences in this loop are from  $S_1$  to itself and to  $S_2$  and to  $S_3$ , from  $S_2$  to  $S_3$  and  $S_1$ , and from  $S_3$  to  $S_1$ . At times during the execution of a transforming compiler, the transitive closure of the data dependence graph is required. Many transforming compilers will actually produce all nine dependences from this code fragment. Since transitive cache dependences are not used anywhere, the aggressive use of kill sites is encouraged for cache dependence analysis. Aggressive use of kill sites reduces the cache dependences for this code fragment to three: (1) a loop independent true edge between  $S_1$  and  $S_2$ , (2) a loop independent input edge between  $S_2$  and  $S_3$ , and (3) a loop carried anti edge between  $S_3$  and  $S_1$ . Eliminating half of the dependences can be significant when algorithm running times depend directly on the number of edges in the graph.

## 1.2.4 LC(x) and D(x)

During computation of the overflow iteration, it will be convenient to blur the distinction between loop carried and loop independent dependences. To avoid having to handle the dependences separately, two functions will be used: Loop Carried By, LC(e) and Distance, D(e). The values of both of these functions are obvious for loop carried dependences. LC(e) is the loop level that carries the distance, and D(e) is the value of the distance vector at that level. LC(e) for a loop independent dependence edge is the minimum nesting level of any statement between the source and the sink of the edge, including the endpoints. The distance D(e) of a loop independent dependence is always 0.

When trying to determine the amount of memory used by a program segment, a dependence edge that does not have both of its endpoints within the segment should

not be considered. For loop carried dependences, the endpoints are contained in the segment if the edge is carried by a loop in the segment. For a loop independent edge, the edge is considered when the endpoints are both within the segment. By defining LC(x) to be the nesting level of the smallest loop that includes both endpoints of a loop independent dependence, LC(x) indicates which loops are affected by an edge x.

The distance D(x) indicates how many iterations of a loop must occur before the dependence can be satisfied. It is correct to set D(x) to 0 for loop independent edges, since the loop control structure will not execute between the source and the sink of the dependence.

# 1.2.5 Uniformly Generated Dependences

The dependence graph is made up of edges indicating where dependences may exist. When we are trying to compute how much memory is used by a loop, the dependences that prevent new data from being used are those that actually exist. Must dependences would provide better information about which references require additional data to be used in a program segment. Although transformations need to guarantee that all possible dependences are maintained, when considering memory performance, inaccuracies cause only sub-optimal performance, not incorrect performance. If the may edges were included when the overflow iteration was computed, each loop would be predicted to use less memory during execution. If a program was tuned using a low estimate of the amount of data required, the actual usage would cause misses. If a high estimate is used, the actual usage would fit into a smaller cache, just wasting some of the available space. Accurate estimates will allow better tuning, minimizing the misses for a given memory size.

Gannon, Jalby, and Gallivan [GJG87] defined a uniformly generated dependence as a dependence between two references for which a distance vector exists and each element is known (not symbolic).

If two references have a known distance vector between them, then the compiler has determined that the two references will touch the same memory location. A uniformly generated dependence separates two references that must access the same location during execution. Uniformly generated dependences fit neatly into the idea of must dependences. Many other dependences, such as those due to different symbolic

subscripts or index arrays, will rarely or never access the same location. No other well-defined class of dependences definitely uses the same memory location at both ends every time the ends are executed.

May dependences are ignored due to the manner in which the overflow iterations are calculated. For each reference in a loop, the dependence graph is used to determine whether the reference has been used previously in the loop. If a must dependence exists (and the execution path between the two statements occurs), then the sink will not use a "new" storage location. The assumption is that may dependences will, in actuality, rarely use the same memory locations. If the statements rarely use the same location, then the sink of the dependence will use a "new" storage location. Because the overflow iteration should overestimate the amount of memory used, rather than underestimate, only must dependences are considered. For the purposes of computing the overflow iteration of a loop, any dependence that is not uniformly generated is ignored.

#### 1.3 Previous Work

The previous work fits into two basic categories: cache performance studies and attempts to improve memory performance. Previous cache performance studies have used short traces; a method to trace the cache performance of complete programs is presented in this work. The basic difference between the methods to improve memory performance described in this dissertation and previous work, is our attempt to make the best use of a fixed size memory rather than attempting to minimize the set of active locations.

#### 1.3.1 Cache Performance Studies

The best known cache performance study is by Alan Smith [Smi82]. He measured the performance of a combined instruction and data cache on 19 program address traces (3 PDP-11 and 16 IBM 360/370). The traces were split into groups of four. A cache simulation run switched between traces in a group every 10,000 references to model multiprogramming, until each trace had supplied 250,000 references. The traces varied from a text editor written in C to the COBOL compiler and an APL plotting program. Seven of the programs were written in various dialects of FORTRAN. This set of programs was meant to model a general purpose educational workload. The

programs were not CPU intensive and did not have large data requirements. A 32K cache produced a 98+% hit ratio for every program measured.

Smith made a number of statements about cache performance. He stated that a hardware prefetching mechanism was effective for all tested programs. Set associativity above 8 produced very little benefit. Optimal line size was between 64 and 256 bytes. LRU was on average 12% more effective than FIFO. There was no clear performance difference between the write-back and write-through policies [Smi82].

In 1985, Smith conducted a detailed examination of hardware prefetching[Smi85b]. In this study, 49 traces from 6 architectures and 7 languages were used. Again, the traces were short (two 500K and the rest 250K or shorter). Only three programs accessed over 100,000 bytes of virtual storage during the traces. It was noticed that the various machines and compilers had different instruction fetch and data write percentages. Smith's report indicated the need to examine a representative workload to determine the effectiveness of a cache for a particular machine.

Lee, Yew and Lawrie [LYL87b] looked at the performance considerations of caches on multiprocessors. The cache performance of 23 scientific library subroutine calls was examined. A compile time cache coherency solution prevented multiple copies of read/write data by marking them as non-cacheable references. The longest trace was about 34 million references, and the average trace was between 5 and 6 million references. They found that the optimal cache line was always less than eight words and in many cases only one or two words.

Chapter 2 discusses a cache performance study using typical supercomputer application programs as the workload. Scientific programs that run on large computers are a different type of workload than a general purpose computing workload. Before attempting to transform programs to improve performance, a study to determine the potential gains is performed. During the performance study, the differences in memory performance due to workload variation are discussed.

## 1.3.2 Improving Memory Performance

A number of researchers have improved performance at various levels of the memory hierarchy. The work has ranged from trying to lower the number of virtual page faults to eliminating extraneous uses of vector registers. The following sections are brief descriptions of the most relevant work, together with a brief discussion of their influence on and differences with the work in later chapters.

# Virtual Memory Locality

Abu-Sufah [AS79] examined the problem of reducing the number of virtual memory pages used by a program. In contrast with earlier work surveyed by Denning [Den70] and Kuck [KL70], he used data dependences as the basis of his solution. Abu-Sufah produced a general mechanism that substantially reduces virtual memory paging. His studies suggest that a transformed program can get the same performance as the original program with one-fifth to one-sixth the number of virtual memory pages.

Abu-Sufah developed a general method for measuring the space-time cost of various programs using a virtual memory page as the unit of allocation. He then examined the effects on the space-time cost of programs, of three transformations individually, and in combination. The three transformations are loop distribution to separate the program into smaller pieces, loop fusion to recombine pieces that are heavily related, and strip mining to access arrays in single page size sections.

Program transformations were very successful for Abu-Sufah in reducing each program's space-time cost. Although the criterion, space-time cost, is not useful for cache memories, the effectiveness of the transformations in tuning programs to the criterion is encouraging. The success demonstrates that transformations can be used to change global memory performance in a predictable manner.

## Cache Packing

Kalid Thabit [Tha81] examined several software methods to reduce the effective main memory access time when a cache is present. Two models for compiler control of the cache, the prompting and the explicit models, were presented. In addition to presenting these models, Thabit showed that memory allocation to make maximum use of long cache lines is equivalent to bin packing and is an NP-complete problem. Also presented is a simple data dependence test to determine whether a blocking transformation (strip mining) suggested by Abu-Sufah is safe.

The prompting model presents the compiler with two cache commands, Prompt and Release. Prompt allocates a memory block in the cache, possibly bringing data in from main memory, and Release deallocates the data block. The allocation mech-

anism is not speculative. If a block is requested, then it will be used. Since Prompts are not speculative, they cannot be moved across control dependences that may affect execution. Allowing speculative prefetching, we can move many of the prefetch commands much further from the actual uses, greatly increasing the likelihood that the prefetch completes before the value is actually required. The prompting model was presented by Thabit with no data on how effective it would be in practice.

The explicit model gives the compiler complete control of cache block allocation, cache block deallocation, and transfer of data to and from main memory. This model reduces the cache management problem to the register allocation problem (on a somewhat larger scale). There are several problems with this model. The most common solution to the register allocation problem in the literature is graph coloring [CAC+81],[Cha82]. The graph coloring solution is intractable and does not seem to be a promising method of cache management. When thousands of cache blocks exist, the coloring could take an unacceptably long time to solve. A second problem is that the control instructions would need to be inserted into the program rather than being handled by the hardware.

Thabit's model for compiler control of cache showed that some simple optimal cache allocation problems are NP-complete. Rather than look for solutions to these problems, compiler writers need to determine what cache behavior is common in actual programs and find solutions that are fast and accurate for those cases.

### Cache Locality

Gannon, Jalby and Gallivan have done the only known prior work on maximizing cache locality [GJG87]. They computed the number of active locations in an array. Transformations were then used to reduce this number and to predict a lower bound on the number of cache hits.

The general method is to define a family of "reference" windows for each variable. A reference window defines the current set of elements that must be in the cache (i.e., those that will be used again). A reference window is defined for each dependence and specifies the set of elements used at the source before some time t that are also used at the sink after time t.

To define these windows accurately, several common subcases of data dependences are defined. The most important is when a dependence distance vector can be de-

termined exactly and consists of constants. This is called a uniformly generated dependence. It is simple to compute the window size of a uniformly generated dependence. In general, the window will be one larger than the number of iterations necessary to carry the dependence. For example, a loop independent dependence has a distance vector of all zeros and a window size of one. A uniformly generated loop carried dependence with a distance of three has a window size of four elements.

The hit ratio can be calculated by determining a spanning dependence for each variable and then counting the number of references inside the spanning window and the number of different locations accessed by the spanning dependence. The hit ratio is then the number of references minus the number of different locations divided by the number of references. This is a program constant and cannot be changed with safe transformations. Gannon et.al. attempted to minimize the maximum sum of active windows in the program.

A major difference between Gannon's methods and the methods proposed in this dissertation is our emphasis on the loop that does not fit into the cache. Cache management is not an absolute; there is a trade-off between compile time and execution time. Under the approach in this dissertation, it is possible to identify when the program fits into available cache such that there is no need to further improve the program.

This dissertation uses Gannon's definition of uniformly generated dependences to describe dependences that must reuse a memory location. Dependence graphs include edges that either can not be disproved or are known to occur only occasionally. When determining whether a memory location resides in cache when referenced, the only edges of interest are those that actually occur. Uniformly generated dependences capture this idea very cleanly.

### Vector Register Allocation

Allen and Kennedy [AK88] studied methods to section vector loops when the number of loop iterations exceeds the vector pipe length. Assuming a vector pipe of 64 elements (CRAY-1, CRAY-XMP) and a 100 element vector operation, the naive solution of executing the first 64 as one operation and the last 36 as a second operation may produce incorrect results. The simple solution of using temporary storage to

guarantee that the correct values are always used can use a tremendous amount of storage.

Allen and Kennedy use the data dependence graph to determine when simple sectioning produces potentially incorrect results. A number of program transformations such as, loop reversal, input prefetching, loop splitting, loop interchange, and loop fusion can be used to produce correct results without using temporary storage. The circumstances under which each transformation is safe and effective were described.

Register allocation optimizes the performance of a small explicitly controlled set of locations. The compiler knows the contents of each register at all times. Maintaining this level of information about cache and virtual memories would be very expensive due to the large number of cache locations and the nonlinear complexity of register allocation methods. To improve cache performance, methods that do not track every cache location are needed. Fortunately, cache misses are not catastrophic errors. If a register does not have the expected contents, then the program is incorrect. If the cache does not have the expected value, then the result is a cache miss. Thus, a probabilistic solution can be used.

Allen and Kennedy have shown the effectiveness of program transformations for improving memory access patterns. Vector register allocation deals with specifically allocated memory, but the specific transformations to shorten dependences between references that use the same memory locations could be effective for cache management if applied properly.

## Cache Prefetching

Lee, Yew and Lawrie have studied data prefetching for shared-memory multiprocessors [LYL87a], [LYL87b]. Working on the Cedar project with software-enforced cache coherency, they found that data prefetching was effective in addressing the memory access bottleneck. Their view of data prefetching initiates operand fetches several instructions beyond the current processor instruction.

Data prefetching does not address the problem of saturating the memory bandwidth, but it does attempt to overlap the memory latency with execution. They report that prefetching obviates the performance advantage of long cache lines. Since multiprocessor interconnection strategies may have limited-width data paths, using

shorter cache lines can reduce the average memory latency. They hypothesized that with data prefetching, shorter cache lines will perform better for multiprocessors.

Lee et. al.[LYL87a] showed that low level prefetching can be effective. In general, prefetches into registers can not be separated from the use of the register by more than a few instructions, since a register must be allocated during the prefetching. If prefetching is separated from register loads, the prefetch can be moved further away from the actual load, allowing a larger overlap of memory latency and computation time. The success of overlapping data fetches at the low level indicates that more aggressive prefetching may be able to almost completely overlap memory latency delays with execution.

#### Blocking

Two recent papers have reported on computer programs whose performance displayed noticeable sensitivity to problem size when running on vector or parallel processors. Vector performance of an Alliant FX/1 fell by as much as 60% when the vector lengths were greater than the length that could be maintained in the cache [ASM86]. IBM 3090 performance fell by 30% when the arrays of a matrix multiplication were larger than the cache size [LS88]. In both reports, it was noted that performance did not degrade when accesses were blocked into groups smaller than the cache size.

Blocking data accesses to improve the performance of a processor (particularly parallel processors) is a well-known technique. Gallivan, Jalby, Meier and Sameh [GJMS88] discussed the performance of blocked BLAS3 linear algebra routines on an Alliant and found that blocked versions generated twice the MFLOPs for some array sizes. For tridiagonal linear equations, Berry and Sameh [BS88] improved the performance by blocked LU decomposition over the standard LINPACK version[DMBS79] by as much as 800%. On a Cray-2, unrolling the inner loop improved performance by a factor of three, and a blocked assembly program increased performance by a factor of six for large arrays [Cal86].

In these studies, programmers were either blocking the programs by hand, [LS88], or providing library routines that have been blocked by hand (eg. BLAS3 [GJMS88]). Although both of these methods are effective, it is desirable to automate the blocking of data. Any machine dependent function that the compiler can perform simplifies a programmer's job and makes the programs easier to port to new machines. When

the compiler performs the blocking, it does not obscure the programmer's view of the program, and the blocking is ensured to be performed correctly. This will eliminate some errors and make others easier to locate. When the programmer is blocking array accesses by hand, some estimate of the potential benefit is weighed against the demands on his time. If the gains are small or difficult to determine, blocking is not done. By spending some compilation time to block memory accesses, any program that benefits from blocking is blocked.

When code is blocked by hand, the program should be retuned every time the memory hierarchy changes. This includes moving between manufacturers, moving between computer models from one company and, in some instances, moving between different versions of the same computer. Automatic blocking can tune code to a particular memory hierarchy by simply recompiling.

The first step towards automatic methods of increasing memory performance is understanding how typical memories perform on real programs. The performance of caches on computationally intensive programs has not been thoroughly studied. Before it is possible to start optimizing programs to run on parallel processors with multiple caches or multiple levels of cache, a firm understanding of how a single cache and processor interact is required. This dissertation attempts to understand how computationally intensive programs run on sequential caches and investigates how to improve their performance. Both software and hardware mechanisms for improving performance are considered.

Chapter 2 describes a tool to measure very long cache traces and uses it to measure the performance of a group of supercomputer application programs. The next chapter presents a static model of the dynamic memory behavior. Program transformations to improve a program's memory performance are discussed in Chapter 4. For those cases where transformations are ineffective at eliminating cache misses, Chapter 5 examines a simple method of overlapping cache misses with other computation.

# Chapter 2

# Data Cache Performance

#### 2.1 Introduction

This chapter describes an experimental study of a wide variety of programs and caches to determine how various memory structures perform for computationally intensive programs. Hardware designers can use this study to help make design decisions for super and super-mini computers. Chapters 4 and 5 will use the tools built for cache simulation and observations of programs with poor cache performance to examine methods for improving the cache performance during compilation.

Recent studies at the University of Illinois and IBM have shown that memory performance can have a significant impact on the overall performance of a computer. Abu-Sufah and Maloney measured the vector performance of an Alliant FX/8 on increasing vector lengths and found that when the vectors exceeded the cache size, the performance declined by up to 60% [ASM86]. In similar work, Liu and Strother found that a matrix multiply problem that did not fit in the cache ran 30% slower on an IBM 3090 vector processor than when the problem did fit into the cache [LS88]. Both reports recognized the problem as a memory performance problem and suggested methods to improve overall performance by improving the cache hit ratios of the programs.

In both studies, the test programs were quite simple, namely, a program with very long vector operations, and a single matrix multiplication problem. While these are certainly subroutines that will be called by programs running on supercomputers, they will not normally be programs by themselves. However, actual production codes tend to be computationally intensive and thousands of lines long.

In the past, cache performance studies have not examined the class of computationally intensive programs. There are two reasons: (1) there is no commonly acknowledged benchmark, and (2) tracing simulations of long programs requires too much storage. Studies such as those done by Alan Smith [Smi82], [Smi85a] use trace

lengths from 10,000 to 333,000 entries. These traces correspond to fractions of a second of execution time for powerful machines. However, traces of this length are used for several reasons. First, the storage required to keep a trace that would correspond to minutes or hours of execution is not available. Second, most cache studies have been directed toward time-sharing systems that will swap the program out to disk after a small time-slice, effectively flushing the cache about every 10,000 accesses. Other studies have used whole programs, but the relationship between these programs and actual supercomputer applications is unknown. Chi and Dietz, [CD89] are looking at the performance of a class of caches. They use full programs such as bubble sort, puzzle, and tower of Hanoi for their study, but the performance of these programs does not necessarily correspond to the performance of supercomputer applications.

The cache studies have focused on cache performance and have paid little attention to the relationship between misses in the cache and the program that is executing. Before the compiler can attempt to improve memory performance, an understanding of the behavior of each reference in the source program is required. To determine the performance of individual references during execution of long programs, we developed a new simulation tool called PFC-Sim.

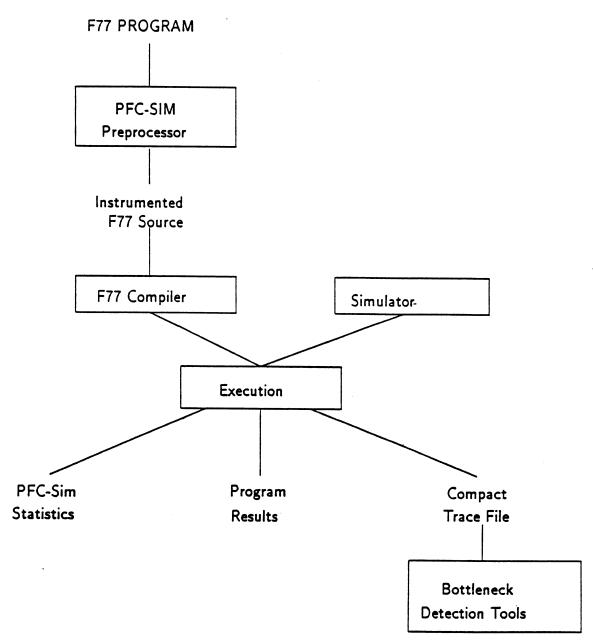

PFC-Sim is a program-event-driven tracing facility which can be modified to perform a variety of dynamic statistic-gathering tasks. The version used in this dissertation gathers information about memory performance in terms of hits, misses and traffic. Another version counts floating point operations and dynamic vectorization percentage. All versions of PFC-Sim have the same basic structure (see Figure 2.1) including a preprocessor that locates interesting events in the source program and inserts code that invokes a run-time simulator, run-time routines to simulate some functions or just record the events, and visualization tools to make the dynamic statistics easier to understand. For memory simulation, every data reference in the program is preceded by a call to the cache simulator. To simulate execution time, every basic block has a statement that increments the simulated clock by the execution time required for a single execution of the block.

Very long programs can be simulated by PFC-Sim since trace entries produced by a program are discarded as soon as the simulator processes them. In this manner, simulations of any length can be run without concern for disk space. The translation process that marks events in the source gives each event a unique number. By passing

Figure 2.1 PFC-Sim

that number to the simulator, separate statistics for each event are maintained. When execution completes, the statistics about the entire program can be gathered, or subsets (i.e., single loops or individual references) can be examined.

To understand supercomputer program memory performance, a collection of actual production programs is required. Researchers at Rice University are collecting a set of computationally intensive programs known as the Rice Compiler Evaluation Program Suite (RiCEPS). Each program in the suite is written in FORTRAN77 and includes the data required for execution. Each program is either an actual production program or an "abstracted" version, where "abstracting" involves replacing proprietary routines with computationally-similar, non-proprietary versions of those routines. The execution times of the programs vary from less than one minute to several days on an IBM 3081D. As a collection of production supercomputer programs, the benchmark gives a much better idea of the supercomputer run-time performance than programs used in previous studies.

As describe in Chapter 1, a cache can be specified by a number of parameters: cache size, cache line (or block) size, replacement policy, write policy, degree of associativity, and whether it employs a prefetching mechanism. To understand the effects of these parameters, each program in RiCEPS was run with a variety of cache structures. The structures were chosen to allow each parameter to be investigated separately. Each series of simulations was run for each parameter. The series involved changing the parameter while holding all other parameters constant.

The simulations provide two basic types of information about whole programs: the hit ratio and the amount of memory traffic generated. To better understand the results of each design decision, each parameter's effect on these values was determined. Trends among the programs was examined as well as individual programs that do not follow the trends. To reduce the number of misses in a program, the compiler must locate the misses. By counting misses and hits for each reference, the hit ratio for each individual reference was determined.

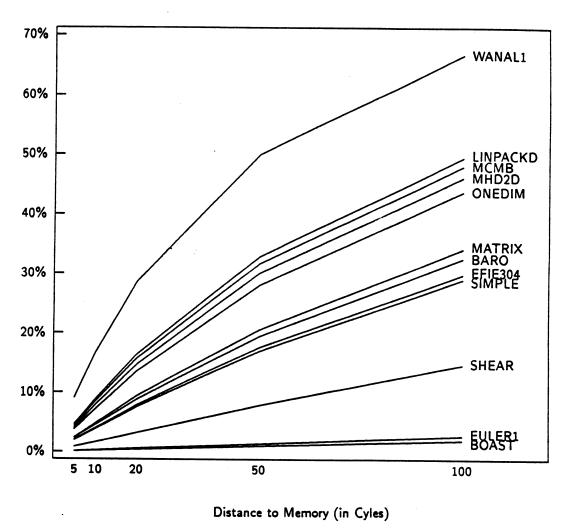

Cache performance effects on program execution can also be realized from the information produced by PFC-Sim. Using the estimated execution time and the number of misses during the program, the percentage of execution time spent waiting for the memory can be determined. As supercomputers get faster and more distant (in cycles) from their main memories, this can become a pronounced performance

problem. The second impact of cache performance is the amount of traffic generated to support the execution. Most modern supercomputers have found it difficult to provide enough bandwidth to keep the floating point units running at peak rates. By investigating the average amount of bandwidth required for each floating point operation, a measure of the peak effective MFLOP rate for a machine was determined.

The following two sections detail the tools used for the data cache performance studies. The programs that presently comprise RiCEPS are described. Then, PFC-Sim's design and implementation is discussed. Using the results of the experimental study, the effects of various cache design decisions on actual program performance are then discussed.

# 2.2 Rice Compiler Evaluation Program Suite

The Rice Computer Evaluation Program Suite (RiCEPS) is being gathered to address the lack of a publicly accessible set of computationally intensive programs. RiCEPS is a group of programs culled from production supercomputers. Each program was selected to be representative of a group of applications. The programs are substantial in size and require a significant amount of execution time. Where possible, programs that took too long have been shortened. One method used to shorten programs is to reduce the length of time being simulated (from 12 hours to 10 minutes in the case of the BARO test program). In some cases, this has lowered the total execution time on an IBM 3081D from a projected 10 days to about 3 hours. A wave analysis program (WANAL1), which iteratively finds better answers, had the number of iterations reduced from 200 to 3 (shortening the execution time from 67 hours to 80 minutes).

Work on the benchmark set is progressing in parallel with this thesis. The benchmark is expected to grow to about twenty programs by early 1989. When the benchmark programs are considered stable, the intention is to make them available through Argonne National Laboratory's netlib facility. Each program in the benchmark includes, in addition to the FORTRAN program, a brief description of what the code does (what it solves/what algorithms it uses) and at least one set of data to run the program. Some of the programs generate their own data and do not use any explicit data sets.

The experiments reported later in this chapter used a preliminary version of the benchmark containing twelve programs. Many of these programs will not be present in the final benchmark for a variety of reasons. In some cases, we do not have permission to redistribute. In other cases, we may find that a code that arrives later is more representative of programs for that class of computationally intensive problems. The programs' execution times range from one minute (MATRIX) to several hours (SIMPLE, BARO, BOAST). While most programs are 1 to 3 thousand lines, they range in size from 15 lines to over 23,000 lines. All of the programs run under the IBM VS2 FORTRAN compiler on an IBM 3081D.

The benchmark programs used for this work included:

- MCMB a mixed characteristic microbial biodegradation program. Concentration is solved by continuous linears in space. Backward differencing in time is treated by segmented characteristics. Preconditioned conjugate gradient iterations are used to solve matrices for both concentration and pressure.

- MATRIX a simple 100 x 100 matrix multiply.

- BARO weather simulation of an isolated vortex embedded in a mean westerly flow. It uses a shallow water atmospheric model with a fourth order potential entropy conserving advection scheme and leapfrog differencing.

- SIMPLE an abstracted hydrodynamics program produced by Livermore National Laboratory for distribution and tests.

- EFIE304 calculates the current distribution on an arbitrary body excited by a plane wave of desired amplitude H-Field. The program manipulates the given data to obtain triangular patches. Current density is calculated at the center of each edge.

- BOAST a black oil reservoir simulator.

- EULER1 a solver for one dimensional unsteady Euler equations that utilizes spectral methods: collocation method with Chebyshev series, 1D propagating shock wave, bursting diaphragm flow, and colliding shock wave flows.

- SHEAR three dimensional turbulent fluid dynamics simulation based on spectral techniques.

- MHD2D solves 2D MHD equations with periodic boundary conditions on a 256 x 256 grid using the spectral method and leapfrog time differencing.

- ONEDIM eigenfunctions and eigenvalues of the time independent Schroedinger equation for one dimensional potential.

- LINPACKD benchmark that has been used to determine the floating point performance of the most recent computer/compiler combinations on double precision LINPACK calls. [Don88]

- WANAL1 boundary control of wave equations by conjugate gradient method, without initial data smoothing using a perturbed bilinear form without cutting.

#### 2.3 PFC-Sim

PFC-Sim is a program-driven-event tracing facility consisting of three parts: a preprocessor, run-time routines. and visualization tools written for this research (see Figure 2.1). To fulfill the requirements of this research, PFC-Sim needs to run on long programs in a limited amount of space and needs to create a map between actions in the trace and the corresponding events in the source program. To eliminate the need for an enormous trace file, the simulation of memory occurs during program execution. Unique marking of each event in the program source allows a simple mapping between the source program and actions during execution.

A one hour program can access the cache billions of times. Even with very small trace entries, this would easily exceed the available disk storage. In a typical tracing simulation, a single execution of the program is traced, the trace file is compacted in some manner, and then many simulations are run on the resulting compacted trace file. Since PFC-Sim runs on programs where the original trace file is too long to store, the compaction and simulation steps run concurrently with the program being traced, eliminating the need to ever write the trace entries. This requires retracing of the entire program for every different memory simulation, but since at least 90 percent of the execution time is in the simulation routines, the cost of re-executing the program is not prohibitive.

Only computing the hit ratio of a program does not aid a programmer in determining whether a particular section of code is getting adequate memory performance.

To improve a program's memory performance, some means of determining the reference or set of references causing the majority of the misses is needed. If memory accesses are determined by looking at the assembly code produced by the program, it will be very difficult (particularly if the code is optimized) to determine to which source statement a particular load corresponds. By marking loads and stores in the program source, PFC-Sim has several advantages. The mapping between events and source program statements is simple; every event is given a unique number.