# REWRITING X86 BINARIES WITHOUT CODE PRODUCER COOPERATION

by

Richard Wartell

| APPROVED BY SUPERVISORY COMMITTEE: |

|------------------------------------|

|                                    |

|                                    |

| Dr. Kevin Hamlen, Chair            |

|                                    |

|                                    |

| Dr. Gopal Gupta                    |

|                                    |

|                                    |

| Dr. Murat Kantarcioglu             |

|                                    |

|                                    |

| Dr. Zhiqiang Lin                   |

Copyright © 2012

Richard Wartell

All rights reserved

Dedicated to my parents,

for their unending support.

And my brother,

for his inspiration and honesty.

# REWRITING X86 BINARIES WITHOUT CODE PRODUCER COOPERATION

by

RICHARD WARTELL, B.S.

# DISSERTATION

Presented to the Faculty of

The University of Texas at Dallas

in Partial Fulfillment

of the Requirements

for the Degree of

DOCTOR OF PHILOSOPHY IN COMPUTER SCIENCE

#### ACKNOWLEDGMENTS

The author is incredibly grateful for the opportunity to work under his advisor, Dr. Kevin Hamlen, who was thoroughly helpful in building the foundation of the author's knowledge necessary to complete this dissertation and inspiring a thirst for knowledge and creativity. His patient and humble approach to teaching and direction were crucial in the author's research and the completion of this work.

This research would never have been accomplished without the help of the author's colleague, Vishwath Mohan. His willingness to act as a sounding board for ideas and helpfulness in working on certain pieces of this work were crucial in its completion. Special thanks should also be given to Dr. Yan Zhou whose work in Machine Learning and collaboration on disassembly projects was unendingly helpful to the author. Special mention should also be given to Dr. Zhiqiang Lin for his contributions and ideas that extended the author's research. Meera Sridhar should also be thanked for her work ethic and contribution to the work on rewriter transparency. Finally, thanks should also be given to the work done by Dr. Micah Jones and Dr. Murat Kantarcioglu whose work is closely tied to this dissertation.

This research was supported in part by Air Force Office of Scientific Research awards FA9550-08-1-0044 and FA9550-10-1-0088, and National Science Foundation award #1054629. All opinions expressed are those of the authors and do not necessarily reflect those of the AFOSR or NSF.

The author extends his heartfelt thanks Dr. Mikhail Atallah who was the original inspiration for this author's interest in security. Additionally, the author would like to thank Matt White who was this author's original collaborator, inspiration, and good friend. Finally, the author

wishes to thank Nate Gatchell, whose friendship, support, and unending spirit and swagger were a constant inspiration.

November 2012

#### **PREFACE**

This dissertation was produced in accordance with guidelines which permit the inclusion as part of the dissertation the text of an original paper or papers submitted for publication. The dissertation must still conform to all other requirements explained in the "Guide for the Preparation of Master's Theses and Doctoral Dissertations at The University of Texas at Dallas." It must include a comprehensive abstract, a full introduction and literature review, and a final overall conclusion. Additional material (procedural and design data as well as descriptions of equipment) must be provided in sufficient detail to allow a clear and precise judgment to be made of the importance and originality of the research reported.

It is acceptable for this dissertation to include as chapters authentic copies of papers already published, provided these meet type size, margin, and legibility requirements. In such cases, connecting texts which provide logical bridges between different manuscripts are mandatory. Where the student is not the sole author of a manuscript, the student is required to make an explicit statement in the introductory material to that manuscript describing the student's contribution to the work and acknowledging the contribution of the other author(s). The signatures of the Supervising Committee which precede all other material in the dissertation attest to the accuracy of this statement.

REWRITING X86 BINARIES WITHOUT

CODE PRODUCER COOPERATION

Publication No. \_\_\_\_\_

Richard Wartell, Ph.D.

The University of Texas at Dallas, 2012

Supervising Professor: Dr. Kevin Hamlen

Binary code from untrusted sources remains one of the primary vehicles for software propa-

gation and malicious software attacks. All previous work to mitigate such attacks requires

code-producer cooperation, has significant deployment issues, or incurs a high performance

penalty. The problem of accurate static x86 disassembly without metadata is provably

undecidable, and is regarded by many as uncircumventable.

This dissertation presents a framework for x86 binary rewriting that requires no cooperation

from code-producers in the form of source code or debugging symbols, requires no client-side

support infrastructure (e.g., a virtual machine or hypervisor), and preserves the behavior of

even complex, event-driven, x86 native COTS binaries generated by aggressively optimizing

compilers. This makes it exceptionally easy to deploy. The framework is instantiated as

two software security systems: Stir, a runtime basic block randomization rewriter for

Return-oriented programming (ROP) attack mitigation, and REINS, a machine verifiable

Software Fault Isolation (SFI) and security policy specification rewriter. Both systems exhibit

extremely low performance overheads in experiments on real-world COTS software— 1.6%

viii

and 2.4% respectively. The foundation of the system includes three novel approaches to static x86 disassembly, along with a method of statically proving transparency for rewriting systems.

# TABLE OF CONTENTS

| ACKNO  | WLED    | OGMENTS                           | V          |

|--------|---------|-----------------------------------|------------|

| PREFA  | CE .    |                                   | ⁄ii        |

| ABSTR  | ACT     |                                   | iii        |

| TABLE  | OF CO   | ONTENTS                           | Х          |

| LIST O | F TAB   | LES                               | iii        |

| LIST O | F FIGU  | JRES                              | iv         |

| СНАРТ  | ER 1    | INTRODUCTION                      | 1          |

| СНАРТ  | ER 2    | STATIC X86 DISASSEMBLY            | 7          |

| 2.1    | Challe  | nges                              | 8          |

| 2.2    | Curren  | at x86 Disassembly                | 12         |

| 2.3    | Shingle | ed Disassembly                    | 16         |

| 2.4    | Machin  | ne Learning Disassembly Model     | 20         |

|        | 2.4.1   | Design                            | 22         |

|        | 2.4.2   | Evaluation                        | 28         |

| 2.5    | Graph   | Based Disassembly Model           | 34         |

|        | 2.5.1   | Design                            | 35         |

|        | 2.5.2   | Shingled Disassembler             | 36         |

|        | 2.5.3   | Opcode State Machine              | 36         |

|        | 2.5.4   | Maximum-Likelihood Execution Path | 37         |

|        | 2.5.5   | Algorithm Analysis                | <b>4</b> C |

|        | 2.5.6   | Evaluation                        | <b>4</b> C |

|        | 2.5.7   | Broad Results                     | <b>4</b> C |

|        | 2.5.8   | eMule Case Study                  | 43         |

| СНАРТ | TER 3  | X86 BINARY REWRITING              | 47  |

|-------|--------|-----------------------------------|-----|

| 3.1   | Rewrit | ring Challenges                   | 47  |

|       | 3.1.1  | Accurate Disassembly              | 48  |

|       | 3.1.2  | Where to rewrite?                 | 49  |

|       | 3.1.3  | Control Flow Instructions         | 51  |

|       | 3.1.4  | Hijacking System Calls            | 54  |

| 3.2   | STIR   |                                   | 57  |

|       | 3.2.1  | ROP Protection                    | 58  |

|       | 3.2.2  | Design                            | 60  |

|       | 3.2.3  | Evaluation                        | 70  |

| 3.3   | Reins  |                                   | 78  |

|       | 3.3.1  | Overview                          | 78  |

|       | 3.3.2  | Control-flow Safety               | 83  |

|       | 3.3.3  | Policy Specification              | 89  |

|       | 3.3.4  | Verification                      | 92  |

|       | 3.3.5  | Evaluation                        | 93  |

|       | 3.3.6  | Case Studies                      | 98  |

| 3.4   | Interm | nediary Library                   | 101 |

|       | 3.4.1  | Callback Handling                 | 101 |

|       | 3.4.2  | Dynamic Library Loading           | 106 |

|       | 3.4.3  | Policy Implementation             | 109 |

| СНАРТ | ER 4   | REWRITER TRANSPARENCY             | 112 |

| 4.1   | Action | Script Byte Code                  | 113 |

| 4.2   | IRM T  | Transparency                      | 114 |

| 4.3   | Transp | parency Verification Design       | 118 |

|       | 4.3.1  | ActionScript Bytecode Core Subset | 118 |

|       | 4.3.2  | Concrete and Abstract Machines    | 119 |

|       | 4.3.3  | Verification Algorithm            | 122 |

|       | 4.3.4  | Model-Checking                    | 125 |

|       | 4.3.5  | Invariant Generation                             | 27 |

|-------|--------|--------------------------------------------------|----|

|       | 4.3.6  | A Verification Example                           | 29 |

| 4.4   | Evalua | ation                                            | 31 |

| 4.5   | Transp | parency for x86 Rewriters                        | 35 |

| СНАРТ | TER 5  | RELATED WORK                                     | 36 |

| 5.1   | Disass | embly                                            | 36 |

| 5.2   | Binary | Rewriting                                        | 39 |

|       | 5.2.1  | Recompilation                                    | 39 |

|       | 5.2.2  | Use of Debug Information                         | 41 |

|       | 5.2.3  | Virtual Machines                                 | 42 |

|       | 5.2.4  | Restrictionless Binary Rewriting                 | 43 |

| 5.3   | Transp | parency                                          | 14 |

| СНАРТ | TER 6  | CONCLUSION                                       | 45 |

| REFER | ENCES  | $5 \ldots \ldots \ldots \ldots \ldots \ldots 14$ | 18 |

| VITA  |        |                                                  |    |

# LIST OF TABLES

| 2.1  | x86 Instruction Aliasing                                                    | 7   |

|------|-----------------------------------------------------------------------------|-----|

| 2.2  | Indirect Branch Types                                                       | 11  |

| 2.3  | Disassembly Techniques                                                      | 13  |

| 2.4  | Statistics of IDA Pro 5.5 disassembly errors                                | 16  |

| 2.5  | Programs tested with PPM Disassembler                                       | 28  |

| 2.6  | Tagging accuracy                                                            | 30  |

| 2.7  | A comparison of mistakes made by IDA Pro and by our disassembler            | 30  |

| 2.8  | Disassembly discrepancies between IDA Pro and our disassembler for eMule $$ | 32  |

| 2.9  | File Statistics                                                             | 41  |

| 2.10 | Disassembly Comparison for eMule.exe                                        | 45  |

| 3.1  | Inplace Binary rewriting                                                    | 49  |

| 3.2  | Pinhole Rewriter                                                            | 50  |

| 3.3  | Direct Jump Modification Example                                            | 52  |

| 3.4  | Summary of x86 code transformations                                         | 53  |

| 3.5  | Summary of x86 code transformations                                         | 57  |

| 3.6  | Linux test programs grouped by type and size                                | 71  |

| 3.7  | STIR Binary size overheads                                                  | 79  |

| 3.8  | Summary of x86 code transformations                                         | 86  |

| 3.9  | Experimental results: SPEC benchmarks                                       | 95  |

| 3.10 | Experimental results: Applications and malware                              | 96  |

| 3.11 | Callback Trampoline Chunk Redirection                                       | 104 |

| 4.1  | Experimental Results                                                        | 133 |

# LIST OF FIGURES

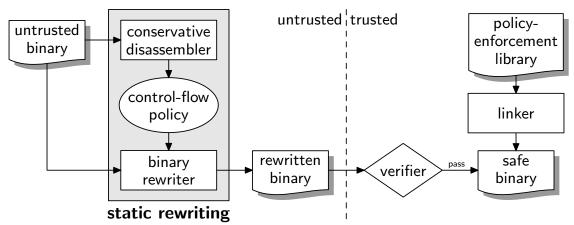

| 1.1  | The process of rewriting an unsafe binary                                 | 4  |

|------|---------------------------------------------------------------------------|----|

| 2.1  | The x86 machine instruction format                                        | 9  |

| 2.2  | The Java bytecode instruction format                                      | 10 |

| 2.3  | Java Disassembly vs. x86 Disassembly                                      | 12 |

| 2.4  | Shingled disassemblies of a given binary                                  | 19 |

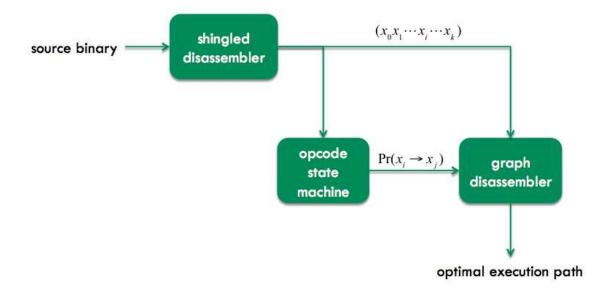

| 2.5  | Disassembler Architecture                                                 | 35 |

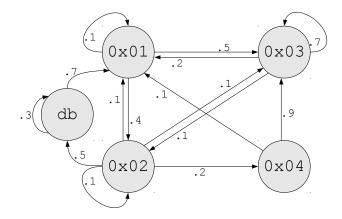

| 2.6  | Instruction Transition Graph: 4 opcodes                                   | 37 |

| 2.7  | Graph disassembly for a shingled binary                                   | 38 |

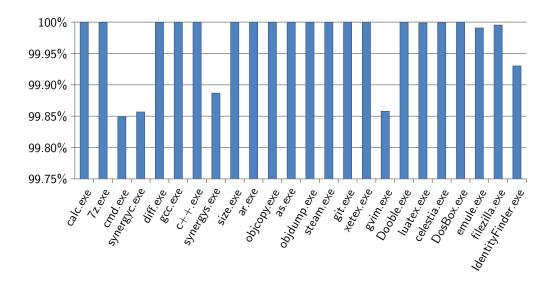

| 2.8  | Percent of instructions identified by IDA Pro as well as our disassembler | 42 |

| 2.9  | Percent of addresses sheered during shingled disassembly                  | 42 |

| 2.10 | Disassembly time vs. IDA Pro                                              | 43 |

| 3.1  | Rewriting a register-indirect system call                                 | 55 |

| 3.2  | Rewriting code that uses a jump table                                     | 55 |

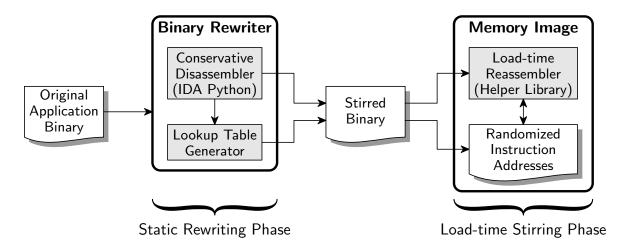

| 3.3  | System architecture                                                       | 60 |

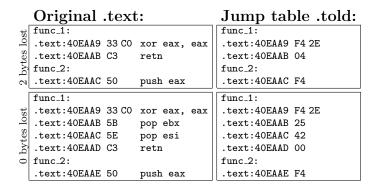

| 3.4  | A stirring example                                                        | 66 |

| 3.5  | Position-independent code                                                 | 68 |

| 3.6  | Overlapping function pointers                                             | 69 |

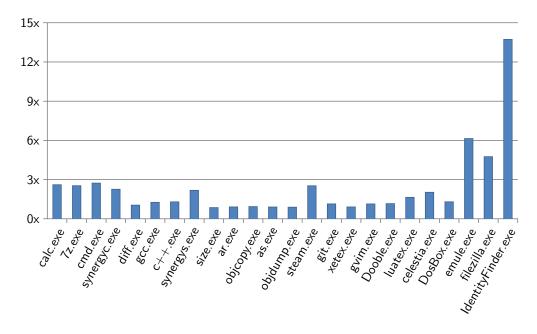

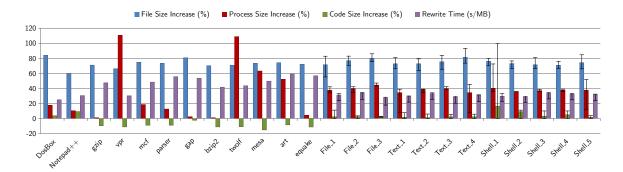

| 3.7  | Static rewriting times and size increases                                 | 71 |

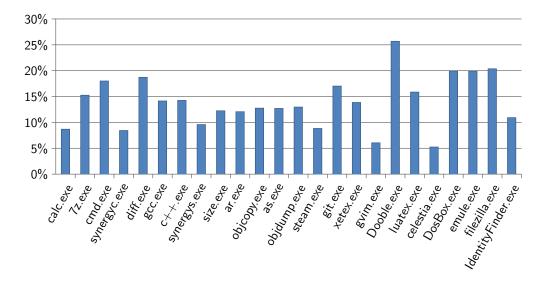

| 3.8  | Gadget reduction for Windows binaries                                     | 73 |

| 3.9  | Runtime overheads for Windows binaries                                    | 76 |

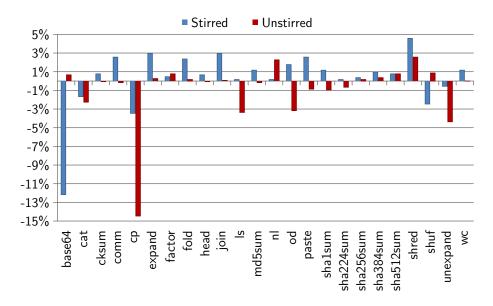

| 3.10 | Runtime overheads for Linux binaries                                      | 76 |

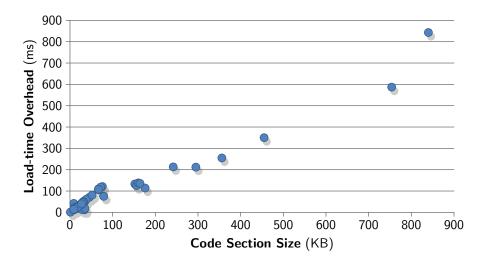

| 3.11 | Load-time overhead vs. code size                                          | 77 |

| 3.12 | Reins architecture                                                        | 83 |

| 3.13 | Reins exmaple of a register-indirect system call                          | 89 |

| 3.14 | Reins example using a jump table                                          | 90 |

| 3.15 | A policy that prohibits applications from both sending emails and creating .exe files                        | 90  |

|------|--------------------------------------------------------------------------------------------------------------|-----|

| 3.16 | Eureka email policy                                                                                          | 91  |

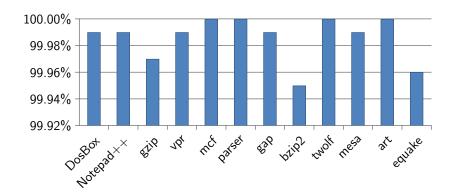

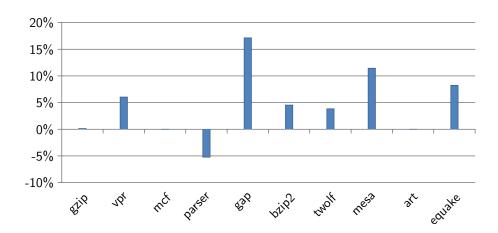

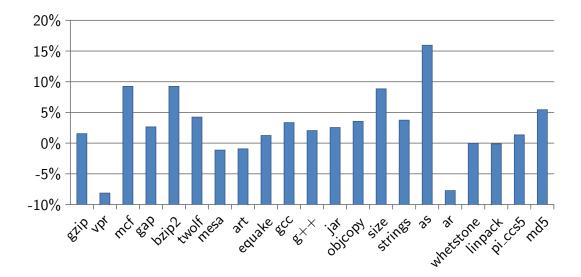

| 3.17 | Runtimes of rewritten binaries relative to originals                                                         | 98  |

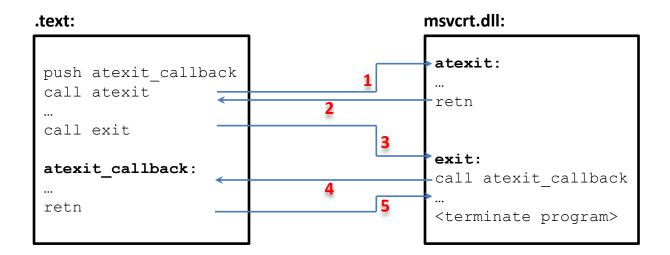

| 3.18 | Example of .atexit callback                                                                                  | 102 |

| 3.19 | Rewritten .atexit callback                                                                                   | 103 |

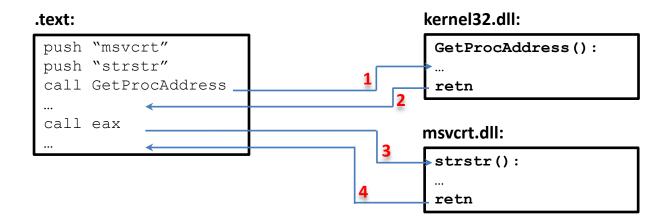

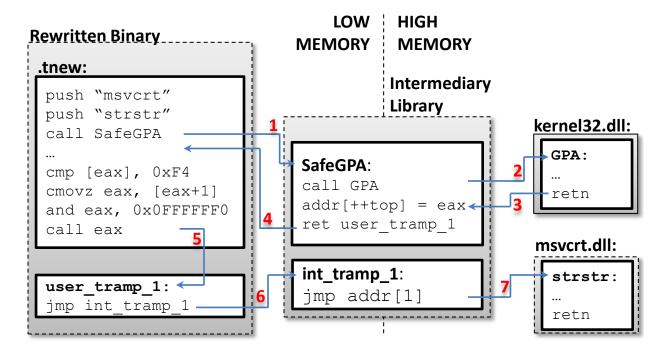

| 3.20 | $\label{eq:example_proc} Example \ of \ GetProcAddress() \ Execution \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 107 |

| 3.21 | $Rewritten\ GetProcAddress()\ Execution\ .\ .\ .\ .\ .\ .\ .$                                                | 108 |

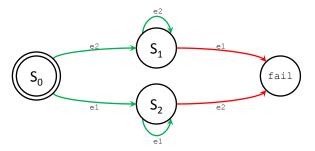

| 3.22 | Policy DFA Example                                                                                           | 110 |

| 4.1  | Non-standard core language instructions                                                                      | 118 |

| 4.2  | Semantics of the <b>obsevent</b> pseudo-instruction                                                          | 119 |

| 4.3  | Concrete and abstract machine configurations                                                                 | 120 |

| 4.4  | Concrete and abstract bisimulation machines                                                                  | 121 |

| 4.5  | Concrete small-step operational semantics                                                                    | 121 |

| 4.6  | Abstract small-step operational semantics                                                                    | 122 |

| 4.7  | An IRM that prohibits more than 100 URL navigations                                                          | 129 |

#### CHAPTER 1

### INTRODUCTION

Native code is presently the most ubiquitous and prevalent form of mobile software. In 2008 alone, more than 288 million PCs were shipped, with a combined 3.6 billion units of software shipped as well [Business Software Alliance, 2010]. The majority of individuals and organizations do not have the money or manpower to produce all their own software, and therefore must blindly trust a large volume of native code obtained from untrusted or semi-trusted sources.

The software business has been growing ever since its inception. In 2008 alone, 3.6 billion packaged software units were sold worldwide, with an estimated total revenue of \$296 billion dollars [Business Software Alliance, 2010]. In 2010, the estimated revenue of enterprise software alone (i.e., software purchased by organizations not individuals) was \$244 billion dollars [Gartner, 2010]. These numbers only represent mainstream software purchases and downloads. They do not include software downloads of freeware, shareware, and open-source projects, which are harder to estimate.

Untrustworthy code sources are not limited to malicious software authors; in security-critical contexts they also include any source that is fallible. Faulty software is typically vulnerable software that can be subverted by an adversary to become malicious software. As a result, formal verification of a software's origin (e.g., by digital signature verification) provides few tangible security assurances. In fact, most software is a conglomeration of many components from many different vendors spread across many countries worldwide. A flaw in any one of these components can often be exploited to subvert the entire software and the entire system on which it runs. Mitre's Common Vulnerabilities and Exposures (CVE)

database has catalogued over 5,500 highest-severity software vulnerabilities (i.e., those that lead to complete system compromise) in major software products just since 2010

The software engineering, programming languages, and compiler design communities have a long and active history of discovering ever more powerful tools and practices for the design and implementation of secure software that is free from such faults. The Coq automated theorem proving language [INRIA, 2012] is the result of 20 years of research by the programming language community, allowing formal machine verifiable proofs to be provided with software developed entirely within the Coq framework. The software engineering community is increasingly focused on security requirements engineering, attempting to mitigate software faults via improved programming practices. However, it is unlikely that 100% of software will be developed using these technologies in the near future. The vast majority of the industry continues to develop their products in unsafe languages, such as C++, for which formal proofs of security are intractable or impossible. Such practices show little evidence of abatement.

In response to the inevitability of untrusted native code, code-consumers have historically adopted three major approaches to safely executing untrusted or untrustworthy native code applications:

- 1. Many security-conscious organizations, including many governments, develop most or all of their security-critical software in-house using secure tools and a detailed code review process.

- 2. Some untrusted software can be safely executed as-is within a sandboxing virtual machine (VM).

- 3. More recently, technologies for secure binary analysis and transformation have emerged that promise to safely filter untrustworthy code or statically transform it into safe code.

Developing in-house software may seem like the best option, but it can be a slow, time and resource consuming process. In addition, it can be just as prone to error as mainstream development, even given cutting-edge tools. Most code consumers—even governments—lack resources or personnel comparable to the worldwide software development community, which includes industry titans like Microsoft, Google, and Apple. In-house development therefore constantly lags well behind the state-of-the-art, remaining susceptible to attacks that the rest of the world has addressed long ago.

Executing software within a VM [VMware, 2012] is a viable solution, protecting a host machine from faulty software run within the VM. VMs also offer the opportunity to run guest operating systems within a host machine—a much more reasonable solution than owning a computer that uses each operating system. However, though VMs provide numerous benefits, there are many situations they cannot handle:

- 1. VMs often cannot tractably enforce fine-grained policies. For example, VMware does not support enforcement of fault isolation for individual modules within process address spaces, because doing so requires a knowledge of the internal process layout and code logic that is beyond VMware's capabilities.

- 2. Enforcing a new policy requires modifying the VM, which tends to be very difficult and error-prone.

- 3. VM-sandboxed processes cannot easily access external system resources like trusted processes on the host machine without severe performance penalties. This makes them unsuitable for many applications.

- 4. VMs are hard to prove correct; they must usually remain trusted, and they're very complex and subject to frequent change. The size of the free version of VMware Workstation installation file is currently 426MB.

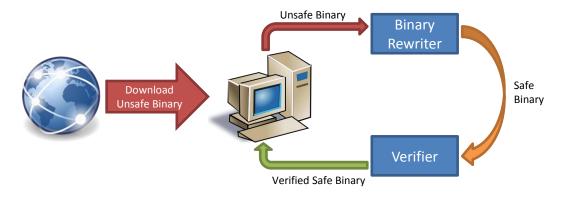

Figure 1.1. The process of rewriting an unsafe binary

5. VMs cannot be deployed as a service without expanding the circle of trust to include the service provider. For example, running software remotely on a cloud requires adding the cloud to the trusted computing base. Most clouds don't divulge details of the internal cloud architecture, so this trust is blind.

Binary transformation is an alternative solution, solving the problem of untrusted code instrumenting an untrusted binary to enforce security policies. Figure 1.1 displays the general approach of rewriting an untrusted binary from the internet.

Binary transformation comes with some strong benefits. For example, unlike a VM, a binary rewriter can enforce fine-grained security policies, since the enforcement mechanism resides within the binary instead of outside of it. In addition, different binary rewriters can enforce different policies, such as having an email client-specific rewriter that enforces different policies than a web browser-specific rewriter, allowing rewritten processes to run natively and therefore communicate directly (if permitted). This separation is not possible with a VM since it requires inter-operating processes to cohabitate under the umbrella of a single VM. Rewritten binaries are amenable to formal, machine-verification of safety, allowing the rewriter to remain untrusted, minimizing the trusted computing base. Since it's untrusted, the rewriter can be deployed as an untrusted service.

Though binary rewriting extends many benefits, it also raises daunting challenges. The first step in any binary rewriting process is accurate static analysis, including disassembly. This step is necessary to provide the instruction semantics to the rewriter, in order for it to make proper decisions about which instructions or behaviors to guard. However, x86 static disassembly is provably undecidable in the general case due to unaligned instructions, code and data interleaving, and computed control-flows. Past works overcome this challenge by restricting themselves to toy programs not representative of real-world COTS applications, requiring insider information (e.g., debug symbols) that most code producers are not willing to provide, or forcing the code producer to recompile their binary with a special compiler, which most code producers are not willing to do.

My Thesis. This dissertation argues that it is possible to perform effective, provably safe rewriting of a large category of COTS x86 binaries without metadata or perfect disassembly. Disassembly flaws can be tolerated via use of a conservative disassembler and by implementing dynamic control-flow patching that in-lines a light-weight logic to patch undiscovered computed control-flows at runtime. This approach avoids the undecidability of x86 disassembly by deferring computed control-flow decisions to runtime and including all valid execution paths in the rewritten binary. The rest of this dissertation describes the steps necessary to accomplish this through three novel approaches to disassembly and two secure rewriting strategies—one based on basic block randomization and the other using machine verifiable software fault isolation. Both of these binary rewriting techniques have very low overhead and require no source code or metadata. Lastly, it shows how compatibility issues can be handled via transparency verification.

The rest of this dissertation is structured as follows. Chapter 2 details the x86 instruction set and the difficulties involved in performing static disassembly, as well as two possible solutions. The challenges faced when performing static x86 binary rewriting are discussed

in Chapter 3, as well as two interesting binary rewriters, STIR and REINS, developed for this dissertation. Behavioral equivalence of binary rewriters is discussed in Chapter 4, and a solution to transparency for ActionScript binaries is presented. Finally, relevant related work is presented in Chapter 5 and conclusions are presented in Chapter 6.

#### CHAPTER 2

#### STATIC X86 DISASSEMBLY

Disassemblers transform machine code into human-readable assembly code. For x86 executables, this can be a daunting task in practice. Unlike Java bytecode and RISC binary formats, which separate code and data into separate sections or use fixed-length instruction encodings, x86 permits interleaving of code and static data within a section and uses variable-length, unaligned instruction encodings. This trades simplicity for brevity and speed, since more common instructions can be assigned shorter encodings by architecture designers.

Since instructions are unaligned, any address can be treated as the beginning of an instruction, and thus multiple execution paths through a binary exist. Table 2.1 shows an example of *instruction aliasing*, how x86 instructions can be interleaved within each other. Malicious code is therefore much easier to conceal in x86 binaries than in other formats. To detect and identify potential attacks or vulnerabilities in software programs, it is important to have a comprehensive disassembly for analyzing and debugging the executable code.

In software development contexts, robust disassembly is generally achieved by appealing to binary debugging information (e.g. symbol tables, relocation information, etc.) that is

Table 2.1. x86 Instruction Aliasing

| OF |              | 8A         | C3   | CO        | E8      | 03  |

|----|--------------|------------|------|-----------|---------|-----|

| jр | jp C3C0E803h |            |      |           |         |     |

|    |              | mov al, bl |      |           |         |     |

|    |              |            | retn |           |         |     |

|    |              |            |      | shr al, 3 |         |     |

|    |              |            |      |           | call 03 |     |

|    |              |            |      |           |         | add |

generated by most compilers during the compilation process. However, such information is typically withheld from consumers of proprietary software in order to discourage reverse engineering and to protect intellectual property. Thus, debugging information is not available for the vast majority of COTS binaries and other untrusted mobile code to which reverse engineering is typically applied.

Without any debugging information, accurate static disassembly of an x86 binary is an undecidable problem, since reachability of arbitrary byte addresses is equivalent to the halting problem. However, in order to correctly rewrite any binary, the first step is accurate disassembly. If any of the semantic information about the code section has been lost, that information will not be translated to the rewritten file or instruction guards and optimizations may not be properly applied, causing crashes in the rewritten binary.

The rest of Chapter 2 is arranged as follows. Section 2.1 details the various challenges involved in performing static x86 disassembly. Current approaches to x86 disassembly are presented in Section 2.2. Finally, three different approaches to x86 disassembly that this dissertation contributes are described in Sections 2.3, 2.4, and 2.5.

Acknowledgement must be made to Dr. Yan Zhou for her work on the writing and implementation of the disassemblers in Sections 2.4 and 2.5. Dr. Kevin Hamlen was also a key contributor of ideas and writing throughout this chapter.

#### 2.1 Challenges

#### **Instruction Format**

Figure 2.1 shows the x86 machine instruction binary format [Intel Corporation, 2012]. Instructions begin with 1–3 opcode bytes that identify the instruction. Instructions with operands are then followed by an addressing form specifier (ModR/M) byte that identifies register or memory operands for the instruction. Some addressing forms require a second

|   |           | 7–6 | 5–3               | 2–0     | 7–6    | 5–3     | 2–0  |              |             |

|---|-----------|-----|-------------------|---------|--------|---------|------|--------------|-------------|

|   | Opcode    | Mod | Reg*              | R/M     | Scale  | Index   | Base | Displacement | Immediate   |

| _ | 1–3 bytes | Мо  | $\overline{dR/M}$ | byte    | S      | IB byte | =    | address      | data        |

|   |           |     |                   |         |        |         |      | operand      | operand     |

|   |           | re  | egister,          | /addres | s mode | specifi | er   | (0–4 bytes)  | (0–4 bytes) |

<sup>\*</sup>The Reg field is sometimes used as an opcode extension field.

Figure 2.1. The x86 machine instruction format.

scale-index-base (SIB) byte that specifies a memory addressing mode. The addressing mode essentially encodes a short formula that dynamically computes the memory operand at runtime. For example, addressing mode [eax\*4]+disp32 references a memory address obtained by multiplying the contents of the eax register by 4 and then adding a 32-bit displacement constant. The displacement, if present, comes after the SIB byte. Finally, immediate operands (constants) are encoded last and have a width of up to 4 bytes (on 32-bit architectures).

In addition to this complicated instruction format, there are a number of prefix bytes that may precede the opcode bytes, all eleven of which may be used in combination and each with their own specific function. For example, 0x66 and 0x67 modify the byte width of the operand and address size respectively, where as 0xF2 and 0xF3 are both used to repeat the instruction they precede a specific number of times as specified in the ecx register.

A few x86 machine instructions have multiple different correct representations at the assembly level. Most notable is the floating point WAIT instruction, which can either be interpreted as an opcode prefix for the instruction it precedes, or as a separate instruction in its own right. We adopt the former interpretation in our treatment, since it makes for a more compact assembly representation.

To contrast, Figure 2.2 shows the instruction format of Java bytecode. The drastic difference in complexity is apparent. Each Java bytecode instruction starts with a 1 byte opcode which is optionally followed by operand bytes depending on the opcode. There

$$\begin{array}{c|c} \textbf{Opcode} & \textbf{Operand} \\ \textbf{1 byte} & \textbf{(0+ bytes)} \end{array}$$

Figure 2.2. The Java bytecode instruction format.

are only 256 possible opcodes (0x00-0xFF), and 54 are currently unused. In addition, java bytecode branch targets are static, so instruction aliasing is not possible.

# **Control-Flow Modifying Instructions**

Instructions that modify the control-flow of a program (that modify the eip register) can either be *direct* or *indirect*.

#### Definition 2.1.1. Direct Branches

Direct branch instructions add their operand to the eip register, treating it as an offset.

#### Definition 2.1.2. Indirect Branches

Indirect branch instructions calculate their targets at runtime, either by setting the eip register to their operand, as in the case of jmp and call instructions, or popping their target off the stack in the case of retn instructions.

Direct branch instructions are not difficult to analyze as their target is static and does not change at runtime. Indirect branches, however, calculate their targets at runtime. Register values, stack values, and any dereferenced memory address can be targeted. Table 2.2 shows examples of each indirect branch type. Due to these branch types and the lack of restrictions on branch targets, all addresses within an executable code section are viable targets, even if they are in the interior of another instruction.

Once again, we contrast this property against Java bytecode, which disallows branch instructions to the middle of another instruction. In addition, branches are all direct in Java bytecode, and thus can all be determined statically.

Table 2.2. Indirect Branch Types

| Branch Type                | Example                 |

|----------------------------|-------------------------|

| Register                   | call eax                |

| Dereferenced Register      | call [eax]              |

| Dereferenced Stack         | call [esp - 4]          |

| Dereferenced Memory        | call [0x4040d4]         |

| Scaled Dereferenced Memory | call [eax*4 + 0x4040d4] |

# Code/Data Interleaving

The final property that makes x86 binaries so difficult to disassemble is that code and data can be interleaved within executable sections. Consider Java bytecode, which disallows such interleaving: disassembly starts with the first instruction and follows to each successive instruction until the end is reached. The same would be true in x86 if there was no data within executable sections. Every byte in the executable section can be treated as data or as code, and theoretically as both.

Table 2.3 shows the differences between disassembling java and x86 binaries. Multiple execution sequences exist for the same sequence of bytes in x86, where as in Java bytecode, only one instruction sequence is possible.

## Static x86 Disassembly Undecideability

The combination of these factors implies the following lemma about static x86 disassemblies:

**Lemma 2.1.3.** It is Turing-undecidable whether an arbitrary assembly code is an accurate disassembly of an arbitrary, executable x86 binary, where an accurate disassembly is one that correctly classifies each byte as (a) an instruction boundary, (b) internal to an instruction, or (c) non-executable data.

|               | 5E 5F 5D C3 E8 BB 10 | C 03 00 89 04 24 68 | BB 1C 03         |

|---------------|----------------------|---------------------|------------------|

| Java          | x86                  | x86                 | x86              |

| Disassembly   | Disassembly 1        | Disassembly 2       | Disassembly 3    |

| dup2_x2       | pop esi              | pop esi             | pop esi          |

| new           | pop edi              | pop edi             | pop edi          |

| nop           | pop ebp              | pop ebp             | pop ebp          |

| 12f           | retn                 | retn                | retn             |

| $iconst_{-}1$ | call sub_433784      | db EB               | db EB            |

| fload_2       | mov [esp+24], eax    | mov ebx, 8900031Ch  | db BB            |

| imul          | push BB1C03A1        | add al, 24h         | sbb al, 3        |

| new           |                      | push BB1C03A1       | add [ecx-44], cl |

|               |                      |                     | sbb al. 3        |

Byte Sequence

Figure 2.3. Java Disassembly vs. x86 Disassembly

# 2.2 Current x86 Disassembly

There are a variety of different approaches to statically disassembling an x86 binary accurately. Table 2.3 gives examples of the most common approaches, as well as some of their benefits and deficiencies.

Modern static disassemblers for x86 binaries employ a variety of techniques to accurately differentiate bytes that comprise instructions from those that comprise static data. IDA Pro [Hex-Rays, 2012] is widely acknowledged as the best tool currently available for distinguishing code from data in arbitrary binaries (cf., [Balakrishnan et al., 2005, Kinder and Veith, 2008]). It combines straight-line, heuristic, and execution emulation-based disassembly while also providing an extensive GUI interface and multiple powerful APIs for interacting with the disassembly data. Recent work has applied model-checking and abstract interpretation to improve upon IDA Pro's analysis [Kinder and Veith, 2008, Kinder et al., 2009], but application of these technologies is currently limited to relatively small binaries, such as device drivers, for which these aggressive analyses remain tractable.

Table 2.3. Disassembly Techniques

| Disassembly  | Description                                               |

|--------------|-----------------------------------------------------------|

| technique    |                                                           |

| Fall-through | Disassemble from the first byte of the binary and fall    |

|              | through to each following instruction, regardless of se-  |

|              | mantics. No attempt to distinguish code from data is      |

|              | made.                                                     |

| Control-flow | Follow the semantics of the assembly language, using      |

|              | branches to determine where to disassemble next. How-     |

|              | ever, computed jump targets are difficult to determine    |

|              | because they are calculated at run-time.                  |

| Heuristics   | Probability based heuristics can be used in order to dis- |

|              | assemble x86, based on the semantics of x86. Since these  |

|              | are based on probabilities, many false positives arise in |

|              | distinguishing code from data.                            |

| Dynamic      | Disassembling dynamically is a viable solution for many   |

|              | problems, but a code-coverage issue arises due to the     |

|              | fact that most executions do not actually execute all     |

|              | instructions in the code section of a binary.             |

All other widely available disassemblers to our knowledge take a comparatively simplistic approach that relies mainly upon straight-line disassembly, and that therefore requires the user to manually separate code from data during binary analysis. Our tests therefore focus on comparing the accuracy of our algorithm to that of IDA Pro.

Disassembly heuristics employed by IDA Pro include the following:

- Code entry point. The starting point for analyzing an executable is the address listed in the header as the code entry point. That address must hold an instruction, and will hopefully lead to successfully analyzing a large portion of the executable.

- Function prologues and epilogues. Many function bodies compiled by mainstream compilers begin with a recognizable sequence of instructions that implement one of the standard x86 calling conventions. These byte sequences are assumed by IDA Pro to be the beginnings and ends of reachable code blocks.

- Direct jumps and calls. The destination address operand of any static jump instruction that has already been classified as reachable code is also classified as reachable code.

- Unconditional jumps and returns. Bytes immediately following a reachable, unconditional jump or return instruction are considered as potential data bytes. These often contain static data such as jump tables, padding bytes, or strings.

However, despite a decade of development and tuning, IDA Pro nevertheless fails to reliably distinguish code from data even in many non-malicious, non-obfuscated x86 binaries. Some common mistakes include the following:

• Misclassifying data as returns. IDA Pro frequently misclassifies isolated data bytes within data blocks as return instructions. Return instructions have a one-byte x86 encoding and are potential targets of computed jumps whose destinations are not statically decidable. This makes them extremely difficult to distinguish from data. IDA

Pro therefore often misidentifies data bytes that happen to match the encoding of a return instruction.

- 16-bit legacy instructions. The x86 instruction set supports legacy 16-bit addressing modes, mainly for reasons of backward compatibility. The vast majority of genuinely reachable instructions in modern binaries are 32- or 64-bit. However, many data bytes or misaligned code bytes can be misinterpreted as 16-bit instructions, leading to flawed disassemblies.

- Mislabeled padding bytes. Many compilers generate padding bytes between consecutive blocks of code for alignment purposes. These bytes are not reached by typical runs, nor accessed as data, so their proper classification is ambiguous. IDA Pro typically classifies them as data, but this can complicate some code analyses by introducing many spurious code-data boundaries in the disassembly. In addition, these bytes can later become reachable if the binary undergoes hotpatching [Microsoft Corporation, 2005]. We therefore argue that these bytes are more properly classified as code.

- Flows from code to data. IDA Pro disassemblies frequently contain data bytes immediately preceded by non-branching or conditionally branching instructions. This is almost always an error; either the code is not actually reachable (and is therefore data misidentified as code) or the data is reachable (and is therefore code misidentified as data). The only exception to this that we have observed in practice is when a call instruction targets a non-returning procedure, such as an exception handler or the system's process-abort function. Such call instructions can be immediately followed by data.

To provide a rough estimate of the classification accuracy of IDA Pro, we wrote scripts in IDAPython [Erdélyi, 2008] that detect obvious errors made by IDA Pro in its disassemblies.

Table 2.4. Statistics of IDA Pro 5.5 disassembly errors

| File Name            | Instructions | Mistakes |

|----------------------|--------------|----------|

| Mfc42.dll            | 355906       | 1216     |

| Mplayerc.exe         | 830407       | 474      |

| RevelationClient.exe | 66447        | 36       |

| Vmware.exe           | 364421       | 183      |

Table 2.4 gives a list of the executables we tested and counts of the errors we identified for IDA Pro 5.5. The main heuristic we used to identify errors is the existence of a control-flow from code to data. Certain other errors were identified via manual inspection. It is interesting to note that most programs compiled using the GNU family of compilers have little to no errors in their IDA Pro disassemblies. This is probably because GNU compilers tend to yield binaries in which code and data are less interleaved, and they perform fewer aggressive binary-level optimizations that can result in code that is difficult to disassemble.

# 2.3 Shingled Disassembly

Since computed branch instructions in x86 have their targets established at runtime, every byte within the code section can be a target and thus must be considered as executable code. Therefore, we refer to a disassembler that retains all possible execution paths through a binary as a *Shingled Disassembler*.

### Definition 2.3.1. Shingle

A shingle is a consecutive sequence of bytes that decodes to a single machine instruction.

Shingles may overlap.

The core functionality of the shingled disassembler is to eliminate bytes that are clearly data and compose a byte sequence that retains information for generating every possible valid shingle of the source binary. This is a major benefit of this approach since the shingled disassembly encodes a superset of all the possible valid disassemblies of the binary. In later

sections, we discuss how we apply our graph disassembler to prune this superset until we find the most probable execution paths. In order to define what consists of a valid execution path, we must first discuss a few key concepts.

# Definition 2.3.2. Fall-through

Shingle x (conditionally) falls through to shingle y, denoted  $x \to y$ , if shingle y is located adjacent to and after instruction x, and the semantics of instruction x do not (always) modify the program counter<sup>1</sup>. In this case, execution of instruction x is (sometimes) followed by execution of instruction y at runtime.

#### Definition 2.3.3. Unconditional Branch

A shingle is an unconditional branch if it only falls through when its operand explicitly targets the immediately following byte. Unconditional branch instructions for x86 include jmp and ret instructions.

Unconditional branch instructions are important in defining valid disassemblies because the last instruction in any disassembly must be an unconditional branch. If this is not the case, the program could execute past the end of its virtual address space.

#### Definition 2.3.4. Static Successor

A control-flow edge (x, y) is static if  $x \to y$  holds or if x is a conditional or unconditional branch with fixed (i.e., non-computed) destination y. An instruction's static successors are defined by  $S(x) = \{y \mid (x, y) \text{ is static}\}.$

#### Definition 2.3.5. Post-dominating Set

The (static) post-dominating set P(x) of shingle x is the transitive closure of S on  $\{x\}$ . If

<sup>&</sup>lt;sup>1</sup>At first glance, it would seem that we could strengthen our definition of fall-throughs to any two instructions that do not have an unconditional branch instruction between them. However, there are cases where a compiler will place a call and jcc instruction followed by data bytes. A common example of this is call [IAT:ExceptionHandler] since the exception handler function will never return.

there exists a static control-flow from x to an illegal address (e.g., an address outside the address space or whose bytes do not encode a legal instruction), then P(x) is not well defined and we write  $P(x) = \bot$ .

## Definition 2.3.6. Valid Execution Path

All paths in P(x) are valid execution paths from x.

The x86 instruction set does not make use of every possible opcode sequence, therefore certain bytes cannot be the beginning of a code instruction. For example, the 0xFF byte is used to distinguish the beginning of one 7 different instructions, using the byte that follows to distinguish which instruction is intended. However, 0xFFFF is an invalid opcode that is unused in the instruction set. This sequence of bytes is common because any negative offset in two's complement that branches less than 0xFFFF bytes away will start with 0xFFFF. The shingled disassembler can immediately mark any shingle whose opcode is not supported under the x86 instruction set as data. A shingle that is marked as data is either used as the operand of another instruction, or it is part of a data block within the code section. Execution of the instruction would cause the program to crash.

#### Lemma 2.3.7. Invalid Fall-through

$\forall x,y:: x \rightarrow y \land y = \emptyset \rightarrow x = \emptyset$ , in which  $\emptyset$  stands for data bytes.

Any time that we encounter an address that is marked data, all fall-throughs to that instruction can be marked as data as well. Direct branches also fall into this definition. All direct call and jmp instructions imply a direct executional relationship between the instruction and its target. Therefore, if any shingle that targets a shingle previously marked as data can also be marked as data.

#### Definition 2.3.8. Sheering

A shingle x is sheered from the shingled disassembly when  $\forall y :: x \rightarrow y$ , x and all y are marked as data in the shingled disassembly.

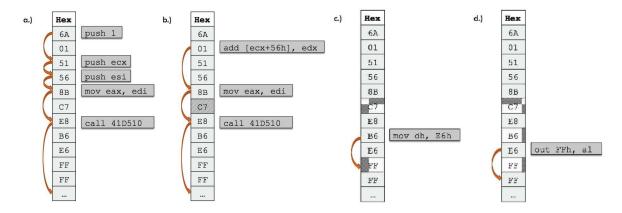

Figure 2.4 illustrates how our shingled disassembler works. Given a binary of byte sequence 6A01 5156 8BC7 E8B6 E6FF FF..., the shingled disassembler performs a single-pass, ordered scan over the byte sequence. Data bytes and invalid shingles are marked along the way. Figure 2.4a demonstrates the first series of valid shingles, beginning at the first byte of the binary. Figure 2.4b starts at the second byte, which falls through to a previously disassembled shingle. The shingle with byte C7 is then marked as data (shaded in Figure 2.4) since it is an invalid opcode. Figure 2.4c shows an invalid shingle since it falls through to an invalid opcode FFFF. Our shingled disassembler marks the two shingles B6 and FF as invalid in the sequence. Figure 2.4d shows another valid shingle that begins at the ninth byte of the binary. After completing the scan, our shingled disassembler has stored information necessary to produce all valid paths in P(x).

Figure 2.4. Shingled disassemblies of a given binary 6A0151568BC7E8B6E6FFFF (a) a sequence of shingles beginning at the first byte; (b) a sequence of shingles beginning at the second byte; (c) an invalid shingle that falls through to an invalid opcode FF; (d) a valid shingle beginning at the E6 byte.

The pseudocode for generating a shingled disassembly for a binary is shown in Algorithm 1.

This disassembly technique results in a completely valid disassembly that executes properly.

All instruction sequences included in the shingled disassembly are valid based on the semantics of the x86 instruction set. However, not all of the disassembled shingles are necessary: many of the instructions in the disassembly are never executed and were not intended execution

## **Algorithm 1**: Shingled Disassembly

```

Input: x_0 \dots x_i \dots x_{n-1};

// byte input

Ins(x_i)—output \emptyset if x_i is a data byte

Output: y_0 \dots y_i \dots y_{n-1}

t = 0;

y_i = \varnothing, \forall i = 1, \ldots, n-1;

// initialize y_i

while t < n \, \operatorname{do}

v=t;

while y_v = \emptyset do

y_v = Ins(x_v) \parallel \emptyset;

if y_v \neq \emptyset then v = v + |Ins(x_v)|;

\mathbf{end}

else

| break ;

end

end

t++;

end

t=n;

while t \ge 0 do

if x_t = \emptyset then

// invalidate any opcode branching to address t

\forall v \text{ if } v+\mid x_v\mid:=t \text{ then }

x_v := \emptyset;

end

end

t--;

end

```

sequences when the binary was compiled. In order to prune unnecessary shingles, another disassembly technique can be applied to narrow down to a single execution sequence of shingles.

# 2.4 Machine Learning Disassembly Model

None of the approaches listed in Section 2.2 attempt to use Machine Learning as a tool in the disassembly process. Each of the described techniques is based around a knowledge

of the semantic information in an executable's code section (or ignorance of it in the case of straight-line disassembly). However, the problem of disassembly can be simplified down beyond instruction semantics.

We define the tagging problem as follows: Given a non-empty input string X over an alphabet  $\Sigma$ , find a set of transition events  $\mathcal{T} = \{\$_1, \dots, \$_M\}$  such that  $\mathcal{T} = \arg \max_{\mathcal{T}} f(X, \mathcal{T})$ , where  $\$_i$  at position i < |X| marks a transition event e in X, and f is a function that measures the likelihood that X is tagged correctly.

The tagging problem resembles the word segmentation problem in some natural languages where no clear separations exist between different words [Teahan et al., 2000]. In the word segmentation problem, the task is to find correct separations between sequences of characters to form words. In the tagging problem, our objective is to find separations between different instructions, and often between instructions and data as well. In both problems, resolving ambiguities is the major challenge. For example, a byte sequence E8 F9 33 6A 00 can be a 5-byte call instruction (opcode E8), or three bytes of data followed by a push instruction (opcode 6A). Ambiguities can only be resolved through investigating their surrounding context.

Solutions to the tagging problem must also successfully identify and ignore "noise" in the form of padding bytes. Padding bytes are neither executed as code nor accessed as data on any run of the executable, so their classification is ambiguous. However, reliably distinguishing these padding sequences from true code and data is non-trivial because the same sequence of bytes often appears as both code and padding within the same executable. For example, the instruction

is semantically a *no-operation* (NOP), and is therefore used as padding within some instruction streams to align subsequent bytes to a cache line boundary, but is used in other instruction streams as a genuinely reachable instruction. Another common use of semantic NOPs is to introduce obfuscation to hide what the program is doing.

In general, code and data bytes may differ only in their locations in the sequence, not in their values. Any byte sequence that is code could appear as data in an executable, even though it should statistically appear much more often as code than data. Not every data sequence can be code, however, since not all byte sequences are legitimate instruction encodings, as was discussed in Section 2.3.

## 2.4.1 Design

There are three components in our tagging algorithm: an instruction reference array, a utility function, and heuristic sanity checks. The reference array stores the length of an instruction given the bytes of an opcode (and the existence of length-relevant prefix bytes). The utility function estimates the probability that a byte sequence is code. We estimate the probability using a context-based language model built from pre-tagged x86 executables. Finally, our sanity checks use heuristics to verify that our disassembly does not violate x86 instruction semantics.

### Instruction Reference Array

From the x86 instruction decoding specification we derive a mapping from the bytes of an opcode to the length of the instruction. This is helpful in two respects: First, it marks a definite ending of an instruction that allows us to move directly to the next instruction or data. Second, it tells us when a series of bytes is undefined in the x86 instruction set, which means that the current byte cannot be the beginning of an instruction. We tested our code against more than ten million instructions in the IDA Pro disassembler and had 100% accurate instruction lengths.

### **Utility Function**

The utility function helps predict whether a byte sequence is code or data in the current context. If the current byte sequence is unlikely to be code, our tagging algorithm moves to the next byte sequence. If we predict that the byte sequence is code, we look up the length of the instruction in the instruction reference array and move to the next byte sequence. The following two properties express the desired relationship between the utility function and its input byte sequence.

**Property 2.4.1.** A byte sequence bordered by transitions is tagged as code (resp., data) if its utility as code (resp., data) is greater than its utility as data (resp., code).

**Property 2.4.2.** A transition between two byte sequences  $S_A$  and  $S_B$  entails a semantic ordering in machine code:  $f(S_B|S_A) \ge f(S_B|S_*)$ , where  $S_*$  is any subsequence but  $S_A$  in a given binary, and f is the utility function.

Our utility function estimates the likelihood of a transition event using context-based analysis. We collect context statistics from a set of pre-tagged binaries in the training set. In a pre-tagged binary, code-code and code-data/data-code transitions are given. Two important forms of information are yielded by pre-tagged binaries. First, they provide semantic groupings of byte sequences that are either code or data; and second, they provide a semantic ordering between two subsequences, which predicts how likely a subsequence is followed by another. To correctly tag an input hex string, both pieces of information are important. This calls for a language model that We choose to use a context-based statistical data compression model for storing context statistics of each byte sequence encountered in the training set of binary executables. base of the utility function. The data model have the following traits:

- can capture local coherence in a byte sequence, and

- can capture long-range correlations between two adjacent subsequences—i.e., subsequences separated by a code-code or code-data/data-code transition.

Several modern statistical data compression models [Moffat and Turpin, 2002] are known for their context-based analysis. These data models can work directly on any raw input regardless of source and type. We use the current state of the art data compression model as our language model. Before we discuss the details of the language model, we give the tagging algorithm in Algorithm 2.

```

Algorithm 2: Tagging

// input string of bytes

Input: x_0 \dots x_i \dots x_{n-1};

// language model

Output: x_0 \dots x_i | x_{i+1} \dots x_j | \dots | x_k \dots x_{n-1};

// segmented string

t \leftarrow 0;

while t < n \, \operatorname{do}

\ell \leftarrow 0;

if x_t \in M_c then

// lookup instruction length

// tag as possible data

// output the segment

print x_t \dots x_{t+\ell-1};

t \leftarrow t + \ell;

```

Context-based Data Compression Model. The compression model we use to store context statistics is predication by partial matching (PPM) [Cleary and Witten, 1984, Cormack and Horspool, 1987, Cleary and Teahan, 1997]. The theoretical foundation of the PPM algorithm is the kth order Markov model, where k constrains the maximum order context based on which a symbol probability is predicted. PPM models both short-range and long-range correlations among subsequences by using dynamic context match. The context of the ith symbol  $x_i$  in an input string is the previous i-1 symbols. Its kth order context  $c_i^k$  includes only the k prior symbols. To predict the probability of seeing  $x_i$  in the current location of the input, the PPM algorithm first searches for a match of  $c_i^k$  in the context tree. If a match is found,  $p(x_i|c_i^k)$  is returned as the symbol probability. If such a match does not exist in the context tree, an escape event is recorded and the model falls back to a lower-order

context  $c_i^{k-1}$ . If a match is found, the following symbol probability is returned:

$$p(x_i|c_i^k) = p(Esc|c_i^k) \cdot p(x_i|c_i^{k-1})$$

where  $p(Esc|c_i^k)$  is the escape probability conditioned on context  $c_i^k$ . The escape probability models the probability that  $x_i$  will be found in the lower-order context. This process is repeated whenever a match is not found until an order-0 context has been reached. If  $x_i$  appears in the input string for the first time, a uniform probability of distinct symbols that have been observed so far will be returned. Therefore, the probability of  $x_i$  in a string of input is modeled as follows:

$$p(x_i|c_i^k) = \begin{cases} \left(\prod_{j=k'+1}^k p(Esc|c_i^j)\right) \cdot p(x_i|c_i^{k'}) & \text{if } k \ge 0\\ \frac{1}{|A|} & \text{if } k = -1 \end{cases}$$

where  $k' \leq k$  is the context order when the first match is found for  $x_i$ , and |A| is the number of distinct symbols seen so far in the input. If the symbol is not predicted by the order-0 model, a probability defined for the order -1 context is predicted.

The PPM model predicts symbol probabilities. To estimate the probability of a sequence of symbols, we compute the product of the symbol probabilities in the sequence. Thus, given a data sequence  $X = x_1x_2 \dots x_d$  of length d, where  $x_i$  is a symbol in the alphabet, the probability of seeing the entire sequence given a compression model M can be estimated as

$$p(X|M) = \prod_{i=1}^{d} p(x_i|x_{i-k}^{i-1})$$

where  $x_i^j = x_i x_{i+1} x_{i+2} \dots x_j$  for i < j.

We use the above probability estimate as our utility function. We build two compression models  $M_c$  and  $M_d$  from the pre-tagged binaries in the training set:  $M_c$  is built from tagged instructions and  $M_d$  is built from tagged data. Given a new binary executable e and a subsequence  $e_i$  in e,

$$M_c = \{e_i | p(e_i|M_c) > p(e_i|M_d)\}$$

Classification. After tagging the transitions in the executable, we have segments of bytes. Even though the tagging algorithm outputs each segment either as code or data, we cannot assume this preliminary classification is correct because some data bytes may match legitimate opcodes for which a valid instruction length exists in the reference array. The tagging algorithm will output this segment as code even though it is data. Therefore, we need to reclassify each segment as data or code.

Our classification algorithm makes use of the aforementioned language model and several well known semantic heuristics. The language models are also used in the tagging algorithm. The heuristics are adapted from those used by human experts for debugging disassembly errors. We first discuss the language model-based classification module followed by the semantic heuristics.

Classification Using Language Model. Classifying byte sequences is a binary classification problem. We reuse the two compression models built for tagging. Recall that model  $M_c$  is built from pre-tagged code and model  $M_d$  is built from the pre-tagged data in the training set. To classify a byte sequence B, we compute a log likelihood of B using each data model  $\alpha \in \{c, d\}$ :

$$p(B|M_{\alpha}) = -\log \prod_{i=1}^{|B|} p(b_i|b_{i-k}^{i-1}, M_{\alpha})$$

where  $M_{\alpha}$  is the compression model associated with class  $\alpha$ , |B| is the length of byte sequence B, sequence  $b_{i-k}, \ldots, b_i$  is a subsequence in B, and k is the length of the context. The class membership  $\alpha$  of B is predicted by minimizing the cross entropy [Teahan, 2000, Bratko et al., 2006]:

$$\alpha = \underset{\alpha \in \{c,d\}}{\operatorname{arg\,min}} - \frac{1}{|B|} p(B|M_{\alpha})$$

## Sanity Checks

Once we have deemed which instructions are code and data, sanity checks are necessary to ensure that the disassembly we have generated makes sense based on x86 instruction semantics.

Certain semantic heuristics are helpful in determining an accurate class membership of an x86 byte sequence. Reverse engineers rely heavily upon such heuristics when manually correcting flawed disassemblies. In most cases, these heuristics make no changes but are useful in ensuring the disassembly is creating a valid execution sequence.

Word data tables. Many static data blocks in code sections store tables of 4-byte integers. Often the majority of 4-byte integers in these tables have similar values, such as when the table is a method dispatch or jump table consisting of code addresses that mostly lie within a limited virtual address range. One way to quickly identify such tables is to examine the distribution of byte values at addresses that are 1 less than a multiple of 4. When these high-order bytes have low variance, the section is likely to be a data table rather than code, and is classified accordingly.

16-bit addressing modes. When classifying a byte sequence as code yields a disassembly densely populated by instructions with 16-bit operands (and the binary is a 32-bit executable), this indicates that the sequence may actually be data misclassified as code. Modern x86 architectures support the full 16-bit instruction set of earlier processor generations for backward compatibility reasons, but these legacy instructions appear only occasionally in most modern 32-bit applications. The 16-bit instructions often have short binary encodings, causing them to appear with higher frequency in randomly generated byte sequences than they do in actual code.

Data after unconditional jumps. Control-flows from code to data are almost always disassembly errors; either the data is reachable and is therefore code, or the code is actually unreachable and is therefore data. Thus, data inside of a code section can only occur at the very beginning of the section or after a branch instruction—usually an unconditional jump or return instruction. It can occasionally also appear after a call instruction if the call

File Name File Size (K) Code (K) Data (K) Transitions 7zFM.exe 379 271 3.3 1379 68 23 8.6 182 notepad.exe DosBox.exe 3640 294767.215355 WinRAR.exe 1059 718 31.6 5171 148.2 Mulberry.exe 9276 4632 36435 11823 9798 49.247757 scummvm.exe emule.exe 5624 3145 119.5 24297 Mfc42.dll 1110 751 265.515706 Mplayerc.exe 5858 4044 126.1 28760 1493 RevelationClient.exe 38225218.4 2675 1158 87.3 18259 Vmware.exe

Table 2.5. Programs tested with PPM Disassembler

never returns (e.g., the call targets an exception handler or process-abort function). This observation gives rise to the following heuristics:

- If an instruction is a non-jump, non-return surrounded by data, it is reclassified as data.

- If a byte sequence classified as data encodes an instruction known to be a semantic NOP, it is reclassified as code.

#### 2.4.2 Evaluation

We tested our disassembly algorithm on the 11 real-world programs listed in Table 2.5. In each experiment, we used 10 of the programs to build the language models and the remaining one for testing. All the executables are pre-tagged using IDA Pro; however, IDA Pro yields imperfect disassemblies for all 11 executables. Some instructions it consistently labels as data, while others—particularly those that are semantic nops—it labels as data or code depending on the context. This leads to a noisy training set.

Since we lack perfect disassemblies of any of these programs, evaluation of the classification accuracy of each algorithm is necessarily based on a manual comparison of the disassembly results. When the number of classification disagreements is large, this can quickly exceed the

human processing limit. However, disagreements in which one algorithm identifies a large, contiguous code section missed by the other are relatively easy to verify by manual inspection. These constituted the majority of the disagreements, keeping the evaluation tractable.

Tagging Results. We first report the accuracy of our tagging algorithm. Inaccuracies can take the form of code misclassified as data (false negatives) and data misclassified as code (false positives). Both can have potentially severe consequences in the context of reverse engineering for malware defense. False negatives withhold potentially malicious code sequences from expert analysis, allowing attacks to succeed; false positives increase the volume of code that experts must examine, exacerbating the difficulty of separating potentially dangerous code from benign code. We therefore compute the tagging accuracy as

$$accuracy = 1 - \frac{false\ negatives + false\ positives}{total\ number\ of\ instructions}$$

where false positives count the number of instructions erroneously disassembled from data bytes.

As can be seen in Table 2.6 we were able to tag 6 of the 11 binaries with 100% accuracy. For the remaining 5, the tagging errors were mainly caused by misclassification of small word data tables (see §2.4.1) consisting of 12 or fewer bytes. Our heuristic for detecting such tables avoids matching such small tables in order to avoid misclassifying short semantic NOP sequences that frequently pad instruction sequences. Such padding often consists of 3 identical 4-byte instructions, which collectively resemble a very short word data table.

Classification Results. To evaluate the classification accuracy we took the output of our tagging algorithm and ran each segment through the language model to get its class membership. Table 2.7 shows the classification results of our disassembly algorithm. False positives (FP), false negatives (FN), and overall classification accuracy is listed for each disassembler.

Table 2.6. Tagging accuracy

| File Name            | Errors | Total   | Tagging Accuracy |

|----------------------|--------|---------|------------------|

| 7zFM.exe             | 0      | 88164   | 100%             |

| notepad.exe          | 0      | 6984    | 100%             |

| DosBox.exe           | 0      | 768768  | 100%             |

| WinRAR.exe           | 39     | 215832  | 99.982%          |

| Mulberry.exe         | 0      | 1437950 | 100%             |

| scummvm.exe          | 0      | 2669967 | 100%             |

| emule.exe            | 117    | 993159  | 99.988%          |

| Mfc42.dll            | 0      | 355906  | 100%             |

| Mplayerc.exe         | 307    | 830407  | 99.963%          |

| RevelationClient.exe | 71     | 66447   | 99.893%          |

| Vmware.exe           | 16     | 364421  | 99.998%          |

Table 2.7. A comparison of mistakes made by IDA Pro and by our disassembler

|                      | IDA Pro 5.5              |                        | Ours     |                          | urs                    |          |

|----------------------|--------------------------|------------------------|----------|--------------------------|------------------------|----------|

| File Name            | $\overline{\mathbf{FP}}$ | $\mathbf{F}\mathbf{N}$ | Accuracy | $\overline{\mathbf{FP}}$ | $\mathbf{F}\mathbf{N}$ | Accuracy |

| 7zFM.exe             | 0                        | 1                      | 99.999%  | 0                        | 0                      | 100%     |

| notepad.exe          | 4                        | 0                      | 99.943%  | 0                        | 0                      | 100%     |

| DosBox.exe           | 0                        | 26                     | 99.997%  | 0                        | 0                      | 100%     |

| WinRAR.exe           | 0                        | 23                     | 99.989%  | 0                        | 39                     | 99.982%  |

| Mulberry.exe         | 0                        | 202                    | 99.986%  | 0                        | 0                      | 100%     |

| scummvm.exe          | 0                        | 65                     | 99.998%  | 0                        | 0                      | 100%     |

| emule.exe            | 0                        | 681                    | 99.931%  | 0                        | 117                    | 99.988%  |

| Mfc42.dll            | 0                        | 1216                   | 99.658%  | 0                        | 47                     | 99.987%  |

| Mplayerc.exe         | 0                        | 2517                   | 99.697%  | 0                        | 307                    | 99.963%  |

| RevelationClient.exe | 0                        | 2301                   | 96.537%  | 0                        | 71                     | 99.893%  |

| Vmware.exe           | 0                        | 183                    | 99.950%  | 0                        | 45                     | 99.988%  |

eMule Case Study. To show some of the specific differences between decisions made by IDA Pro's disassembler and our approach, we here present a detailed case study of eMule, a popular peer-to-peer file sharing program. Case studies for other executables in our test suite are similar to that presented here. Table 2.8 illustrates examples in which IDA Pro classified bytes were code but our disassembler determined that they were data, or vice versa. In the table, db is an assembly directive commonly used to mark data bytes in a code listing. To identify all discrepancies, we stored all instructions from both disassemblies to text files with code/data distinguishers before every instruction. We then used sdiff to find the differences. The cases in Table 2.8 summarize all of the different kinds of discrepancies we discovered.

IDA Pro makes heavy use of heuristic control-flow analysis to infer instruction start points in a sea of unclassified bytes. Thus, its classification of bytes immediately following a call instruction depends on its estimate of whether the called method could return. For example, Case 1 of Table 2.8 shows a non-returning call to an exception handler. The call is immediately followed by padding bytes that serve to align the body of the next function. These bytes are also legitimate (but unreachable) instructions, so could be classified as data or code (though we argue in §2.2 that a code classification is preferable). However, this control-flow analysis strategy leads to a classification error in Case 2 of the table, wherein IDA Pro incorrectly identifies method GetDLGItem as non-returning and therefore fails to disassemble the bytes that follow the call. Our disassembler correctly identifies both byte sequences as code. Such scenarios account for about 20 of IDA Pro's disassembly errors for eMule.

Case 3 of Table 2.8 illustrates a repetitive instruction sequence that is difficult to distinguish from a table of static data. IDA Pro therefore misidentifies some of the bytes in this sequence as data, whereas our algorithm correctly identifies all as code based on the surrounding context.

Many instruction sequences in x86 binaries are only reachable at runtime via dynamically computed jumps. These sequences are difficult to identify by control-flow analysis alone

Table 2.8. Disassembly discrepancies between IDA Pro and our disassembler for eMule

|      |                                             | Example Disassemblies                                                                                     |                                                                                                                    |  |  |

|------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

| Case | Description                                 | IDA Pro 5.5                                                                                               | Ours                                                                                                               |  |  |

| 1    | padding after a<br>non-returning call       | call ExceptionHandler $db \ (1-9 \ bytes)$ function_start                                                 | call ExceptionHandler code (1-9 bytes) function_start                                                              |  |  |

| 2    | calls misidentified as non-returning        | call GetDLGItem $db\ 88h\ 50h$ sbb al, 8Bh                                                                | call GetDLGItem mov edx, [eax+1Ch]                                                                                 |  |  |

| 3    | repetitive<br>instruction<br>sequences      | db (4 bytes)  push 0 push 0 call 429dd0h                                                                  | push 0 push 0 push 0 push 0 push 0 call 429dd0h                                                                    |  |  |

| 4    | missed computed jump targets                | db (12 bytes) push offset 41CC30h                                                                         | mov eax, large fs:0<br>mov edx, [esp+8]<br>push FFFFFFFFh<br>push offset 41CC30h                                   |  |  |