# MASTER/SLAVE SPECULATIVE PARALLELIZATION AND APPROXIMATE CODE

by

Craig B. Zilles

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

(Computer Sciences)

at the

UNIVERSITY OF WISCONSIN - MADISON

2002

#### **Abstract**

This dissertation describes *Master/Slave Speculative Parallelization* (MSSP), a novel execution paradigm to improve the execution rate of sequential programs by parallelizing them speculatively for execution on a multiprocessor. In MSSP, one processor—the *master*—executes an *approximate* copy of the program to compute values the program's execution is expected to compute. The master's results are then checked by the *slave* processors by comparing them to the results computed by the original program. This validation is parallelized by cutting the program's execution into tasks. Each slave uses its predicted inputs (as computed by the master) to validate the input predictions of the next task, inductively validating the whole execution.

Approximate code, because it has no correctness requirements—in essence it is a software value predictor—can be optimized more effectively than traditionally generated code. It is free to sacrifice correctness in the uncommon case in order to maximize performance in the common case. In addition to introducing the notion of approximate code, this dissertation describes a prototype implementation of a program distiller that uses profile information to automatically generate approximate code. The distiller first applies unsafe transformations to remove uncommon case behaviors that are preventing optimization; second, it applies traditional safe optimizations to exploit the newly created opportunities.

The mechanisms necessary for a MSSP execution and an example implementation based on a chip multiprocessor are also described. These mechanisms buffer the master's predictions and make them available to the slaves, capture the input and output values for each slave task, and verify and commit the slave tasks to give the appearance of a sequential execution. A hardware implementation of these mechanisms require only a modest amount of resources (likely less than 5% area) beyond a next-generation chip multiprocessor.

This dissertation includes a simulation-based evaluation of the example MSSP implementation. Performance results show that MSSP achieves speedups up to 1.75 (harmonic mean 1.25) for the SPEC2000 integer benchmarks. Performance is currently limited by the effectiveness of code approximation, which can likely be significantly improved.

# Acknowledgments

Before I selected Guri to be my adviser, I asked him what was involved in doing a Ph.D. His response was "you have to go through hell." Although perhaps a slight exaggeration, there is no doubt that the worst times are made bearable and the best times genuinely memorable by the people in our lives.

First and foremost in this regard is family. My deepest thanks go to my wife Julie and my son Brian for being loving and supportive throughout the whole process. You two are my life. I thank also my parents Stephen and Connie, my brother Karl, and Julie's parents George and Jan for their constant encouragement and understanding.

I thank Guri for helping me find important and challenging problems to solve and the perspective to develop the solutions. There is no measure to the extent he has shaped my technical thinking; he has a unique ability to seek out what is critical. I also appreciate the freedom he has given me to develop my own vision and the self confidence to follow it.

I'd also like to thank the other members of my committees--Ras Bodik, Charlie Fischer, Jim Goodman, Mark Hill, and Jim Smith--for their contributions to my personal development and the development of this dissertation. In particular, I'd like to thank Ras for his constructive criticism and encouragement and his effort to push me to formalize my thinking.

Much of my development as a researcher is the result of the academic community to which I belonged. The architecture group at Wisconsin is at once technically ruthless and personally supportive. The faculty should be congratulated on the environment they have created. I have benefited from many of the students of this community, but a few of them deserve special acknowledgment.

I want to thank Eric Rotenberg for jump starting my involvement in architecture by engaging me in full-contact technical discussions in my first term at Wisconsin. I also benefited in these early years from discussions with Andy Glew, Quinn Jacobsen, Timothy Heil, S. Subramanya Sastry, and the members of the Kestrel project. In addition, I want to thank Andreas Moshovos for advising me on the workings of graduate school.

In my later years, it was Adam Butts, Brian Fields, Milo Martin, Ravi Rajwar, Amir Roth, and Dan Sorin who were my "go-to guys." They helped me refine my thinking, writing, and presentation skills. In addition, Milo Martin, my office-mate of 5 years, both tolerated my odious personal habits and taught me most everything I know about multiprocessors. I like you, Milo, even if nobody else does. Amir Roth deserves my special thanks for helping me to organize my writing and not pushing me off the chair lift.

Lastly, I would like to acknowlege the organizations that made this research possible. I thank the National Science Foundation, Intel Corporation, and Cisco Systems for the fellowships that funded much of my graduate studies and addition support from NSF grants CCR-9900584 and EIA-0071924. In addition, thanks go to the Condor project and the Computer Systems Lab at Wisconsin for providing the infrastructure for doing my research.

# **Table of Contents**

| Abstract                                                            | 1     |

|---------------------------------------------------------------------|-------|

| Acknowledgments                                                     | ii    |

| Table of Contents                                                   | . iii |

| List of Figures                                                     | . vi  |

| List of Tables                                                      | viii  |

| Chapter 1 Introduction                                              | 1     |

| 1.1 Constraints Guiding the Development of the Execution Paradigm   | . 1   |

| 1.2 Overview of Master/Slave Speculative Parallelism                |       |

| 1.3 Contributions of this Dissertation                              |       |

| 1.4 Organization of the Dissertation                                | . 5   |

| Chapter 2 The Master/Slave Speculative Parallelization Paradigm     | 6     |

| 2.1 Programs and Parallelization                                    | . 6   |

| 2.1.1 Programs as Operations and Dependences                        | . 6   |

| 2.1.2 Parallelizing Programs: Partitioning into Tasks               | . 7   |

| 2.1.3 Handling Inter-Task Dependences                               | . 9   |

| 2.1.4 Verification of Speculatively Satisfied Dependences           | 11    |

| 2.2 Master/Slave Speculative Parallelization and Distilled Programs | 13    |

| 2.2.1 Checkpoint Speculative Parallelization Paradigms              | 13    |

| 2.2.2 Approximating Code and Distilled Programs                     | 14    |

| 2.2.3 Master/Slave Speculative Parallelization                      | 15    |

| 2.2.4 MSSP Exception Model                                          | 16    |

| 2.2.5 Distilled Program Construction Example                        | 16    |

| 2.2.6 MSSP Execution Example                                        | 19    |

| 2.3 Related Work                                                    | 22    |

| 2.3.1 Speculative Parallelization (SP)                              | 22    |

| 2.3.2 Leader/Follower Architectures                                 | 23    |

| 2.3.3 Speculative Program Optimizations/Transformations             | 24    |

| 2.3.4 Dynamic Optimization Systems                                  | 25    |

| 2.4 Chapter Summary                                                 | 25    |

| Chapter 3 Approximate Code and Constructing Distilled Programs      | 27    |

| 3.1 "Requirements" of the Distilled Program                         | 27    |

|       |                                                                        | iv |

|-------|------------------------------------------------------------------------|----|

| 3.2   | 2 Selecting Task Boundaries                                            | 28 |

|       | 3.2.1 Task Size                                                        | 28 |

|       | 3.2.2 Task Boundary Locations                                          | 29 |

|       | 3.2.3 Specifying Task Ends and Task End Suppression                    | 30 |

|       | 3.2.4 Task Selection Implementation                                    | 30 |

| 3.3   | B Distilled Program Structure                                          | 33 |

|       | 3.3.1 Mapping Between Programs                                         | 33 |

|       | 3.3.2 Transition Code                                                  | 34 |

|       | 3.3.3 Resulting Structure                                              | 35 |

| 3.4   | Framework for Automatic Program Distillation                           | 36 |

|       | 3.4.1 Guiding Root Optimizations with Profile Information              | 37 |

|       | 3.4.2 Implications of Distilled Program Structure on Liveness Analysis | 38 |

| 3.5   | 5 Implementation                                                       | 38 |

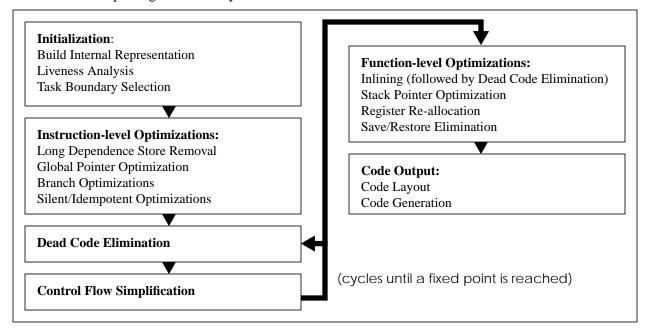

|       | 3.5.1 Initialization                                                   | 39 |

|       | 3.5.2 Instruction-level Optimizations                                  |    |

|       | 3.5.3 Dead Code Elimination and Control-Flow Simplification            | 40 |

|       | 3.5.4 Function-level Optimizations                                     | 41 |

|       | 3.5.5 Code Output                                                      | 41 |

|       | 3.5.6 Performance                                                      | 42 |

| 3.6   | 5 Chapter Summary                                                      | 42 |

|       |                                                                        |    |

| Chapt | ter 4 Implementing the MSSP Paradigm                                   | 43 |

| 4.1   | Required Functionality                                                 | 43 |

| 4.2   | 2 Analytical Model                                                     | 44 |

| 4.3   | A Guiding Theme: Tolerating Inter-processor Communication Latency      | 46 |

| 4.4   | 4 An MSSP Implementation                                               | 47 |

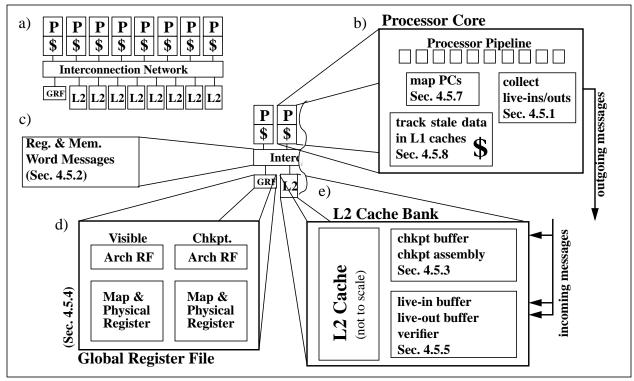

|       | 4.4.1 Mechanism Overviews                                              | 48 |

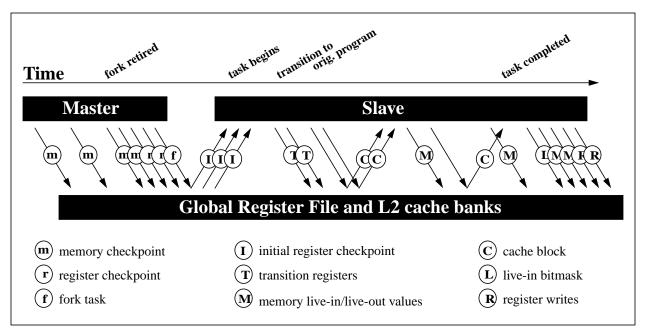

|       | 4.4.2 High-level Operation:                                            | 49 |

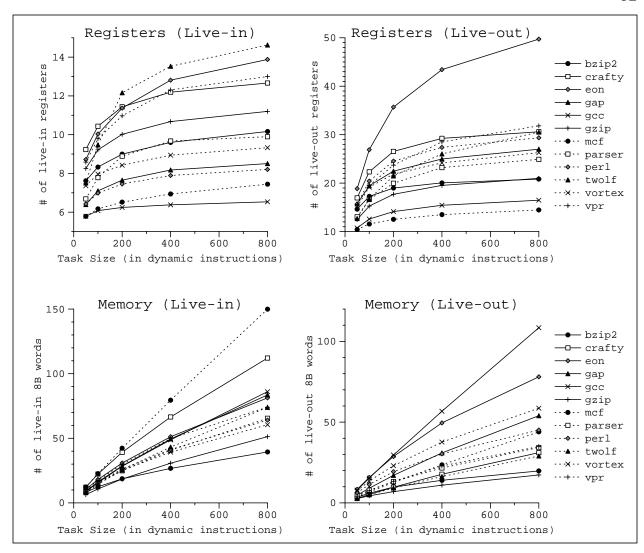

|       | 4.4.3 Program Data That Validates This Approach                        | 51 |

|       | 4.4.4 Power Consumption                                                | 55 |

| 4.5   | 5 Mechanism Details                                                    | 56 |

|       | 4.5.1 Live-in/Live-out Collection                                      | 56 |

|       | 4.5.2 Register/Memory Word Messaging                                   | 58 |

|       | 4.5.3 Memory Checkpoint Assembly                                       | 58 |

|       | 4.5.4 Global Register File                                             | 59 |

|       | 4.5.5 Verification/Commitment                                          | 60 |

|       | 4.5.6 Misspeculation Detection/Recovery Path                           | 61 |

|                                                                     | $\mathbf{v}$ |

|---------------------------------------------------------------------|--------------|

| 4.5.7 Mechanisms for Mapping Between Programs                       | 62           |

| 4.5.8 Tracking Stale Data and Refreshing                            | 63           |

| 4.5.9 Efficiently Communicating, Reading and Writing Register Files | 64           |

| 4.5.10 Early Verification                                           | 64           |

| 4.6 Chapter Summary                                                 | 65           |

| Chapter 5 Experimental Evaluation of the MSSP Paradigm              | 66           |

| 5.1 Experimental Methodology                                        | 66           |

| 5.1.1 Program Distiller Implementation                              | 66           |

| 5.1.2 Simulation Infrastructure                                     | 66           |

| 5.1.3 Benchmark Programs                                            | 68           |

| 5.2 Results                                                         | 68           |

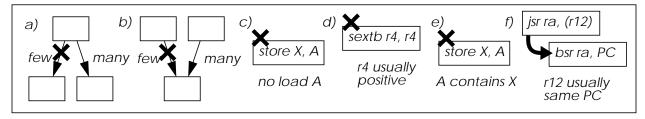

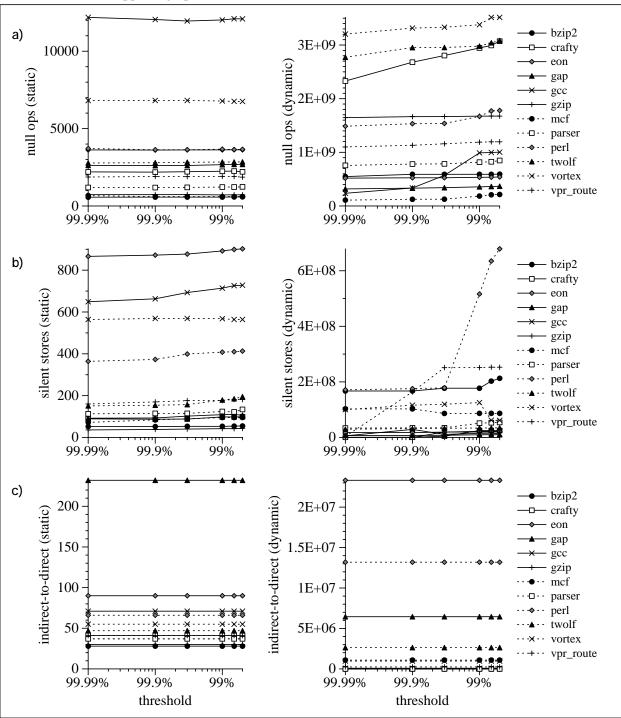

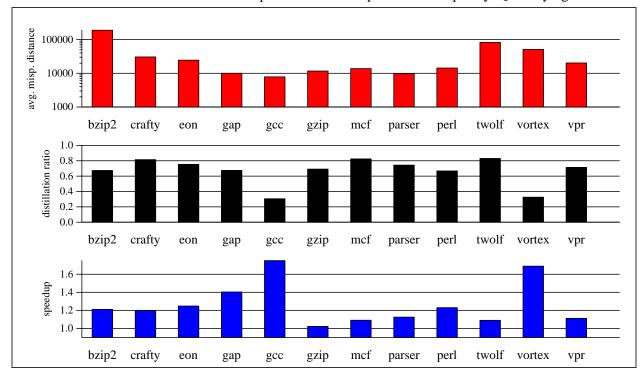

| 5.2.1 Distilled Program Optimizations                               | 70           |

| 5.2.2 Task Selection                                                | 73           |

| 5.2.3 Hardware Resource Utilization                                 | 74           |

| 5.2.4 Mapping                                                       | 76           |

| 5.2.5 Performance                                                   | 77           |

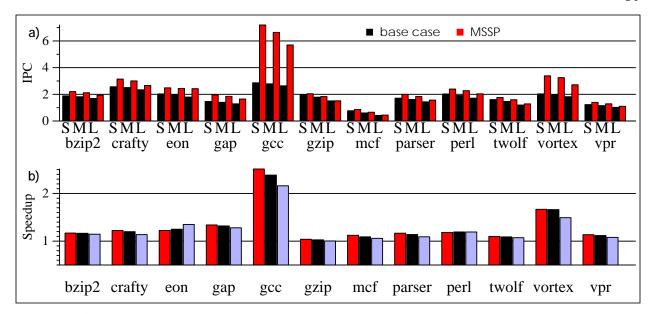

| 5.2.6 Sensitivity to Interconnect Latency/Bandwidth                 | 79           |

| 5.2.7 Sensitivity to Task Size                                      | 81           |

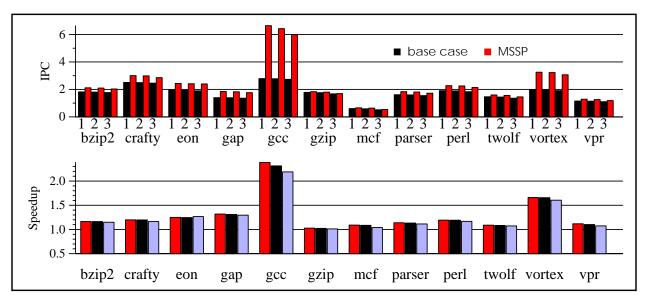

| 5.2.8 Sensitivity to Task Boundary Selection                        | 82           |

| 5.2.9 Sensitivity to Optimization Thresholds                        | 83           |

| 5.2.10 Sensitivity to Number of Processors                          | 84           |

| 5.2.11 Sensitivity to Refreshing                                    | 84           |

| 5.2.12 Sensitivity to a Realistic Mapping Lookaside Buffer (MLB)    | 84           |

| 5.3 Chapter Summary                                                 | 85           |

| Chapter 6 Conclusions                                               | 86           |

| 6.1 Lessons Learned                                                 | 86           |

| 6.2 Requirements for Correct Execution                              | 87           |

| 6.2.1 Mechanisms That Must Be Correct                               | 88           |

| 6.2.2 Mechanisms That Don't Need To Be Correct                      | 88           |

| 6.3 Open Questions                                                  | 89           |

| 6.4 Chapter Summary                                                 | 90           |

| References                                                          | 91           |

# **List of Figures**

| 1.1  | Master processor distributes checkpoints to slaves                                                | . 3 |

|------|---------------------------------------------------------------------------------------------------|-----|

| 2.1  | Examples of register, memory, and control dependences on four classes of instructions             | . 7 |

| 2.2  | Example Execution Dependence Graph (EDG)                                                          | . 8 |

| 2.3  | Control flow graph with task boundaries (a), and resulting potential tasks (b)                    | . 9 |

| 2.4  | The program's execution can be divided into three regions                                         | . 9 |

| 2.5  | Example partition of EDG with annotated dependences                                               | 10  |

| 2.6  | Three techniques for satisfying dependences                                                       |     |

| 2.7  | Alternatives for short dependences in speculative parallel architectures                          | 12  |

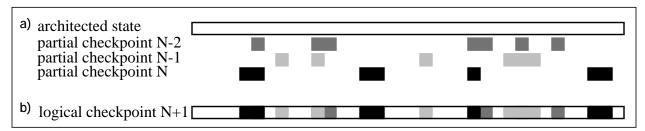

| 2.8  | A live-in checkpoint is assembled from partial checkpoints                                        | 13  |

| 2.9  | Example code fragment from SPEC 2000 benchmark gcc                                                | 16  |

| 2.10 | Example task selection and application of root optimizations                                      | 17  |

| 2.11 | Logical steps in constructing a distilled program                                                 | 17  |

| 2.12 | Distilled program fragment after application of root optimizations                                | 18  |

| 2.13 | Distilled version of example code fragment:                                                       | 19  |

| 2.14 | Flow chart of MSSP execution                                                                      |     |

| 2.15 | Detailed example MSSP execution                                                                   | 21  |

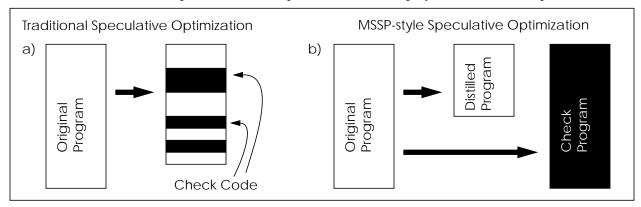

| 2.16 | Traditional vs. MSSP-style speculative optimization                                               | 24  |

| 3.1  | Top-level algorithm pseudocode for selecting tasks                                                | 30  |

| 3.2  | Task selection algorithm example                                                                  | 31  |

| 3.3  | Algorithm pseudocode for creating acyclic regions for task selection                              | 32  |

| 3.4  | Algorithm pseudocode for selecting potential task boundaries to promote                           | 32  |

| 3.5  | Code hoisted across a fork instruction is replicated in the transition code                       | 34  |

| 3.6  | Code can be percolated down into transition code if used only in one task of the original program | ı35 |

| 3.7  | The distilled program structure supports checkpointing and misspeculation recovery                | 36  |

| 3.8  | Summary of root and supporting optimizations                                                      | 37  |

| 3.9  | Overview of phases of program distiller implementation                                            | 39  |

| 4.1  | Performance predicted by the analytical model                                                     | 46  |

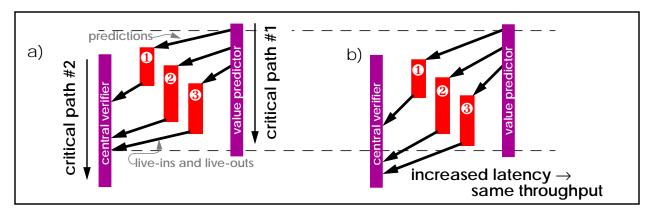

| 4.2  | Critical path through the MSSP execution                                                          |     |

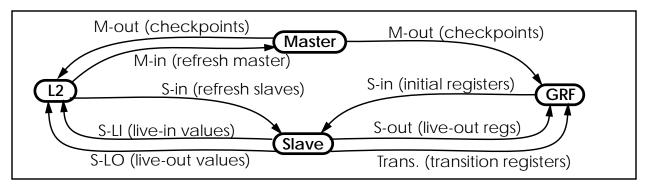

| 4.3  | Block diagram of the MSSP hardware                                                                | 48  |

| 4.4  | Life of a single task (steady state operation of MSSP)                                            | 50  |

| 4.5  | Characterization of task live-in and live-out set sizes                                           | 52  |

| 4.6  | Graphical representation of flow of register and memory data                                      |     |

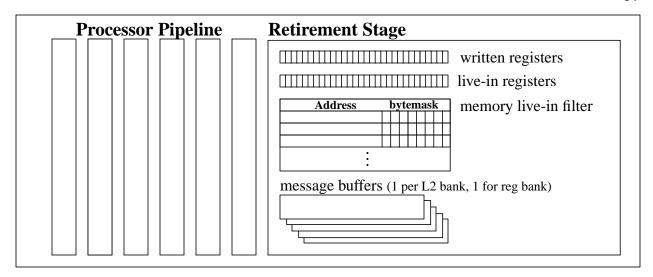

| 4.7  | Hardware structures for collecting live-in and live-out values                                    | 57  |

| 4.8  | Packet formats for sending memory words and register values through interconnection networks      | 58  |

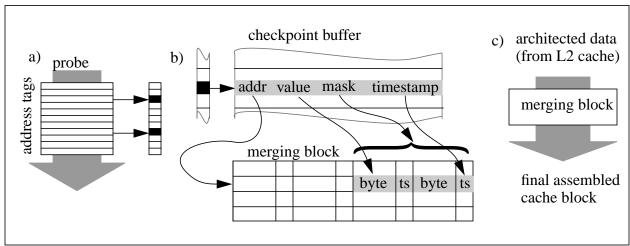

| 4.9  | Checkpoint assembly from entries of the checkpoint buffer                                         | 59  |

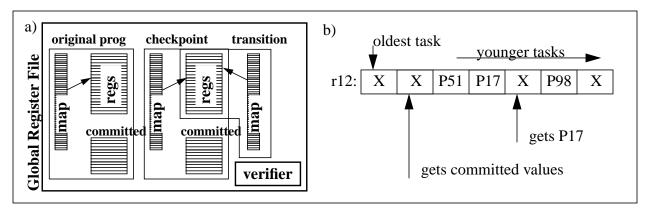

| 4.10 | Detail of global register file implementation                                                     | 60  |

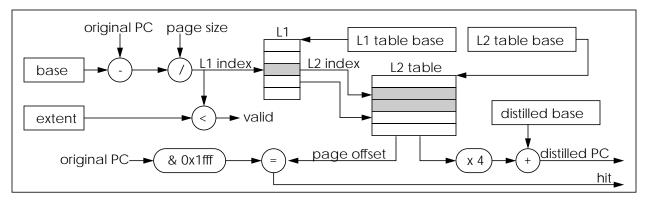

| 4.11 | A sparse page table implementation for mapping                                                    | 63  |

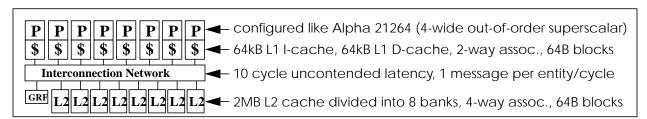

| 5.1  | Diagram of machine model                                                                          |     |

| 5.2  | Root optimizations represented pictorially                                                        |     |

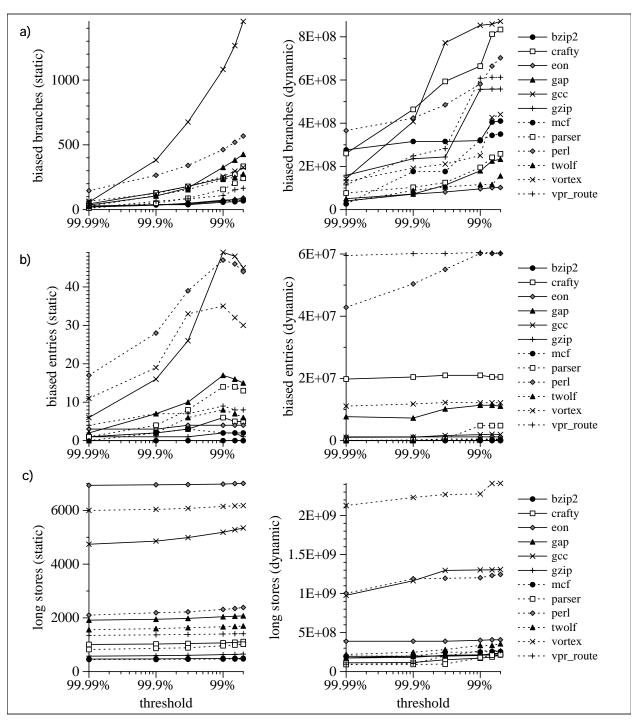

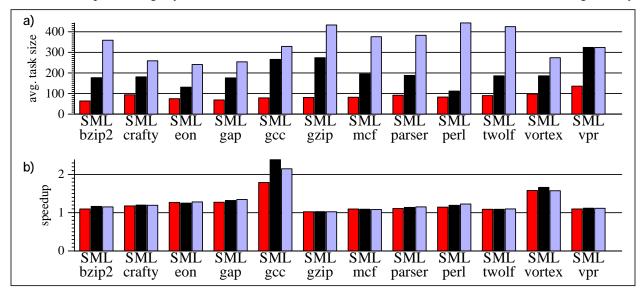

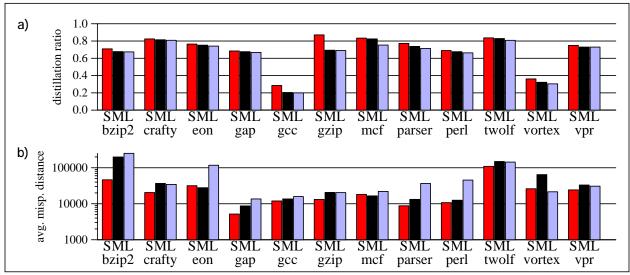

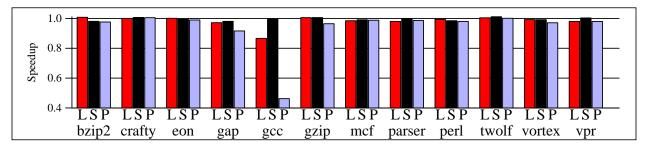

| 5.3  | Effectiveness of root optimizations(2)                                                            |     |

| 5.4  | Effectiveness of root optimizations(1)                                                            |     |

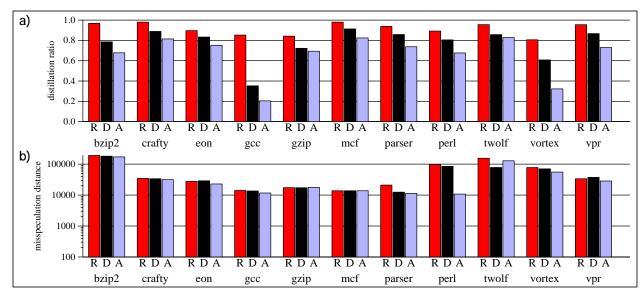

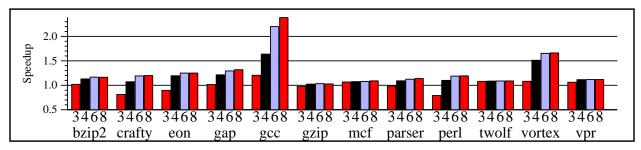

| 5.5  | Relative effect of root and supporting optimizations                                              | 73  |

|      |                                                                        | vii  |

|------|------------------------------------------------------------------------|------|

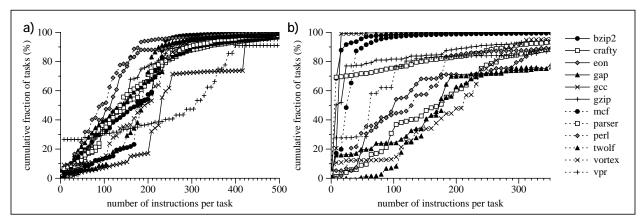

| 5.6  | Task size distributions, with and without task boundary suppression    | 73   |

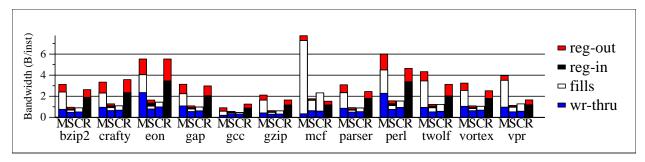

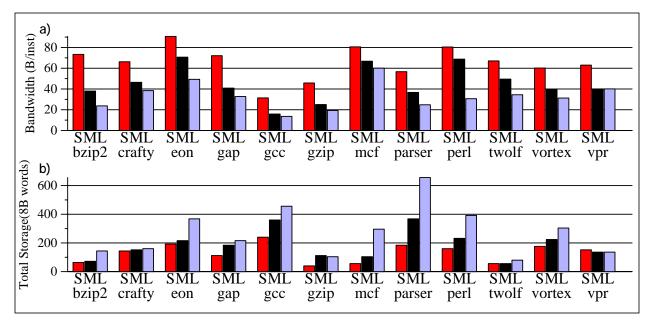

| 5.7  | Bandwidth utilized                                                     | . 75 |

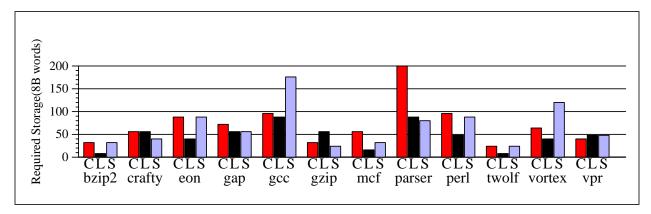

| 5.8  | Amount of speculative state storage required                           | 75   |

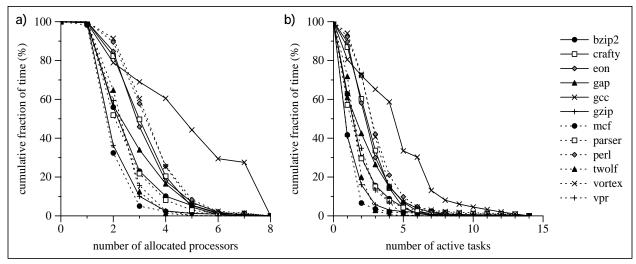

| 5.9  | Processor utilization and task activity distribution:                  | 75   |

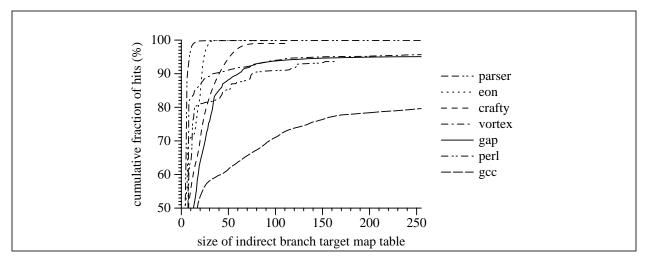

| 5.10 | Hit ratio of as a function of indirect branch target map size          | . 76 |

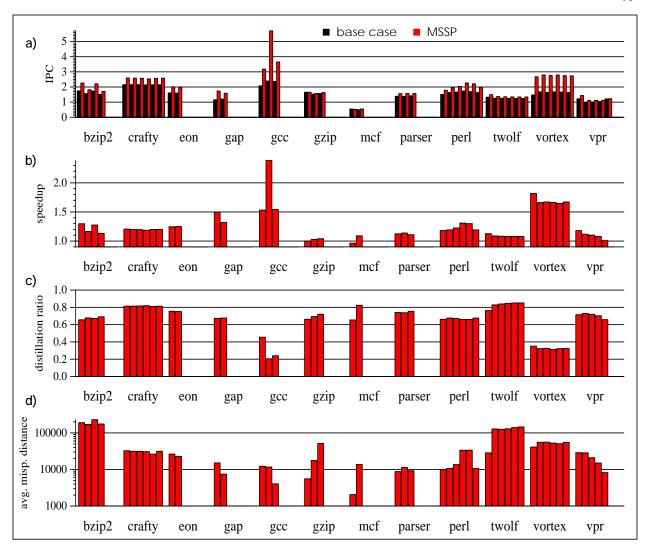

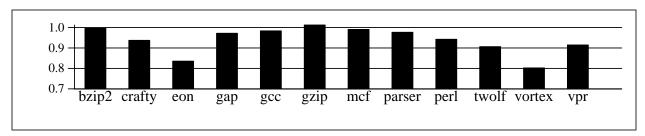

| 5.11 | MSSP Performance across the whole program's execution                  | 77   |

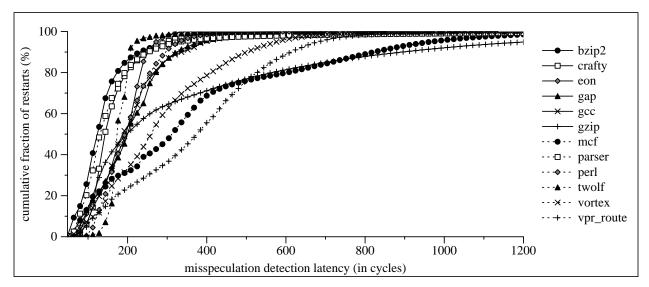

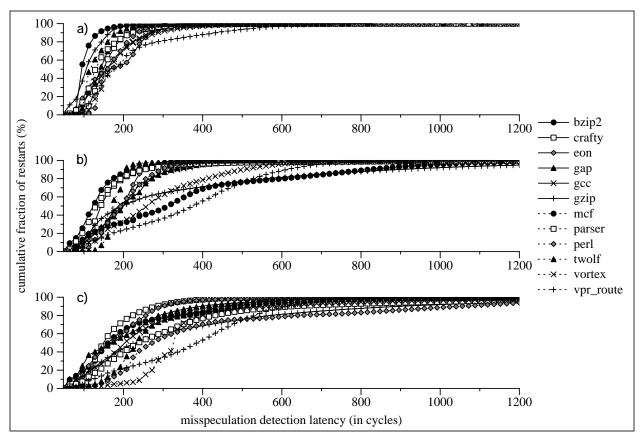

| 5.12 | Task misspeculation detection latency                                  | . 78 |

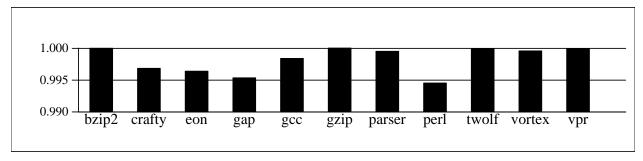

| 5.13 | Performance variation across execution                                 | . 79 |

| 5.14 | Limited sensitivity to inter-processor communication latency           | . 80 |

| 5.15 | Limited sensitivity of inter-processor bandwidth on performance        | . 80 |

| 5.16 | Sensitivity of task size on performance                                | . 81 |

| 5.17 | Impact of task size on distillation ratio and misspeculation frequency | . 81 |

| 5.18 | Sensitivity of task size on task misspeculation detection latency      | 82   |

| 5.19 | Sensitivity of task size on bandwidth and storage requirements         | . 83 |

| 5.20 | Sensitivity of performance on task boundary selection                  | . 83 |

| 5.21 | Sensitivity of distillation thresholds on performance                  | . 84 |

| 5.22 | Sensitivity of performance on number of available processors           | . 84 |

| 5.23 | Sensitivity to refreshing                                              | . 85 |

| 5.24 | Sensitivity indirect branch target mapping                             | . 85 |

|      |                                                                        |      |

# **List of Tables**

| 3.1 | Correctness thresholds for program distiller optimizations                                                                                                       | . 38 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.1 | Raw data on average number of 64-bit registers, 64B cache lines for refreshes, and 8B memory words moved for tasks of different sizes, estimated from Figure 4.5 | . 52 |

| 4.2 | Estimated bandwidths calculated from raw data in Table 4.1                                                                                                       | . 53 |

| 5.1 | Baseline parameters supplied to the program distiller                                                                                                            | . 67 |

| 5.2 | Simulation parameters approximating a CMP of Alpha 21264 cores                                                                                                   | . 68 |

| 5.3 | Input sets used for simulation of Spec 2000 integer benchmarks                                                                                                   | . 69 |

| 5.4 | Distilled program statistics                                                                                                                                     | . 74 |

| 5.5 | Number of indirect branches per 1000 dynamic (original program) instructions                                                                                     | . 77 |

# Chapter 1

#### Introduction

The exponential growth of processor performance has enabled single-processor computers to achieve execution rates in the billions of operations per second and multiprocessor computers capable of hundreds of billions or even trillions of operations per second. Despite these achievements, there remains a desire to have even faster computers that will enable additional software functionality and achieve these performance levels in smaller, cheaper form factors that consume less power.

Advances in semiconductor technology continues to provide the raw materials for continued performance growth, providing larger chips capable of holding more and faster transistors. There remains a challenge though, in how to utilize these resources in a manner that improves performance. Extrapolation of previously used techniques (*e.g.*, naively increasing superscalar width) does not "scale up" efficiently due to clock cycle constraints [57] and true dependences—both control and data—in programs, especially non-numeric programs. Benefitting fully from larger transistor budgets necessitates the development of new execution paradigms to enhance and exploit parallelism. In this dissertation, I propose one such paradigm, Master/Slave Speculative Parallelization (MSSP).

#### 1.1 Constraints Guiding the Development of the Execution Paradigm

Before describing the MSSP paradigm in detail, it is illuminating to discuss the constraints, both physical and social, that I perceived would affect the adoption of a new execution paradigm. These constraints shaped the development of the MSSP paradigm. Five constraints—wire delay, programmer productivity, infrastructure transparency, minimal verification complexity, and flexibility—are described in the following paragraphs.

Wire delay: As clock frequencies increase, the distance a signal can travel in a single cycle decreases. With slow global communication, de-centralized microarchitectures consisting of many loosely-coupled regions are desirable. Designing such architectures can be difficult because partitioning programs so they can be efficiently mapped onto such hardware is a challenging, open problem. Control and data dependences between operations necessitates enforcing some ordering constraints on the operations and facilitating communication between them.

Thesis: A new execution paradigm should provide an efficient means of partitioning programs for mapping onto decentralized microarchitectures.

**Programmer Productivity:** In the early days of computing, computers were so few in number and so expensive that it was appropriate for programmers to hand optimize code to achieve the most benefit from a limited resource. Declining component costs have made computers ubiquitous and cheap, making programmers the limiting resource. Modern computer designers cannot rely on programmers to hand optimize their code—including techniques like manual parallelization—except in performance critical domains (*e.g.*, database server applications). Most programmers are likely to program in a way that maximizes their productivity by using high-level languages and methodologies that favor clarity, verifiability, reusability, and maintainability over performance.

Thesis: A new execution paradigm should handle compiled code well and be tolerant of the manner a computation is expressed. In the limit, the intrinsic complexity of computation should determine execution time, not the manner in which it is expressed.

**Infrastructure Transparency:** Widespread adoption of any technology is slowed if its deployment requires outside entities to change. For processor design teams, such outside entities include compiler vendors, operating system vendors, programmers, and library writers. Requiring changes in the compiler or that programmers change their methodology can take a long time and can be risky. It is much preferable if technology can be introduced in such a manner that it is transparent to the existing infrastructure.

Thesis: A new execution paradigm should be language agnostic, require few, if any, changes to the compiler or operating system, and, therefore, handle legacy code.

**Minimal Verification Complexity:** Much of the cost/effort/time in the development of a modern micro-processor is dedicated to verification. As such, it is desirable to develop micro-architectural techniques that reduce verification complexity or at worst increase it minimally.

Thesis: A new execution paradigm should minimize any additional verification complexity.

**Flexibility:** The above constraints have expounded on the importance of not *requiring* changes to compiler infrastructure or programmer behavior, but it is desirable that if beneficial changes are made they can be exploited. For example, if code is manually parallelized or hand assembled to expose a lot of explicit parallelism, the machine can provide the necessary resources. Thus it is desirable for the micro-architecture to be largely composed of general purpose execution resources (processors, functional units, caches, etc.) rather than special-purpose widgets that will be idle when an alternative execution paradigm is used.

Thesis: A new execution paradigm should require a minimum of special purpose widgets.

In the next subsection, I briefly overview the proposed execution paradigm and how it addresses these perceived constraints.

#### 1.2 Overview of Master/Slave Speculative Parallelism

This dissertation describes the Master/Slave Speculative Parallelization (MSSP) paradigm. This paradigm enables the automatic parallelization of sequential programs, including legacy binaries. This parallelization is effected by dedicating one processor to be the "master<sup>1</sup>," who orchestrates the parallel execution by (1) instructing each "slave" processor where (*i.e.*, at what program counter value) to begin executing and (2) providing each slave processor with the set of live-in values needed to execute the assigned segment (or "task") of the program.

<sup>1.</sup> The use of the word "master" comes from the definition "a device or mechanism that controls the operation of another" and not from the connotation of a master copy from which other copies are made (e.g., phonograph records).

The master processor—to which I will refer simply as the master—performs its duties by executing what I call a distilled program. The distilled program is an "approximate" version of the original sequential program that has been augmented with directives for managing the slave processors. The distilled program's approximate nature allows it to execute more quickly than the original program, but it may occasionally diverge from a correct execution. By coupling the master's execution of the distilled program with the slaves' execution of the original program, MSSP can potentially achieve the superior performance of the distilled program with the correctness of the original program.

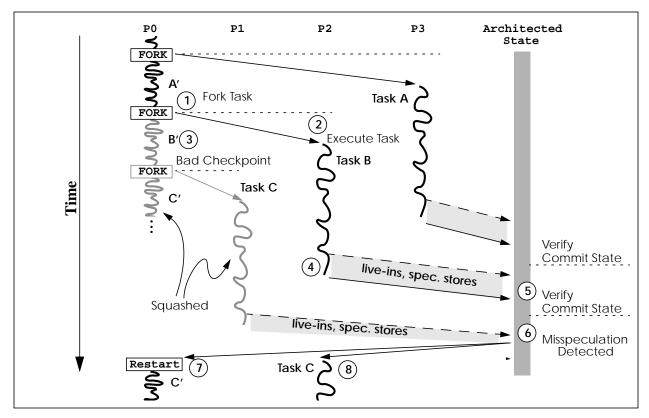

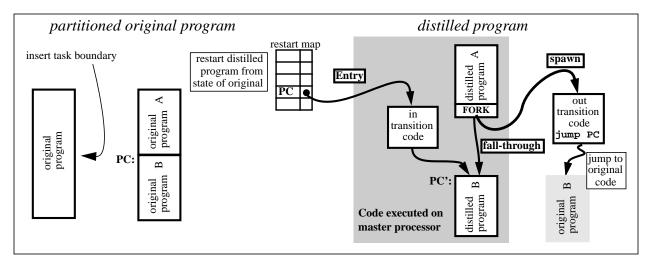

I briefly overview the MSSP paradigm in Figure 1.1. Four processors are shown; one (P0) is allocated to be the master processor, and the rest (P1, P2, and P3) are slaves that begin the example idle. By executing the distilled program, the master processor performs many of the register and memory writes that the original program would, but these writes are not committed. Instead, these writes are used to create a predicted checkpoint of program state to be used by the slave processors and are held in a special "checkpoint" buffer. At task boundaries in the distilled program there are fork instructions that signal the master to spawn a new task in the original program on a free processor and to provide it access to the buffered checkpoint values. At the annotation 1 in the figure, the master processor spawns Task B onto processor P2. P2 begins executing the task after some latency due to the inter-processor communication (2). P0 continues executing (3) the distilled program segment that corresponds to Task B, which I refer to as Task B'.

As the slave **Task B** executes, it will read values that it did not write (live-in values) and perform writes of its own (live-out values). If a corresponding checkpoint value is available, it is used for the live-in value; otherwise the value is read from current visible (architected) state. As the task is speculative—it is using

Figure 1.1: Master processor distributes checkpoints to slaves. The master—executing the distilled program on processor P0—assigns tasks to slave processors, providing them with predicted live-in values in the form of checkpoints. The live-in values are verified when the previous task retires. Misspeculations, due to incorrect checkpoints, cause the master to be restarted with the correct architected state.

predicted live-in values—its live-out values cannot be immediately committed. Instead its live-in and live-out values are recorded in live-in and live-out buffers and associated with the task. When the task is complete (4), **P2** sends its live-in and live-out values to the authority on architected state. If the recorded live-in values exactly correspond to architected state, then the task has been verified and can be committed, and architected state can be updated (5) with the task's live-out values.

If one of the recorded live-in values differs from the corresponding value in the architect state (e.g., because the master wrote an incorrect value (3), this mismatch will be detected during verification. On detection of the misspeculation (6), the master is squashed, as are all other in-flight tasks. At this time, the master is restarted at C'(7), using the current architected state. In parallel, non-speculative execution of the corresponding task in the original program (Task C) begins (8).

#### 1.3 Contributions of this Dissertation

In this dissertation, I focus on three topics: the Master/Slave Speculative Parallelization paradigm, the abstract concept of approximate code, and distilled programs, the specific form of approximate code used in MSSP. In addition, with regards to the constraints discussed in Section 1.1, I demonstrate that the MSSP paradigm has the following characteristics:

- 1. By parallelizing the program into tasks and predicting their live-in values, MSSP effectively creates independent units of work—generally consisting of hundreds of dynamic instructions—that can be mapped onto a distributed micro-architecture (*e.g.*, a chip multi-processor). If live-in predictions are accurate, the MSSP paradigm can be very tolerant of communication latency.

- 2. In approximating a program, the distilled program is free to re-express computation in a manner that facilitates fast execution. Because the distilled program need not be correct in all circumstances, it is sufficient to find an expression that is correct for the "common case", potentially enabling more aggressive optimizations.

- 3. No compiler modifications are required and legacy binaries can be supported. All information needed to construct the distilled program can be derived from the original program's static image and profile information. Thus, transparent implementations that perform the distillation at run time are feasible.

- 4. The program distiller, the mechanism that constructs the distilled program, need not be verified. The unmodified original program is executed (by the slaves) and remains the authority for correct execution. All results computed by the distilled program are predictions, untrusted by the machine until verified against architected state. Thus, any bugs in the distiller translate into mispredictions, which could reduce performance but will not affect correctness.

- 5. The MSSP paradigm can be implemented as an extension to a chip multiprocessor (CMP). By implementing the distiller in software, the required MSSP-specific hardware mechanisms are modest. For example, about 4kB of storage is required at each processor (3% of the size of the caches on a processor with 64kB instruction and data caches) and around 24kB of storage at the L2 (or a little more than 1% of a 2MB L2 cache). These modest hardware requirements can also limit the incremental verification complexity beyond the CMP designs already present in industry. Furthermore, it allows processor vendors to produce a single chip that efficiently handles sequential programs (using MSSP) and parallel programs (using CMP).

In order to justify and explore the implications of the above statements, this dissertation describes the Master/Slave Speculative Parallelization paradigm. Specifically, in this dissertation, I make the following contributions:

1. I define and describe the Master/Slave Speculative Parallelization paradigm, comparing it to previously proposed execution paradigms.

- 2. I demonstrate the opportunity for approximating programs, discussing a prototype implementation of a program distiller.

- 3. I describe the necessary mechanisms for the MSSP paradigm and outline a possible implementation.

- 4. I characterize the distilled programs generated by my prototype program distiller and empirically evaluate the performance of an implementation MSSP.

#### 1.4 Organization of the Dissertation

The organization of this dissertation corresponds directly to the above contributions, where each topic is the focus of a separate chapter (Chapters 2 through 5). I conclude in Chapter 6 by describing some lessons learned during this work, the correctness requirements of the implementations, and outline some unanswered questions to guide future work.

# Chapter 2

### The Master/Slave Speculative Parallelization Paradigm

In this chapter, I define and present the Master/Slave Speculative Parallelization (MSSP) paradigm. As this is a paradigm for automatic parallelization of sequential programs, I begin the chapter (in Section 2.1) with a description of programs and program parallelization in general. In Section 2.2, I present the MSSP paradigm and introduce the concept of approximate code, including definitions and examples of each. Lastly, in Section 2.3, I compare and contrast the MSSP paradigm to previously proposed execution paradigms.

#### 2.1 Programs and Parallelization

This section begins with a brief description of the components that make up programs—operations and inter-operation dependences—and introduces the *execution dependence graph* (EDG), a tool for visualizing the important dependences. In Section 2.1.2, I demonstrate how parallelizing programs involves partitioning EDG's into tasks. In general, such a partitioning results in dependences that cross task boundaries; in Section 2.1.3, I describe the three ways that such dependences can be dealt with. Section 2.1.4 closes this section with a discussion of two mechanisms for verification if these dependences are handled speculatively.

#### 2.1.1 Programs as Operations and Dependences

This dissertation is concerned with the automatic parallelization of programs written with a sequential execution paradigm in mind. These programs consist of operations that name (either explicitly or implicitly) the storage location of their source and destination operands. Inter-operation communication is performed by matching up the producer of the value at a given storage location to the consumer of that location and results in a dependence between the two operations.

In this work, I concern myself with two classes of inter-operation dependences: true data dependences and control dependences. Anti- and output dependences can be easily alleviated by renaming storage locations and in-order retirement, respectively, so they need not be a concern.

True data dependences ensure that storage locations named by source operand contain the correct values at the time an operation is executed. For the purposes of describing parallelization paradigms, dependences through registers and memory are effectively equivalent, so I will not make this distinction.

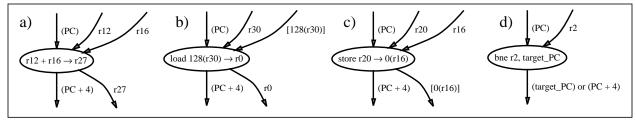

Figure 2.1: Examples of register, memory, and control dependences on four classes of instructions. (a) arithmetic, (b) load, (c) store, and (d) control.

Control dependences determine which operations are executed and, as a result, which data dependences are realized. For simplicity, I will model control dependences as data dependences by adding implicit reads and writes to the program counter (PC) for each instruction. This introduces a serial data dependence from each instruction to the next. Note that, in general, this over-constrains the inter-operation dependences, but results in little loss of generality for the discussion of program parallelization to follow. Figure 2.1 shows example operations and their dependences.

Different executions (dynamic instances) of the same (static) instruction can potentially have different dependences due to different paths through the computation or values computed upon. For a given execution of a program, I can create a graph of the dependences that were realized. This Execution Dependence Graph (EDG) is an execution trace augmented with arcs indicating the inter-operation dependences; an example EDG snippet is shown in Figure 2.2. **The EDG contains the set of dependences that need to have been observed to have correctly performed the program's execution.** The EDG differs from a control-flow graph (CFG) and a data-flow graph (DFG) in that it is concerned with what *did* happen on a particular execution, not what *could* happen on across all possible executions.

#### 2.1.2 Parallelizing Programs: Partitioning into Tasks

Although there are many levels at which parallelism can be exploited (*e.g.*, word, instruction, thread), in this dissertation I focus on thread-level parallelism (TLP). Techniques to exploit word-level parallelism (WLP) and instruction-level parallelism (ILP) have been actively researched and these forms of parallelism are being effectively exploited in existing processors (by SIMD instruction set extensions and superscalar/VLIW architectures, respectively). TLP, on the other hand, is not being exploited in most programs due to the high cost of manual parallelization, so there is significant untapped performance potential. Furthermore, because TLP exploits parallelism at a larger granularity than WLP or ILP techniques, performance benefits of exploiting TLP will likely complement performance achieved through those techniques.

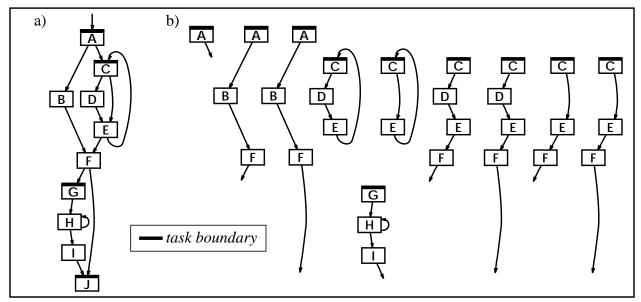

To achieve a thread-level parallel execution for a computation, I will partition it into *tasks* that can be performed in parallel by independent processors. In this work, the program is partitioned into tasks by specifying *task boundaries* with static annotations to the program, much like what was done in Multiscalar [72, 81]<sup>1</sup>. The tasks that result from these task boundaries depend on the control flow path the program follows. Figure 2.3 shows a control flow graph (CFG) of a computation with a set of task boundaries and the set of possible tasks that could arise from the execution of the computation.

**Task Boundary:** a point in the static program, generally associated with the static instructions that it precedes, that terminates a task when it is encountered during execution. (Definition 1)

**Task:** a continuous sequence of operations in the program's execution bounded at each end by a task boundary annotation in the static program, with no task boundary annotations in the task's interior. (Definition 2)

<sup>1.</sup> The difference between this definition and the one used for Multiscalar task selection [72, 81] is that there is no constraint that the tasks have a single entry.

Figure 2.2: Example Execution Dependence Graph (EDG). (a) code snippet from bzip2, and (b) the associated EDG (control dependences are not shown for clarity).

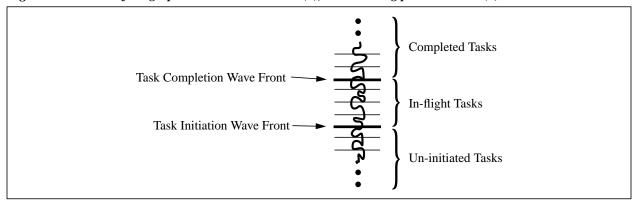

Generally, the program's execution requires the execution of a large number of dynamic tasks, but only a small number of them are *in flight* (*i.e.*, actively being executed) at any one time. As shown in Figure 2.4, a program's execution can be divided into 3 segments: 1) "the past": a segment consisting entirely of completed tasks starting at the beginning of the execution, 2) "the present": a segment of in-flight tasks<sup>2</sup>, and 3) "the future" a segment consisting of un-initiated tasks and ending at the program's completion. I'll refer to the second (middle) segment as the *task window* because it effectively moves like an instruction window down the execution.

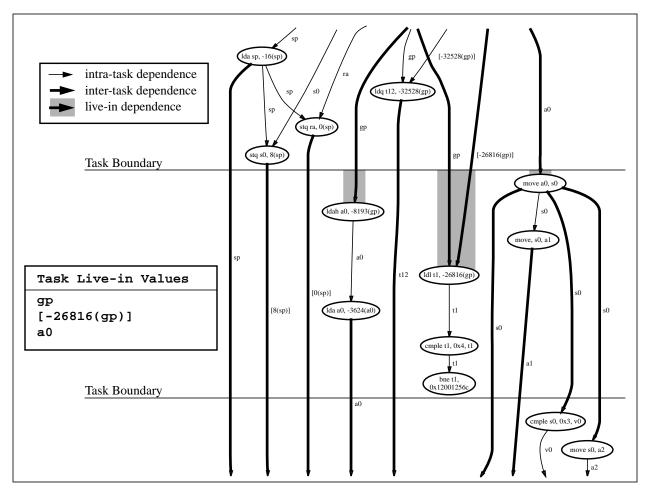

In partitioning a program into tasks, I am making horizontal cuts through the EDG, effectively selecting a set of dependency edges to become *inter-task dependences*. I will refer to the set of inter-task dependences whose consumers belong to a given task as being *live-in* to the task; a task's live-in values are those that it reads before writing. An example that classifies dependences is shown in Figure 2.5. I will refer to the state of all variables at a task boundary as a *checkpoint*; a checkpoint from the immediately proceeding task boundary is sufficient to satisfy all live-in dependences of a task.

<sup>2.</sup> Strictly speaking it is possible to have completed and un-initiated tasks in the "present" segment. More exactly this segment spans from the first in-flight or un-initiated task to the last in-flight or completed task.

Figure 2.3: Control flow graph with task boundaries (a), and resulting potential tasks (b).

Figure 2.4: The program's execution can be divided into three regions. (1) a continuous span of completed tasks starting at the program's beginning, (2) a short span of in-flight tasks, and (3) a continuous span of un-initiated tasks.

While intra-task dependences can be handled by any number of existing micro-architectural techniques, the set of live-in dependences is the responsibility of the parallelization paradigm. The set of writes (to registers or memory) that are not overwritten within the task form the set of live-out values.

#### 2.1.3 Handling Inter-Task Dependences

Before an operation with an inter-task dependence can be executed, the dependence must be satisfied. In the case of a true data dependence, this means the operand value must be supplied. In the case of a control dependence, the starting PC for a task must be supplied to identify which operation to perform. In both cases, a value must be provided to the consuming operation.

Before discussing the means of providing these values, it is important to describe one attribute of dependences: length. The *length* of a dependence is the number of dynamic instructions executed between the producing operation and the consuming operation in an in-order execution of the program. Like tasks, dependence length is a purely dynamic phenomenon, a characteristic of a pair of dynamic instructions that communicate. The length of a dependence—specifically its length relative to the size of the task window—may affect the cost of satisfying the dependence. Therefore, I make the following definitions:

Figure 2.5: Example partition of EDG with annotated dependences. Generally, the live-in set is a small fraction of the inter-task dependences crossing a task.

long dependence: a dependence with a length exceeding the task window size. (Definition 3) short dependence: a dependence with a length less than or equal to the task window size. (Definition 4)

Although this characteristic is defined with respect to a dynamic dependence, it is quite stable (across instances of the same static instruction) and predictable; the stability of very short dependences has previously been demonstrated [51]. Accurate predictions of dependence length can be exploited to select an appropriate mechanism for satisfying the dependence.

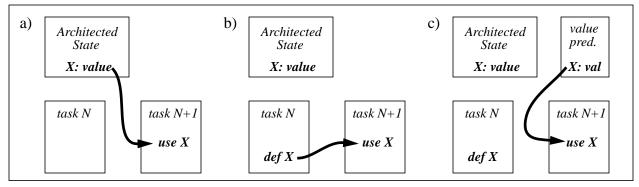

Below, I describe three ways to satisfy dependences: (1) reading the value from architected storage, (2) inter-task communication and (3) value prediction. The first mechanism is appropriate for long dependences; the other two are for short dependences. Figure 2.6 diagrams these three mechanisms.

As tasks commit instructions, they update user-visible state, also known as *architected state*. For long dependences we can be assured that the producing operation has been committed—by definition it belongs to a completed task—and that no in-flight operation is updating the storage location associated with the dependence. As a result, there is a single, unambiguous value for the name and it should be stored in the architected state. Thus, these dependences can be satisfied trivially by reading the value from the architected state.

Figure 2.6: Three techniques for satisfying dependences. (a) reading values from architected state, (b) communicating values from producing task, (c) predicting value with value predictor.

For short dependences, the task that produces the value will be in flight simultaneously with the task that consumes the value. A natural way to handle such a dependence is to have the producing task communicate the value to the consuming tasks. Generally this approach requires a synchronization mechanism, as we cannot assume that an instruction that produces a value will have completed execution before the consuming operation is considered for execution. The synchronization mechanism must identify the producing instruction and stall the consumer until that instruction has completed.

Alternatively, we can satisfy the dependence by predicting the communicated value [22, 45]. In this case, the value will not be provided from the producing task, but from a separate entity, the value predictor.

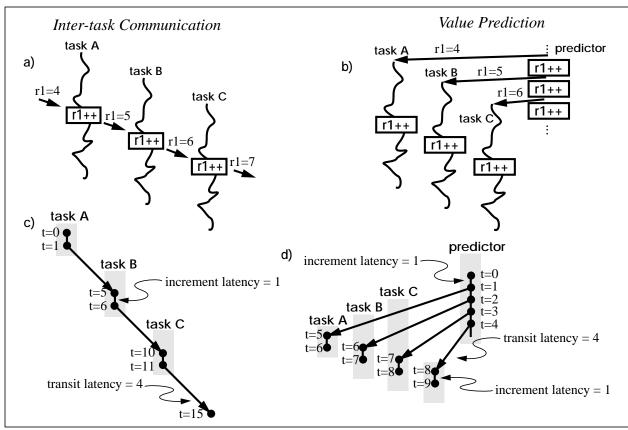

If a value can be predicted effectively, using value prediction can result in better inter-processor communication patterns than inter-task communication. Figure 2.7 illustrates this point with a simple example involving a sequence of tasks with a single communicated value. In a traditional speculative parallelization paradigm this dependence is communicated from task to task, exposing the latency of inter-processor communication between each task. In MSSP, these live-in values are produced by a centralized value predictor. Because it is centralized, no inter-processor communication is required between executions of the increment operation that generate the communicated value. As a result, the required inter-processor communication for multiple tasks can be overlapped.

#### 2.1.4 Verification of Speculatively Satisfied Dependences

Up to this point I have made no distinction between traditional and speculative parallelization techniques. Traditional parallelization techniques ensure correctness by proving that all operations that potentially have inter-task dependences that are shorter than the task window get the correct value, generally by using synchronization. Because correctness is ensured statically by construction, no run-time verification is required in these systems.

The requirements necessary to automatically construct parallel programs that could be proven correct have effectively prevented traditional parallelization of all but a few specific classes of programs. Speculative parallelization, where the process of getting the required values can be speculative, enables a broader class of programs to be parallelized. This speculation relaxes the correctness guarantees required from the compiler and substitutes run-time checks to ensure correctness. State updates need to be buffered speculatively so they can be discarded if run-time checks detect a dependency violation. There are two approaches that can be used for verification: (1) verifying dependences and (2) verifying values.

Verifying dependences requires tracking the source (*i.e.*, the producing operation or architected storage location) from which a value was retrieved and verifying that this source was in fact the correct source. This verification is generally composed of two parts: 1) selecting what appears to be the right value when the consuming operation executes, and 2) watching all writes to ensure that a more appropriate value does

Figure 2.7: Alternatives for short dependences in speculative parallel architectures. This figure shows an illustrative example, where the only inter-task dependence is due to a register-allocated counter that is incremented by each task. Live-ins can be supplied from previous in-flight tasks (a), or task live-in values can be value predicted (b). With inter-task communication, the inter-processor communication latencies are serialized (c), but with value prediction from a centralized value predictor, the latencies can be overlapped (d).

not become available. More specifically, these requirements are: 1) ensuring this source provided the most up to date (*i.e.*, latest in program order) visible (*i.e.*, earlier in program order than the consuming operation) value bound to the desired name at the time the consumer was executed, and 2) ensuring that between the consumer's execution and retirement no operation modifies the value at the desired name and is both visible to the consumer and more up to date than the source. Typically, the first requirement is verified by construction (*i.e.*, only the most up-to-date visible value can be provided) and the second by snooping the stream of state updates. Clearly this approach does not work if value prediction is used, as the original dependence is ignored.

The alternative approach is to verify the value directly, ensuring that the value that was used is the same as the one held in the named storage location at retirement time. Such a verification can be accomplished in two ways: (1) effectively re-execute all instructions at retirement, and (2) verify task live-in values. Re-execution, used in DMT[2], is certainly sufficient for verification, but may be over-kill. If intratask communication and computation can be assumed to be reliable, then it is sufficient to verify task live-in values. This approach involves recording the names and values of the data items a task has used before defining. When the previous task is complete, the current (architected) values associated with those names can be compared to the stored value.

By comparing values directly, any means for generating values (including prediction) can be supported. In addition, comparing values does not signal a misspeculation if the right value was used for the

wrong reason. Research [43, 55, 78] has shown that many writes are "silent," they write a value into a storage location already containing that value. Dependence-based verification mechanisms would signal a misprediction if the storage location was read before the execution of a silent write that was earlier in program order, while value-based ones recognize that the correct value was read.

In effect, our verification and commitment is "reuse" of a block of instructions in the instruction reuse [71] sense. Said another way, the computation is being memoized [8]. The inputs and outputs of a task are packaged up, and if the input values match, then the output values can be committed to architected state.

#### 2.2 Master/Slave Speculative Parallelization and Distilled Programs

With the background and vocabulary in place, I am prepared to discuss the MSSP paradigm. I describe first (in Section 2.2.1) a broader class of execution paradigms called checkpoint speculative parallelization paradigms. Second (in Section 2.2.2), I describe the concept of approximate code and a specific form of approximate code that I call distilled programs that the MSSP paradigm uses to predict checkpoint values. Then, in Section 2.2.3, I present the MSSP paradigm itself and describe the mechanisms that it requires. Finally, I present examples of how a program fragment is approximated and how the MSSP paradigm executes the program fragment, in Sections 2.2.5 and 2.2.6.

#### 2.2.1 Checkpoint Speculative Parallelization Paradigms

I am coining the term *checkpoint speculative parallelization* for a class of execution paradigms that predominantly use value prediction to handle short inter-task dependences. When a new task is initiated these techniques logically construct a checkpoint of state as it is predicted to appear at the beginning of the task. The task can then satisfy all its live-in dependences by reading values from the checkpoint. If the checkpoint is constructed before the beginning of the task, no synchronization is required.

Though logically each task has an independent checkpoint, in practice checkpoints of neighboring tasks are largely similar, suggesting that such replication is unnecessary. In fact, since only a small number of tasks is in flight at a given time and each task generally writes only a small fraction of all architected state, most of a checkpoint is the same as architected state. Hence, only differences (*diffs*) from architected state need to be stored. Similarly, since the architected state holds the correct value for most storage locations, it is only the diffs—the values that could potentially have short dependences—that need to be predicted.

By storing the differences between each checkpoint and the previous one, the logical checkpoint for a task can be created by overlaying the checkpoint diffs of earlier in-flight tasks on the architected state in program order (see Figure 2.8). Thus, the logical checkpoint can be created on demand by using multi-version memory hardware structures like the ARB [10].

As discussed in Section 2.1.3, checkpoint-based paradigms, because they use value prediction, have the potential to be tolerant of inter-processor communication latency, but this latency tolerance can only be

Figure 2.8: A live-in checkpoint is assembled from partial checkpoints. (a) a partial checkpoint is predicted for values updated by each task, and (b) a checkpoint image for task N+1 is assembled by selecting the most recent copy of each value from the partial checkpoints and architected state.

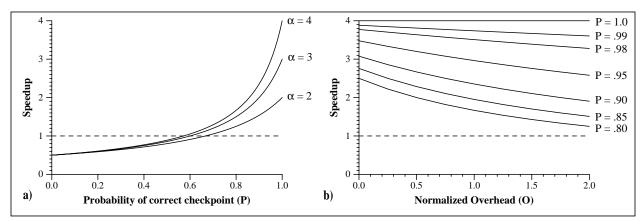

achieved if most of the live-in predictions are correct. Whenever a prediction is incorrect, the execution is serialized by an inter-processor communication to restart the value predictor with the correct architected state. In fact, an analytical model described in Section 4.2 predicts speedups increasing super-linearly with fraction of correct checkpoints. Thus, it is desirable to have near perfect prediction accuracy. Current hardware value predictors do not provide satisfactory prediction accuracy or coverage (or both) and often require large dedicated hardware structures [11, 30, 42, 45, 44, 67, 78, 82]. As a result, I instead use software, executed on a general purpose processor, to generate the necessary value predictions. Previous research has demonstrated that software can be used for accurate value prediction [18, 52, 64, 65, 66, 85].

#### 2.2.2 Approximating Code and Distilled Programs

The MSSP paradigm predicts checkpoint values by executing a *distilled program*, generated by *approximating* the original static program. The definition of approximate code is as follows:

**Approximate code:** a distinct executable computation that has a high probability, but no guarantee, of computing a desired subset of the state computed by a given piece of reference code. (**Definition 5**)

There are two important features of this definition. First, that the approximate code is not guaranteed to be functionally equivalent to the reference code. Second, the approximate code is distinct from the original code and therefore can be composed arbitrarily with respect to the reference. These two features, together, provide significant flexibility in construction of approximate code.

In return for a loss of precision, the approximate code is generally expected to have better execution characteristics. These better execution characteristics result from the large discrepancy found in many programs between what the program could do and what the program commonly does. Some examples of this discrepancy have been demonstrated:

**Program paths.** Even small programs like SpecInt95 benchmarks have more than  $2^{32}$  potential acyclic paths, but less than a thousand paths account for more than 90% of the execution [6].

**Size of points-to sets.** Points-to sets measured during an execution were 5 times smaller than conservative sets constructed statically [50].

The discrepancy between the number of potential and common case behaviors results in a similar discrepancy between the set of transformations that can be proven safe and those that are safe in practice. Since approximate code need not be correct, it can be optimized beyond what traditional code generation allows by using these additional transformations. Selecting optimizations that both improve performance and largely compute the desired values correctly is facilitated by knowledge of what behaviors the program exhibits in practice. A simple way to collect this information is to monitor the program's execution to gather profile information.

A somewhat subtle part of the definition is that the approximate code only tries to compute a subset of the values computed by the reference code. In general, we are not concerned with arriving at the exact machine state achieved by the reference code but, rather, are focused on particular values of interest. Many of the values computed by the reference code are intermediate values, and forcing the approximate code to compute these values over-constrains it.

The MSSP paradigm uses a specific form of approximate code, called a distilled program. The distilled program is used to predict task live-in values. Thus, the "desired subset of state" computed by the distilled programs are those variables involved in short inter-task dependences. Long inter-task dependence values need not be computed by the distilled program because they can be obtained by other means (*e.g.*, read from the architected state). In addition, the distilled program specifies the task boundaries to that the MSSP implementation. These two characteristics result in the following definition:

**Distilled Program:** a form of approximate code which conveys a division of the original program into tasks and computes the values associated with the resulting short inter-task dependences. (**Definition 6**)

After defining the MSSP paradigm in the next section, I present an example of how distilled programs are constructed in Section 2.2.5.

#### 2.2.3 Master/Slave Speculative Parallelization

The Master/Slave Speculative Parallelization paradigm is a checkpoint speculative parallelization paradigm, but rather than using a hardware value predictor it uses a distilled program to generate value predictions. In fact, this feature is the essence of MSSP, resulting in Definition 7. In this section, I describe the MSSP paradigm at a high level. An illustrative example of its execution is presented in Section 2.2.6.

Master/Slave Speculative Parallelization: A checkpoint speculative parallelization architecture that uses approximate code (in the form of a distilled program) to generate checkpoint value predictions. (Definition 7)

MSSP (unlike other speculative parallelization (SP) paradigms) consists of two executions of the program: the *master*, or leading, execution and the *slave* execution. The two executions use different copies of the program as they serve different purposes. The master, which is responsible for performance, executes the highly optimized, but possibly incorrect distilled program. The slave execution, which is responsible for correctness, executes code much like the code generated by existing compilers. I'll refer to this code as the original program, because in a transparent implementation of the paradigm this program would be the original binary generated by an existing compiler.

Both executions use the same architected memory state, but, because the master execution is executing a potentially flawed program, it is not allowed to update architected state. Only the slave execution is permitted to update architected state. Values created by the master are buffered speculatively and used to facilitate the execution of the slave execution.

The two executions run in close succession—the master's lead is limited by the availability of speculative buffering—so performance will be determined by the slower of the two. To achieve execution throughput equivalent to the master, additional processors can be allocated to the slave execution. If the distilled program is capable of outperforming the original program by a factor of N, then perhaps N slave processors will need to be allocated to "match the impedances" of the two executions.

The parallelization of the slave execution is orchestrated by the master execution. To break the slave execution into tasks, task boundaries in the original program are selected. At the corresponding locations, FORK instructions are inserted into the distilled program. Upon encountering one of these FORK instructions, the master execution assigns the next task to an idle slave processor.

The master provides each slave processor with a starting program counter (PC) and predictions for the live-in values the slave requires. Because the control flow in the two programs roughly corresponds, the master predicts the slave task's starting PC by mapping its own program counter (PC) from the distilled program to a task start PC in the original program. Furthermore, speculative state (e.g., register and memory values) generated by the execution of the distilled program serves as predicted live-in values for the tasks. This speculative state, along with the architected state, form a checkpoint of sorts of the program's state.

As these checkpoint values provided by the master are only predictions, the slave processor must execute speculatively until its inputs are verified. To permit this verification, the values read for live-in variables are recorded and buffered. Likewise, all side-effects of slave task execution (e.g., register writes and stores) are buffered in a live-out value buffer. At the end of a task, if its live-in values match the architected state, the task's live-outs can be committed. Mechanisms are required to buffer all of the non-architectural

data (checkpoint, live-in, and live-out values) and to correctly route it between processors. A full description of the required mechanisms, with an example implementation, can be found in Chapter 4.

Because all communication between the master and the slaves is in the form of predictions, which are verified before the slave updates architected state, there are absolutely no correctness requirements on the distilled program. This lack of correctness requirements means that the mechanism used to generate the distilled program need not be verified perfectly, as bugs can only result in performance degradation. This facilitates constructing the distilled program at run-time, when the most accurate profile information is likely to be available but verification may be costly in terms of computation or memory resources.

#### 2.2.4 MSSP Exception Model

One important feature of MSSP, is that the paradigm's functionality is a super-set of the functionality of the execution paradigm used by the underlying processor cores. For example, if an MSSP execution is composed of out-of-order superscalar processors, all of the features of traditional out-of-order superscalar processors are present. This characteristic is exploited for handling exceptions. If an exception occurs, the execution can revert back to the committed architected state (by squashing all in-flight speculative execution) and then re-execute the excepting code using the underlying execution paradigm. Thus, MSSP has no exception model of its own, just a means to revert to a traditional execution to exploit that paradigm's execution model. More detail on how exceptions are handled is covered in Section 4.5.6. Next, I demonstrate distilled program construction.

#### 2.2.5 Distilled Program Construction Example

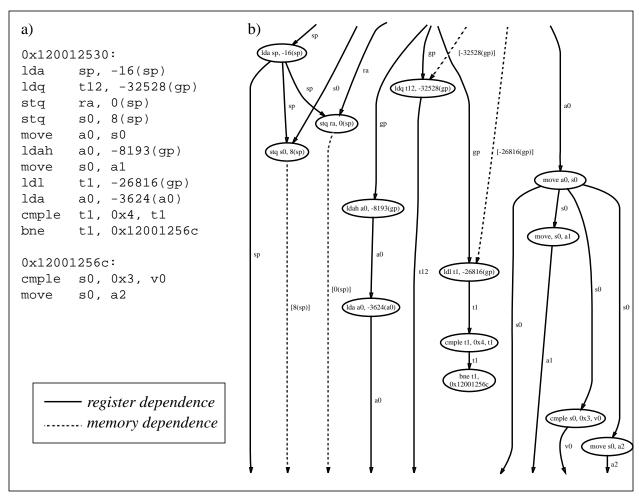

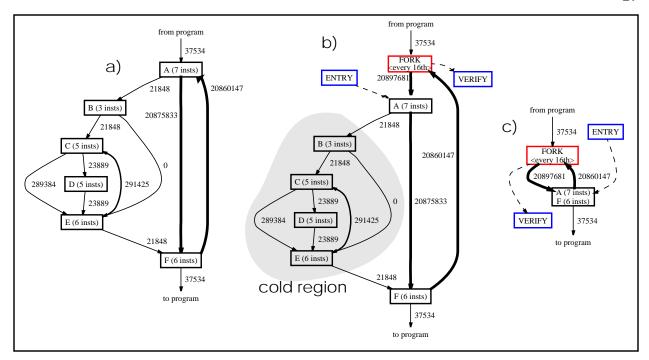

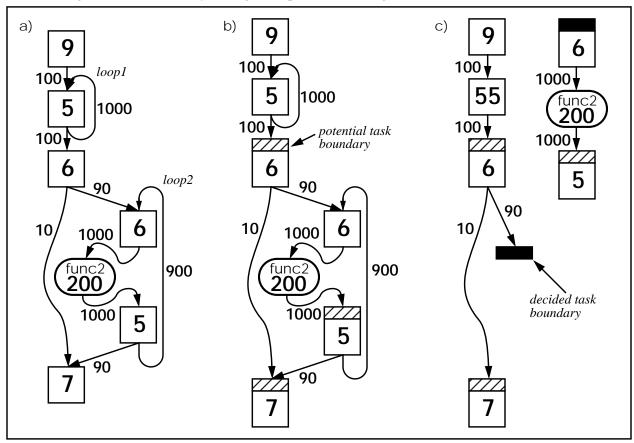

An intuitive understanding of the potential of approximate code is most easily achieved through an example. In Figure 2.9, a hot loop nest from gcc is shown. The corresponding control-flow graph (CFG) is shown in Figure 2.10a. From the execution frequency annotations on the CFG edges it can be seen that the inner loop (blocks **B**, **C**, **D**, and **E**) is only executed on 0.1% of the interations of the outer loop (blocks **A** and **F**). In approximating this code fragment, the inner loop will be removed to optimize the execution of the outer loop.

Figure 2.9: Example code fragment from SPEC 2000 benchmark gcc. Loop nest extracted from function propagate\_block, lines 1660-1678. Statements annotated with the control flow block to which they belong; blocks E and F perform the loop counter increment and test for the inner and outer loops, respectively.

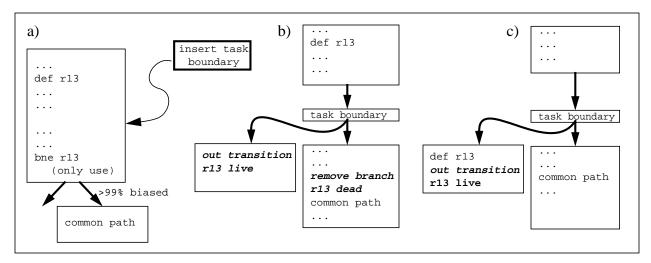

Figure 2.10: Example task selection and application of root optimizations. The control flow graph for this code example is shown for: (a) the original code, (b) the code after it has been transformed to include a task boundary, and (c) after the cold code region has been removed.

Constructing the distilled program consists of a series of steps, shown in Figure 2.11. For this example, the only profile information needed are the previously mentioned edge frequencies. The internal representation is constructed by reading the instructions from the program's memory image. Task selection is described in detail in Section 3.2. For this example it is sufficient to say that inner loop iterations are too small (11 dynamic instructions on average), so outer loop iterations are used for tasks, with a task boundary inserted at the loop header. In fact, even outer loop iterations are too small (13 dynamic instructions on average), so the task boundary is annotated to pack 16 iterations into a task.

When tasks are selected the control flow structure of the internal representation is transformed to include additional blocks. For each task boundary, three blocks are added: a fork block, a verify block, and an entry block. The fork block will contain a FORK instruction that signals to the master processor to allocate a slave processor to begin executing at the corresponding verify block. The entry block is used—after a task misspeculation has occurred—to jump start the master execution using the original program's state.

Next the program distiller performs a liveness analysis on the original code to determine the set of values that are live across the fork block. This set of values will need to be preserved even if all of their uses in

- 1. collect profile information

- 2. build internal representation (IR)

- 3. select task boundaries

- 4. perform liveness analysis

- 5. apply (speculative) root optimizations

- 6. apply (non-speculative) supporting optimizations

- 7. layout and generate code

Figure 2.11: Logical steps in constructing a distilled program.

```

live before A: t0 (&live[i]), t3 (&maxlive[i]), t12 (i)

A:

t6, 0(t3)

ldl

#1 load maxlive[i]

ldl

t2, 0(t0)

#2 load live[i]

t12, 0x3, t11

#3 truncate i to 16b

zapnot

bis

zero, zero, ra

#4 regno = 0

zero, zero, t9

#5 regno = 0

bis

t2, t6, t2

#6 diff = live[i] & ~maxlive[i]

bic

SINGLE TARGET

#7 if (diff)

bea

t2. F

F:

t12, 0x1, t12

#1 i ++

addl

lda

t0, 4(t0)

#2 &live[i]

lda

t3, 4(t3)

#3 &maxlive[i]

ldl

s3, -10104(gp)

LOOP INVARIANT

#4 load regset size

cmplt

t12, s3, s3

#5 i < regset size

bne

s3, A

#6 loop back-edge

```

Figure 2.12: Distilled program fragment after application of root optimizations. Branch A7 is unnecessary as block A has a single successor block. A3-A5 are instructions hoisted out of the inner loop, which are now dead. Removal of A7 results in A1, A2, and A6 becoming dead. Instruction F4 is loop invariant.

the distilled program are removed, as they may contribute to the live-in set of tasks in the original program spawned at this task boundary. The relevant live-in values for this example are shown at the top of Figure 2.12.

After liveness analysis, the next step is to apply root optimizations. These are optimizations that would be unsafe to apply to traditionally generated code, but are used in approximate code to remove uncommoncase behaviors that prevent optimization of common-case paths. In this example, the inner loop (labelled the cold region in Figure 2.10b) is removed from the distilled program. Eliminating this path may result in task misspeculations when this path is executed by the original program but greatly simplifies the CFG of the remaining code (Figure 2.10c). Once the inner loop is removed, outer-loop blocks **A** and **F** can be unified with no further loss of precision.

Application of the root optimizations creates new opportunities for traditional safe optimization (what I call supporting optimizations in this dissertation). The code that remains after the inner loop has been removed is shown in Figure 2.12. Traditional analysis can detect that both paths from branch A7 lead to block F and that instructions A1-A6 are dead; all of these instructions are removed from the distilled program. In addition, instruction F4 is detected to be loop invariant, so it can be hoisted out of the loop.

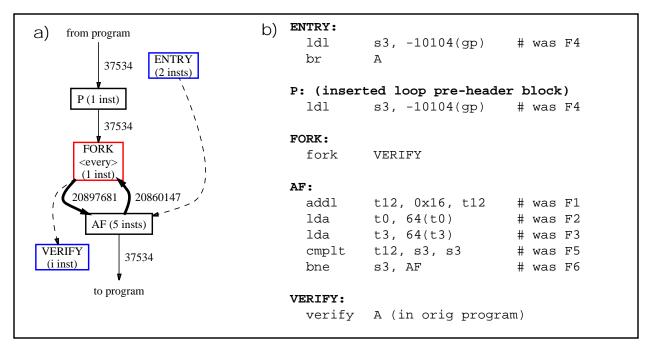

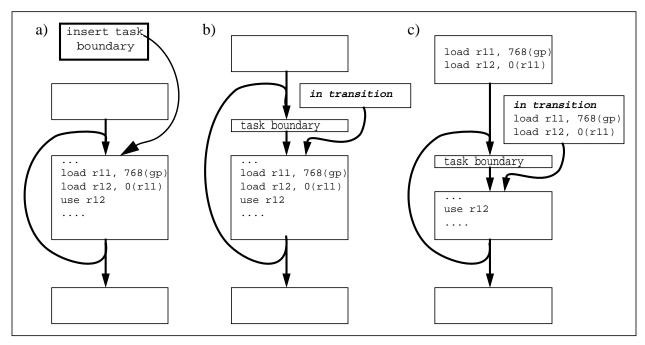

Moving the instruction **F4** to the loop pre-header—block **P** is inserted in the CFG as shown in Figure 2.13—is not without complication. This code motion crosses the incoming edge from the entry block to block **AF**. To compensate for this code motion, a copy of **F4** is added to the end of the entry block to ensure that the value will be computed when transitioning from the original program to the distilled program. There are situations—discussed in Section 3.3.2—that require adding compensation code to the verify block as well.

Block **AF** is then unrolled by a factor of 16 (a degree equal to number of loop iterations per task). Since the induction variables are dead on exit from the loop, only the final branch instruction in the unrolled loop is required, as it subsumes the others. Each of the three induction variable calculations (now each consisting of 16 copies of an add immediate instruction) can be algebraically simplified to a single

Figure 2.13: Distilled version of example code fragment: a) the CFG is further transformed to support a loop header block (H), (b) the instruction contents of each block is shown including the compensation code in the entry block resulting from the motion of instruction F4 to the loop header. Note the constants of instructions F1, F2, and F3 have been scaled by 16.

instruction with the original constant scaled by 16. The fork instruction is further annotated to spawn on every iteration, although each task should still contain 16 iterations of the original program.

The resulting distilled program (shown in Figure 2.13) executes only 6 dynamic instructions per task, where the original program executes over 200 dynamic instructions per task, on average. In the next section, I demonstrate an MSSP execution using this code fragment.

#### 2.2.6 MSSP Execution Example

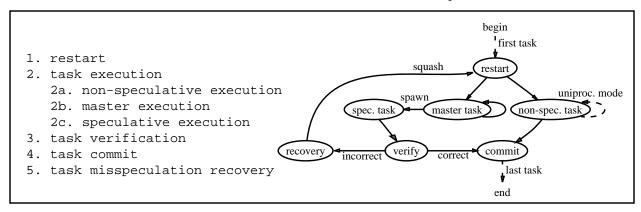

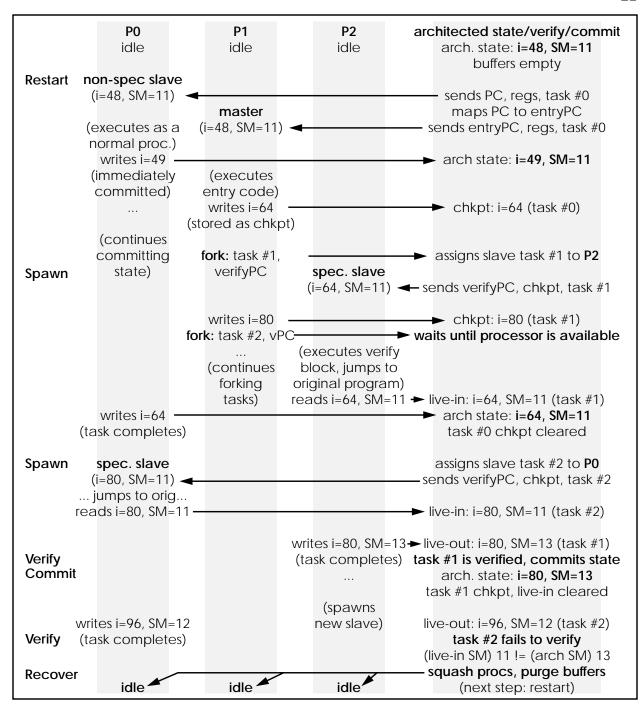

While the MSSP paradigm consists of a small number of straight-forward activities, an execution can be rather complex because many of these activities are occurring concurrently. In Figure 2.14, I list the activities and show the causal relationships between them in a flow chart. The first action performed in an MSSP execution is the restart, which initiates both the master and a non-speculative slave task. The slave

Figure 2.14: Flow chart of MSSP execution.

task can execute non-speculatively (*i.e.*, like a normal uniprocessor) because all of its live-in values are available from architected state and therefore need not be verified. This non-speculative task commits its writes immediately and terminates when it reaches the end of the task.

The master processor, on the other hand, executes task after task in the distilled program (as indicated by the arc from the master to itself in Figure 2.14). In addition, at every task boundary it creates a speculative slave task. There can be many speculative slave tasks concurrently executing, but there will be at most a single non-speculative slave task at any time. If no non-speculative task is running, then the oldest speculative slave task can be verified. If incorrect, a task misspeculation has occurred; recovery is performed by squashing all in-flight tasks and restarting from the most recent architected state. If correct, the task will be committed. The execution ends when the last task is committed.

MSSP can revert to a traditional uniprocessor execution by allowing a non-speculative task to "spawn" the next non-speculative task when it has completed (as shown by the dashed arc from non-spec. task to itself). The slave need not wait until the first task has committed before beginning the next; by simply disabling the task end annotations the slave will execute the program sequentially until they are turned back on.

To more concretely demonstrate the execution, Figure 2.15 shows an illustrative execution of the code fragment distilled in the previous sub-section. The execution begins partway through the loop's execution with the variable i equal to 48 and sometimes\_max equal to 11. For simplicity, I will ignore the other variables. The distilled program is constructed such that the variable i is always correctly computed, but the variable sometimes\_max may be incorrect when the original code executes the inner loop, which has be removed from the distilled program.

The execution commences with the machine quiesced: all processors are idle and all buffers for non-architected data are empty. The restart process initiates two executions of task #0: a non-speculative slave one and a master one. While the non-speculative slave is provided with the architected state, the PC for the master is first mapped (using a lookup table) to find the PC of the corresponding entry into the distilled program. The master executes the entry code before entering the distilled program proper. Both tasks execute simultaneously. The slave task executes like a normal uniprocessor, immediately committing its state. In this example, I assume that the 16 iterations executed by the non-speculative slave all avoid the inner loop, so its only writes are 16 updates to the variable i, of which only the first and last are shown.