# A 3.3-V 18-BIT DIGITAL AUDIO SIGMA-DELTA MODULATOR IN 0.6-μm CMOS

Mohammad Yavari, Mohammad Reza Hasanzadeh, Jafar Talebzadeh, and Omid Shoaei

Electrical & Computer Engineering Department, University of Tehran, Iran P.O. 14395-515, Tehran, Iran

mmyavari@yahoo.com

#### **ABSTRACT**

This paper presents a 3.3-V, 18-bit Sigma-Delta modulator for digital audio, which has been simulated in a 0.6  $\mu m$  double poly, triple metal CMOS process using poly-poly capacitors in all process corners and considering  $\pm$  10 % power supply and -40 °C to 85 °C temperature ranges. The integral gain coefficients of a 2-2 cascaded modulator have been developed for achieving higher overload level factor that is needed for high-resolution noise limited performance modulators. Simulation results give SNDR of 111 dB and 110 dB in typical and worst case, respectively with considering of the circuit noise.

#### 1. INTRODUCTION

Sigma-Delta modulation is a robust means of implementing highresolution analog to digital converters in VLSI technology [1]. By combining oversampling and feedback to shape the noise, and then using a digital low-pass filter to attenuate the noise that has been pushed out-of-band, it is possible to achieve a dynamic range as high as 18-bit. Moreover, oversampling architectures are potentially a power efficient means of implementing highresolution A/D converters. In effect, an increase in sampling rate can be used to reduce the number and complexity of the analog circuits required in comparison with Nyquist rate architectures, transferring much of the signal processing into the digital domain where power consumption can be dramatically reduced simply by scaling the technology and reducing the supply voltage.

Such ADC's like professional audio are usually classified as highend and require 18-bit resolution. Several Sigma-Delta ADC's with 18-bit resolution have been previously reported [2], [3], [4], however all operate with 5-V power supply to take advantage of the larger signal swing. In this paper a new Sigma-Delta modulator architecture that can achieve 18-bit resolution with a single 3.3-V power supply is presented. The circuit requirements for the implementation of proposed architecture has been designed in a 0.6  $\mu m$  5-V double poly triple metal (DPTM) digital CMOS process.

### 2. MODULATOR ARCHITECTURE

Sigma-Delta modulator architectures may be classified as either single loop, which use one A/D and D/A converter along with a series of integrators, or multistage (MASH), which consist of a cascade of single loop Sigma-Delta modulators. Both single loop

and cascade architectures may employ either single bit or multi bit A/D and D/A converters.

A single loop Sigma-Delta modulator with more than two integrators will suffer from unstable oscillations for large level inputs, therefore they can not be chosen for higher overload level modulators. An important advantage of using a multi bit quantizer is that the integrator settling requirements are greatly relaxed since the amplitude of the maximum step change in the integrator input is smaller than with a 1-bit quantizer. Therefore, the integrator seldom slew limits, and the time available for linear settling is maximized. This, in turn, implies a savings in power. Finally, the amplitude of spectral tones is greatly diminished because the total quantization noise is lower, and the quantizer is not continuously in an overload condition. The obvious drawback of multi bit quantization modulators is the need for high linearity in the feedback DAC. Unfortunately, much of the power savings of multi bit quantization are lost owing to the complexity of the techniques that must be used to linearize the output of this DAC.

Cascade architectures use combination of inherently stable first and second order Sigma-Delta modulators to achieve higher order noise shaping. Since stability criteria are relaxed as compared to the higher order loops, the cascade modulators approach the dynamic range more than higher order single loop implementations at the cost of a higher sensitivity to the non-idealities of the building blocks [5].

In the design of high-resolution Sigma-Delta modulators the major concern that limits the accuracy is the analog noise (thermal and flicker noise). Analog noise determines power dissipation and analog circuit size. Flicker noise can be reduced by circuit techniques such as double correlated sampling. Thermal noise is generated from the non-zero on resistance of the switches and the thermal noise of the op-amp. For fully differential modulators, the *SNR* due to *KT/C* noise of the switches can be written as:

$$SNR_{KT/C} = \frac{(2 \times OL \times V_{ref})^2}{2} \frac{C_s \times OSR}{4 KT}$$

(1)

Where  $C_s$ ,  $V_{ref}$  OSR and OL, are the sampling capacitance, reference voltage, oversampling ratio and overload level factor, respectively. The maximum swing of the integrators (op-amps) determines the reference voltage; therefore for a low power design the overload level factor should be increased where it is possible.

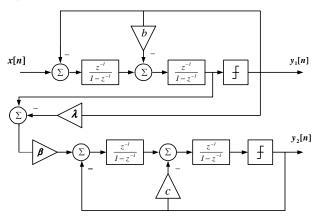

In this paper a 2-2 cascaded Sigma-Delta modulator with *OSR* of 128 has been designed. Fig. 1 shows the 2-2 cascaded Sigma-Delta modulator architecture.

In this section computer simulations that model the non-linearity of the quantizer are used to select the system gains, b, c,  $\beta$  and  $\lambda$  as shown in Fig. 1 for the 2-2 cascaded modulator. The value of these gains is chosen with the objective of maximizing the dynamic range of the modulator under the assumption that the circuit noise floor is -114 dB with considering the sampling capacitance of the first integrator of 10-pF and  $V_{\rm ref}$  of 1.35-V. This amounts to maximizing the modulator overload level without increasing the quantization noise floor above the circuit noise. Another consideration in choosing the system gains is to ensure that the base band quantization noise is independent of the input signal, thereby avoiding the presence of spurious tones and signal dependence in the noise floor.

Fig. 1: Block diagram of 2-2 cascaded Sigma-Delta modulator.

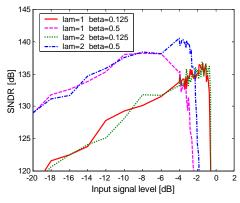

Choosing b and c of 2.5 is a reduction in spectral tones in the output of a second-order modulator, that was noted in [6]. Fig. 2 shows the effect of different values of  $\beta$  and  $\lambda$  on the overload level. The highest overload level is the -0.6 dBFS (i.e. the maximum relative input amplitude in which the SNR degrades no more than 6 dB from the maximum SNR [5]) for  $\beta$ =0.125 and  $\lambda$ =2. It should be noted in [2] and [3] a 2-2 cascaded modulator with local feedback has been designed for higher overload level, however in this case SNDR is very sensitive to matching of analog and digital parameters.

**Fig. 2:** Dynamic range for different values of  $\beta$  and  $\lambda$ .

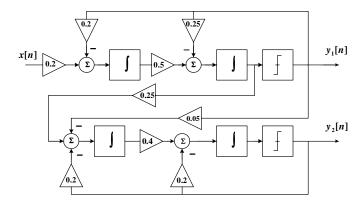

An important consideration in the design of a Sigma-Delta modulator is the size of the integrators output swing as the modulator input approaches full scale. Fig. 3 shows the integrator gains, which has been scaled. The objective of signal scaling is to allow a large modulator input signal range to maximize the *SNR* due to *KT/C* noise.

Fig. 3: A 2-2 cascaded Sigma-Delta modulator with integrator gains.

### 3. MODULATOR DESIGN

The main circuit non-idealities that degrade the *SNDR* of the modulator include: switches thermal noise, op-amp noise, finite DC gain of the integrators, finite bandwidth and slew rate of the op-amps. With modeling each of the non-idealities, the proposed 2-2 cascaded modulator has been simulated at behavioral level simulation [7]. Table 1 shows the effect of these non-idealities on the *SNDR* individually. The resultant *SNDR* is 112 dB including all of the non-idealities shown in Table 1.

| Integrator Non-ideality                     | SNDR [dB] |

|---------------------------------------------|-----------|

| Ideal modulator                             | 136       |

| Switches thermal noise                      | 114       |

| Sampling capacitance (C <sub>s</sub> =10pF) |           |

| Input referred op-amp noise                 | 118       |

| $V_n=3\mu V_{rms}$                          |           |

| Finite DC gain of first integrator          | 124       |

| A <sub>0</sub> =80 dB                       |           |

| Finite unity gain bandwidth                 | 128       |

| UGBW=65 MHz                                 |           |

| Slew rate (SR=120 V/µs)                     | 126       |

Table 1: Circuit level requirements.

Switched-capacitor integrators are the key circuit building block in a Sigma-Delta modulator. The design goal is to choose a low-power operational amplifier topology that can meet the

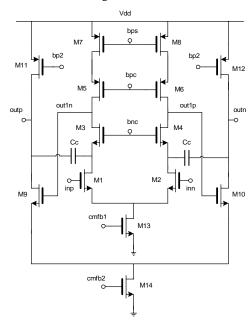

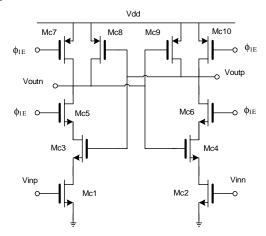

requirements of the 2-2 cascade modulator and to optimize device sizes and bias points to minimize power dissipation. For negligible quantization noise leak due to finite amplifier DC gain, the first two amplifiers require gain of 80 dB or greater. Since this gain is on the order of  $(g_m r_o)^3$ , a two stage amplifier must be employed. From a power dissipation perspective, the following amplifier characteristics are needed: 1) maximum output swing, which suggests a common source second stage, 2) all NMOS signal path for fast settling with large capacitors, 3) minimum number of current legs, 4) minimum number of devices that contribute significant thermal noise, 5) a maximum bandwidth compensation loop and 6) fully-differential 2<sup>nd</sup>-stage for better common mode rejection ratio (CMRR) and power supply rejection ratio (PSRR). The amplifier in Fig. 4 achieves the desirable lowpower characteristics. The first stage is a telescopic amplifier, and this is followed by differential pair in the second stage. The telescopic topology has a number of advantages over its foldedcascode counterpart. It has fewer noise-contributing devices, fewer current legs and a wider bandwidth for a given current level.

The amplifier has an all NMOS signal path. NMOS devices are approximately three times faster than PMOS devices because of the difference between the electron and hole mobilities. Since speed and power directly trade off, a higher speed amplifier will dissipate less power for a fixed settling constraint. The disadvantage with NMOS input devices is the higher flicker noise. In this design, large size input devices has been used for having a reasonable flicker noise. The second stage is made fully differential instead of a quasi-differential common-source stage for a number of reasons. Having a tail current device eliminates the need for a power-hungry inversion stage for the commonmode feedback amplifier. This allows the use of dynamic switched-capacitor common-mode feedback circuits, which does not dissipate any static power. The fully differential second-stage amplifier also eliminates the need for a dynamic level shift between the output of the first stage and the input of the second stage [8]. In addition this fully differential topology improves the PSRR and CMRR.

Some form of compensation is needed to maintain stability in a 2-stage amplifier. The standard Miller compensation has a pole-splitting effect, which moves one pole to a lower frequency and another to a higher frequency. The 2-stage amplifier in Fig. 4 employs the cascode compensation scheme [9], which creates a dominant pole and two complex poles at a higher frequency. It has been shown the cascode compensation scheme yields a higher amplifier bandwidth compared to the conventional Miller compensation. The simulated op-amp unity gain bandwidth is 100 MHz with a phase margin of 74° and the DC gain is 95 dB.

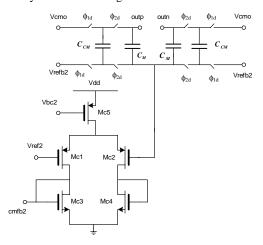

Common-mode feedback (CMFB) is required in fully differential amplifiers to define the voltages at the high-impedance output nodes. The amplifier employs dynamic or switched capacitor common-mode feedback. The fully differential second stage eliminates the need for an inversion in the common-mode feedback loop. Fig. 5 shows the common-mode feedback loop for the second stage of the amplifier. Capacitors  $C_M$  are used to sense the output common-mode voltage. During  $\phi_{2d}$ , switched capacitors  $C_{CM}$  define the appropriate DC voltage on the sense capacitors. For having sufficient gain in the common-mode feedback circuit a diff pair has been added in Fig. 5. References  $V_{\text{ref2}}$  and  $V_{\text{refb2}}$ , which are at the same nominal voltage, are separated to maintain a stable bias on the gate of  $M_{C1}$  while the capacitors  $C_{CM}$  are

switched onto  $V_{\rm refb2}$ . Minimum size devices are used for the CMOS switches in the common-mode feedback circuit. Simulation results show that the CMFB loop has a phase margin of 72°. A similar common-mode feedback is designed for the first stage of the amplifier. The nominal output common-mode voltage,  $V_{\rm CMO}$ , is 1.7-V for this design.

Fig. 4: Fully differential 2-stage OTA.

Fig. 5: Common-mode feedback.

The second major component of the modulator is the comparator. The performance of the modulator is relatively insensitive to comparator offset and hystersis, since the effects of these impairments in the first and second comparators are attenuated by the second-order and fourth-order noise shaping, respectively. A simple dynamic comparator as shown in Fig. 6 is used to perform a single-bit conversion. During phase 2, when the latch signal is low, the differential outputs are reset to  $V_{DD}$ . As the latch signal turns high, the differential inputs control the resistance of the triode devices,  $M_{C1}$  and  $M_{C2}$ . Based on this differential resistance, the outputs of the cross-coupled inverters ( $M_{C3}$ ,  $M_{C4}$ ,  $M_{C7}$  and

$M_{C8}$ ) flip in the appropriate direction. The outputs of the dynamic latch are stored in an SR latch that is implemented with CMOS NAND gates. Inverters buffer the outputs of the SR latches used in the comparators that drive NMOS switches connected to the negative reference voltage and PMOS switches connected to the positive reference voltage.

The integrators need a 2-phase non-overlapping clock (with delays) to minimize signal-dependent charge injection errors. The sampling operation at the input of the third integrator causes a brief disturbance at the output of the second integrator. If the regenerative latch in the first stage quantizer enters the regeneration phase before the output of the second integrator has recovered, an erroneous result may be produced. To avoid this problem, an early phase of  $\phi_1$ , labeled  $\phi_{1E}$ , is used to strobe the first-stage comparator. The timing of the phases and the speed of the latch are such that the subsequent sampling by the third integrator does not cause the latch to error.

Fig. 6: Regenerative comparator.

# 4. SIMULATION RESULTS

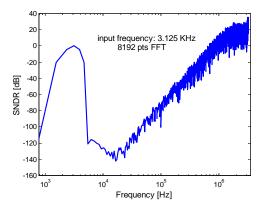

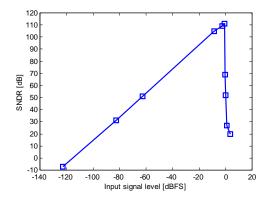

The 2-2 cascaded Sigma-Delta modulator as shown in Fig. 3 has been simulated in a 0.6 μm double-poly triple metal (DPTM) CMOS process with poly-poly capacitors. The threshold voltages of this process are 0.85-V and –0.8-V for NMOS and PMOS transistors, respectively. The modulator samples at 6.4 MHz with 50 KHz Nyquist rate. All of the simulations have been performed with considering 20% bottom plate parasitic capacitance with HSPICE. Plots of *SNDR* and *DR* are shown in Figs. 7 and 8, respectively. The resultant *SNDR* and *DR* are 111 dB, 114 dB in the typical and 110 dB, 112 dB in the worst-case process corners, respectively.

## 5. CONCLUSION

In this paper a new 2-2 cascaded Sigma-Delta modulator with a maximized overload level factor was proposed, which is less sensitive to matching of digital and analog coefficients. It has overload level factor about -0.6 dBFS. The modulator has been designed in a 0.6- $\mu$ m DPTM 5-V digital CMOS process with a single 3.3-V power supply. The resultant *SNDR* and *DR* are 111 dB and 114 dB, respectively. The modulator total power consumption is 65 mW.

Fig. 7: Power spectral density.

Fig. 8: Dynamic range.

## REFERENCES

- S. R. Northworthy, R. Schreier, and G. C. Temes, "Delta-Sigma Data Converters," Piscataway, NJ: IEEE Press, 1997, ISBN 0-7803-1045-4.

- [2] I. Fujimori, "A Single-Chip Stereo Audio Delta-Sigma A/D Converter with 117 dB Dynamic Range," IEICE Trans. Fundamentals, Vol. E83-A, No. 2, Feb. 2000.

- [3] I. Fujimori et al., "A 5-V Single-Chip Delta-Sigma Audio A/D Converter with 111 dB Dynamic Range," IEEE J. Solid-State Circuits, Vol. 32, March, 1997.

- [4] K. Y. Leung et al., "A 5V, 118dB  $\Delta\Sigma$  Analog-to-Digital Converter for Wideband Digital Audio," ISSCC, 1997.

- [5] A. Marques et al., "Optimal Parameters for  $\Delta\Sigma$  Modulator Topologies," IEEE Trans. on circuits and systems-II, Sep. 1998.

- [6] L. A. Williams, and B. A. Wooley, "A Third-Order Sigma-Delta Modulator with Extended Dynamic Range," IEEE J. Solid-State Circuits, Vol. 29, March 1994.

- [7] S. Brigati et al, "Modeling Sigma-Delta Modulator Non-idealities in SIMULINK," ISCAS, 1999.

- [8] A. R. Feldman, B. E. Boser, P. R. Gray, "A 13-Bit, 1.4-MS/s Sigma-Delta Modulator for RF Baseband Channel Applications," IEEE J. Solid-State Circuits, Vol. 33, Oct. 1998

- [9] B. Ahuja, "An improved frequency compensation technique for CMOS operational amplifiers," IEEE J. Solid-State Circuits, Vol. 18, Dec. 1983.