M. Venkata Ramanaiah, Sudhakar Alluri, B.Rajendra Naik, N.S.S.Reddy

Abstract— In Very-huge scale reconciliation (VLSI) application zone, postponement and power are the significant variables for any advanced circuits. Its observed that the as CMOS Inverter Transistor Size decreases from 1µm to 120nm, power reduced from 3.331 to 2.644 (µW) and delay reduced from 5.026 to 22.66 (pS). It is observed that the table 4 as 28T Full Adder Circuit Voltage Scale decreases from 5 V to 1 V, Total power reduced from 63150 to 2262 (nW) and delay reduced from 39.93 to 38.52 (nS) in 180nm technology. It is observed that the table 6 as 28T Full Adder Circuit Voltage Scale decreases from 2 V to 0.8 V, Total power reduced from 21.39 to 2.916 (µW) and delay reduced from 4.939 to 4.74 (nS) in 90nm technology. It is observed that the table 8 as 28T Full Adder Circuit Voltage Scale decreases from 1.5 V to 0.7 V, Total power reduced from 8.98 to 1.713 (µW) and delay reduced from 4.963 to 4.581 (nS) in 45nm technology.

Key words— CMOS Inverter, 28T Full viper, low power, low territory, delay, VLSI.

#### I. INTRODUCTION

The optimization of power consumed in digital blocks of an Coordinated Circuit while protecting the usefulness is performed by Electronic Design Automation (EDA) devices. There is a critical increment in the power utilization of Very Large Scale Integration (VLSI) chips because of the expanding pace and multifaceted nature of the present structures. Reduction of power is a great challenge. Hence, new techniques are designed by the researchers to reduce power dissipation. With today's world of advancement in the IC technology there are more than 100 million transistors, timed at more than 1 GHz which means manual power improvement would be extremely moderate and an incredible assurance of blunders, henceforth Cadence instruments are essential.

Inherent low power utilization of Complementary Metal Oxide Semiconductor (CMOS) innovation is one of the key highlights that prompted the immense achievement of this innovation. Due to this the circuit designers could concentrate on maximizing the circuit performance along with the reduction in the circuit area. CMOS technology has very good scaling properties due to this there is a decrease in the size of the IC's which take into account increasingly

Revised Manuscript Received on September 10, 2019.

M. Venkata Ramanaiah, Department of ECE, CMRIT, JNTUH, Hyderabad, Telangana, India

(Email: ramanaiah.m@gmail.com)

Sudhakar Alluri, Department of ECE, CMRIT, JNTUH, Hyderabad, Telangana, India.

(Email: sudhakaralluri709@gmail.com)

**B.Rajendra Naik**, Department of ECE, UCE, Osmania University, Hyderabad, Telangana, India.

(Email: rajendranaikb@gmail.com)

N.S.S.Reddy, Department of ECE, VCE, Osmania University, Hyderabad, Telangana, India.

(Email: nssreddy69@gmail.com)

more intricate framework plans on a solitary chip while working at high clock frequencies. The concern over the power consumption came into picture during 1980's when the first portable electronic systems were developed. The definitive factor for the achievement of the item financially comes when the battery lifetime is generally excellent. Increase in the active elements on the Integrated Circuit area lead to huge consumption of energy. Maintaining the power levels creates the problems of heat dissipation. Expensive heat removal systems such as heat sinks are required to keep the devices in active states. These elements contributed control as one of the real plan parameter alongside execution and the IC size. The constraining element in the nonstop scaling of CMOS innovation is power, in order to optimize power more research work was carried out in developing automated tools like Cadence Tool. The tool is better in handling issues like optimization at Circuit and Logic level. Today there is an overall impact because of the advancements in research for Cadence tools targets system or architectural level optimization. Efficient techniques together with optimization tools to calculate or estimation of the power utilized in a digital circuit are very important.

The framework particulars are processor Intel (R) center (TM) i5-4570 CPU@3.20GHz.,3.20GHz.Installed memory (RAM) 4 GB (usable memory is 3.43GB) and framework type: 32-bit working framework (OS).

This paper is framed as pursues Section II shows the writing survey on CMOS Inverter and 28Tfull snake Section III introduces the procedure for CMOS Inverter and 28Tfull viper and likewise examined the low power investigation, High speed and low region. Segment IV demonstrates the reproduction results and they are talked about plainly, at last the paper is closed with Section V.

#### II. LITERATURE REVIEW

within the gift brief correspondence global the utilization of gadgets bendy gadgets is growing grade by grade, due to the fact the devices are nice and littler it wishes to fulfill the need of low strength dispersing and least sector important close by the fast. A one piece full snake mobile is one of the maximum as frequently as potential used mechanized circuit detail in math rationale unit (ALU) and it's far the crucial utilitarian unit of all computational circuit. till now diverse development has been achieved round there to refine the designing and execution of complete snake circuit form [1]-[2]-[3]-[4]. Extension is one some of the easy math sports. it is used normally in a couple VLSI systems, for instance,

software program-express DSP systems and microchips. regardless of its crucial enterprise, that's such as blended numbers, it is the center of numerous one-of-a-kind supportive assignments, as an instance, subtraction, increment, department, address estimation, and so on. In most of these systems the snake is a fraction of the large manner that chooses the overall execution of the device[5].

that is the purpose improving the advent of the 1-piece whole-snake cell (the shape rectangular of the mixed snake) is a simple aim. New shape low-manipulate VLSI structures has ascended as amazingly in call for as an development of the rapidly growing trends in bendy correspondence and computation[7]. The battery development would not improve at a comparative charge due to the fact the microelectronics improvement. there is a restrained percent of energy available for the flexible systems. So fashioners square measure featured with more objectives: speedy, excessive return, little issue area, and on the same time, lowmanage utilization. So building low-control, critical snake cells is of fantastic interest[8]-[9], on this paper, a looked after out approach for looking at the snake setup is displayed. it's miles predicated upon keeping apart the whole snake into humbler modules. All of these modules is completed, streamlined, and tried freely. more than one complete-snake cells are made with the useful resource of interfacing these modules. The remainder of the paper is dealt with as follows[10].

#### III. DESIGN METHODOLOGY

1. Transistor Sizing of CMOS Inverter

CMOS inverters are probably the most to a great extent utilized and versatile MOSFET inverters in chip structuring.

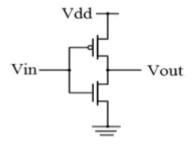

Figure 1:CMOS Inverter black diagram

They paintings with immaterial affect mishap and at tolerably quick. similarly, the CMOS inverter has exquisite approach of reasoning assist traits in that. Its clatter edges are colossal in every low and excessive states. A CMOS electrical converter confirmed up in figure one consists of a PMOS associate degreed a NMOS gadgets associated at the channel and entryway terminals, a stock voltage VDD at the PMOS supply terminal, and a ground associated at the NMOS supply terminal, had been input is related to the door terminals and Output is associated with the channel terminals. because the commitment to the converter varies among association 0 and association one, the nation of the NMOS and PMOS actions in like way to make yield as basis 1 and method of reasoning 0 independently.

With each time of VLSI improvement scaling, the scientists are improving the introduction of pc systems. lamentably, they devour up pretty a few strain; in all reality their potential densities and going with warmth age are all at once advancing in the path of degrees that are proportionate to nuclear reactors . those floor-breaking densities lessen chip reliability and future, increase cooling charges or even motive ordinary issues for huge server ranches. on the contrary completion of the advent enlarge, control issues gift problems for smaller mobile phones with confined battery limits. In the ones gadgets, the use of more reminiscences and quicker processors in addition decline the battery life. From this time beforehand, redesigns in chip development will land at a halt, at a few element aspect monetarily smart responses for power troubles are not given. power the board is a multidisciplinary area that carries diverse factors like imperativeness, temperature and fidelity, all of it really is fantastic.

This paper offers a survey of changed manipulate decline techniques that domain unit accustomed cut back the whole electricity eaten up by the usage of a microchip machine at circuit level. consequently, care must be taken as soon as a static method of reasoning style is picked to esteem a justification art work. full adders are used as a base circuit in contrasted extensive range shuffling circuits to preserve out calculating errands like extension, subtraction, increase, address calculation and MAC unit, and so forth. Beside calculating sporting activities, adders are applied to make reminiscence territories in distinct fashions of microchips and preserve reminiscences. Thusly development inside the full snake ought to display dynamically treasured for all of the circuits wherein its application has a simple effect within the introduction of the circuit where it's been used. The most essential parameters to be stored in idea are minimization power which impacts the presentation accommodation of any VLSI circuit.

#### 2. 28T Conventional Full Adder Circuit

The 1-piece complete snake mobile has 28 transistors. For complicated entryways with large fan-ins the CMOS affiliation style isn't region gainful technique. eventually, care ought to be taken as soon as a static justification trend is picked to esteem a technique of reasoning paintings. The pseudo NMOS framework is simple. The pass crossing element transistor approach of reasoning fashion is general to be a nicely-favored approach for finishing some unique circuits, as an example, multiplexers and XOR based circuits, like adders. An antique fashion of commonplace static CMOS whole snake is predicated upon regular CMOS form with considerable draw up and pull-down transistor giving entire - swing yield and superb the use of capacities.

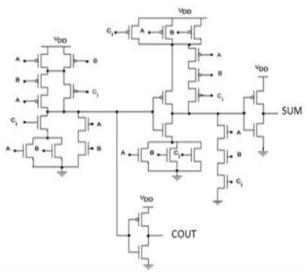

Figure 2: 28T Full Adder Circuit.

The full viper comprises of three sources of info A, B, and Cin one piece every it computes the two yields Sum and convey them two are one piece every this is the activity of the full snake.

$$SUM = A \oplus B \oplus C$$

.....(1)

$COUT = AB + BC + AC$ ....(2)

#### 3. Low Power analysis

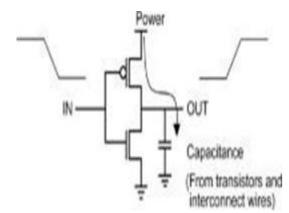

Discern 3: Dynamic power.

Dynamic power is the electricity devoured when the fabric is in dynamic mode. At some thing point the device is in dynamic mode the strength disseminated inside the gadget is known as as Static power, but the signal traits are unaltered.

$$P_{Dynamic} = 0.5*\alpha *_{C} *_{V} *_{2}*_{f}$$

$$U_{Dynamic} = 0.5*\alpha *_{C} *_{U} *_{A} *_{C} *_{C}$$

# IV. SYNTHESIS AND SIMULATION RESULTS

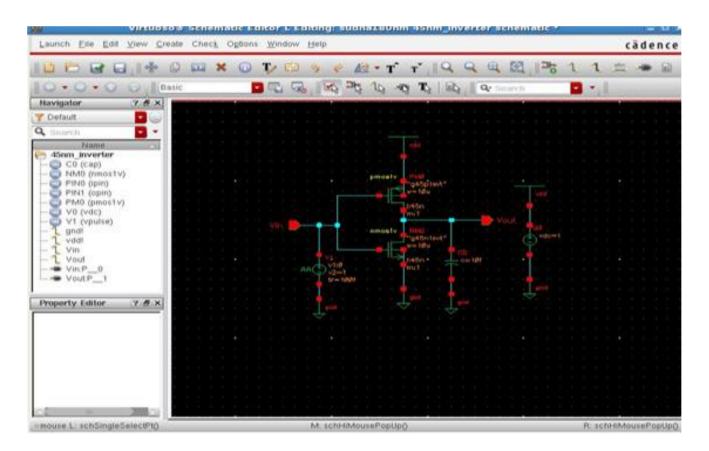

# discern four: CMOS Inverter schematic graph in 45nm era at 1Volts.

it's far seemed in figure 4, The PMOS and NMOS transistors schematic diagram encompass width is 120nm Load capacitance is10fF at stockpile voltage 1V, beat width 2nsec and duration 1nsec. each upward thrust time and fall time (100f) sec the usage of mood 45nm improvement.5

**Table 1: Specification of inverter**

| Specification       | PMOS          | NMOS | PMOS | NMOS | PMOS         | NMOS |

|---------------------|---------------|------|------|------|--------------|------|

| Total width         | 120 nm        |      | 1µm  |      | 10μ <b>m</b> |      |

| Library<br>name     | gpdk 45       |      |      |      |              |      |

| Length              | 45 nm         |      |      |      |              |      |

| Rise/fall<br>time   | 100f s/100f s |      |      |      |              |      |

| Load<br>Capacitance | 10fF          |      |      |      |              |      |

| Temperature         | 27º c         |      |      |      |              |      |

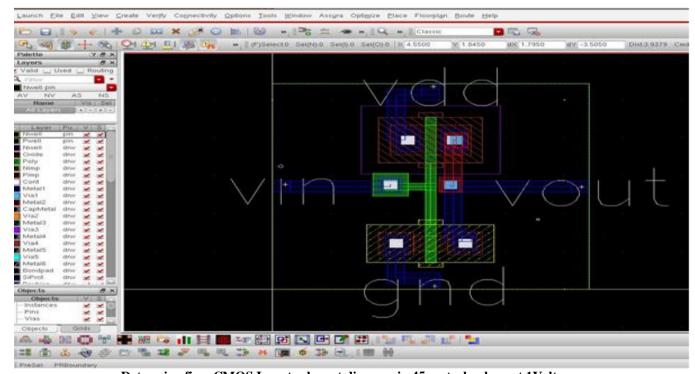

Determine five: CMOS Inverter layout diagram in 45nm technology at 1Volts

It's miles tested in determine 5 CMOS Inverter format outline is combination of PMOS and NMOS transistors incorporate of width is 120nm ,green shading is poly silicon and blue shading is Metal1,wherein Vdd , Vin, Vout and

floor are associated with Metal1, CMOS Inverter layout chart in 45nm era at 1Volts to carry out Inverter.

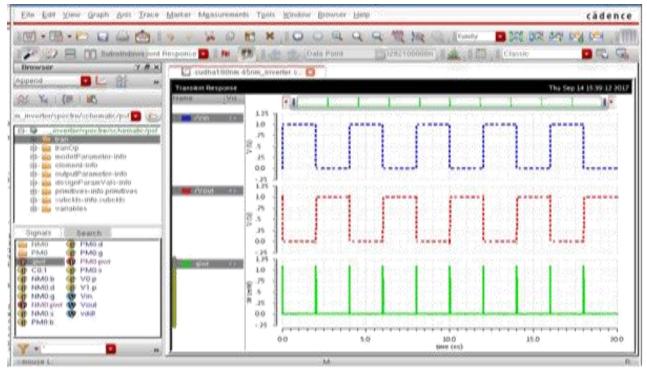

Parent 6: CMOS Inverter Output Waveform at 45nm technology at the frequency 50MHz.

It is shown in discern 6 CMOS Inverter Output Waveform blue shade is enter sign, pink coloration is output signal and inexperienced shade is commonplace electricity signal, on the frequency of 50MHz in 45nm generation.

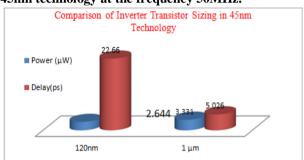

Desk 2: evaluation of CMOS Inverter in 45nm era

| Transistor Width | 120nm | 1 µm  |

|------------------|-------|-------|

| Power (µW)       | 2.644 | 3.331 |

| Delay(ps)        | 22.66 | 5.026 |

It is observed from the above table 2 at different transistor width 120nm, 1  $\mu m$  and 10  $\mu m$  it shows that at 120nm transistor size performed reduced power and delay.

Figure 7: Comparison of Inverter Transistor Size in 45nm Technology

From discern 7 its located that the as CMOS Inverter Transistor length decreases from  $1\mu m$  to 120nm strength decreased from three.331 to  $2.644~(\mu W)$  and delay decreased from 5.026 to 22.66~(ps).

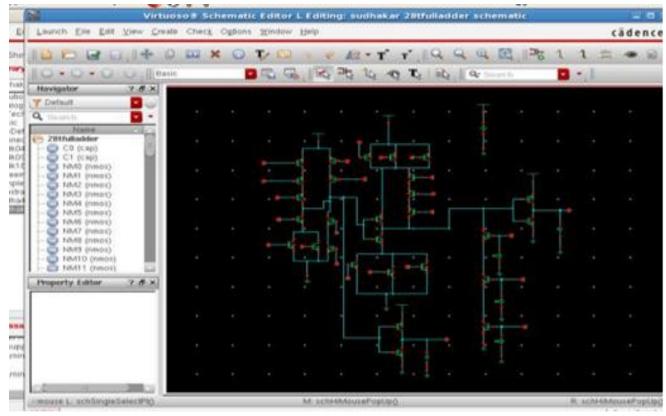

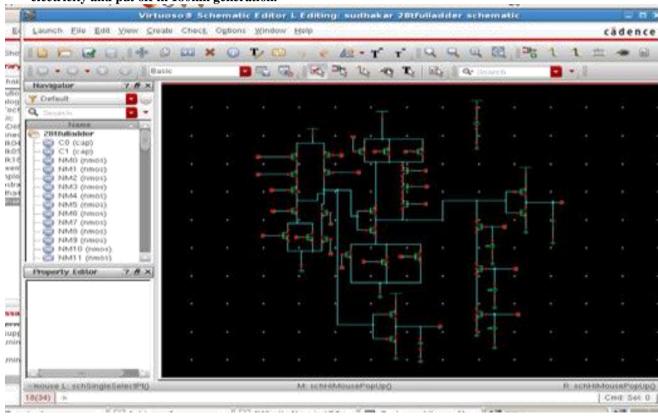

parent eight: 28T complete Adder schematic diagram in 180nm era.

it's miles observed from the discern 8, The PMOS and NMOS transistors schematic graph incorporate of width are 800nm and 400nm, Load capacitance is 10fF, at supply voltage from [1-5] V. both upward thrust time and fall time

(100f) sec and the undertaking of the proposed 28T complete Adder schematic chart changed into executed using 180nm innovation.

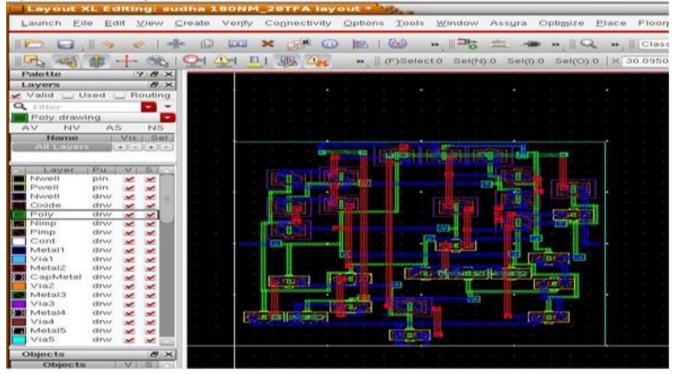

figure 9: 28T full Adder layout diagram in 180nm generation

it's miles seen from the discern nine 28T full Adder layout outline is mixture of PMOS and NMOS transistors contain of width are 800nm and 400nm ,inexperienced shading is poly silicon and blue shading is Metal1, where A, B, Cin, Sum, Cout, Vdd and floor are associated with Metal1, 28T complete Adder format chart at 1.eight Volts in 180nm generation.8

Table 3: Specification of 28T Full Adder in 180nm technology.

| Specification    | NMOS (nm)   | PMOS (nm) |

|------------------|-------------|-----------|

| Library name     | Gpdk180     | Gpdk180   |

| Length           | 180         | 180       |

| Total width      | 400         | 800       |

| Finger width     | 400         | 800       |

| Rise/fall time   | 100fs/100fs |           |

| Load Capacitance | 10fF        |           |

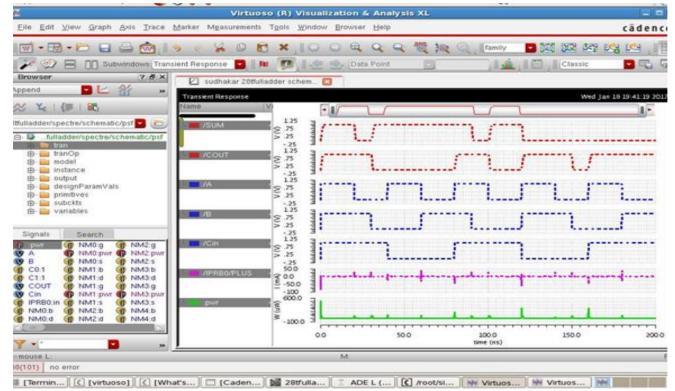

discern 10: 28T complete Adder Output Waveform on the frequency 50MHz and 1Volts in 180nm generation.

found from shown in determine 10 28T full Adder of Output Waveform, at the frequency 50MHz 1Volts in 180nm technology.

Table 4: Comparison of Power Dissipation and Delay 28T Full Adder Circuit in 180nm Technology

| Voltage(V) | Delay | Dynamic Power (nW)  |

|------------|-------|---------------------|

| voltage(v) | (nS)  | Dynamic Tower (IIW) |

| 1          | 38.52 | 2262                |

| 1.8        | 39.64 | 7569                |

| 2          | 39.75 | 9384                |

| 3          | 39.87 | 21440               |

| 4          | 39.9  | 38670               |

| 5          | 39.93 | 63150               |

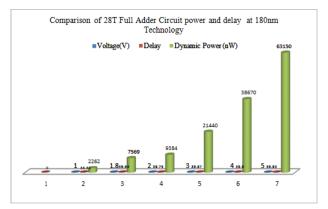

it's far observed that the desk four as 28T complete Adder Circuit Voltage Scale decreases from five V to at least one V, overall electricity reduced from 63150 to 2262 (nW) and delay decreased from 39.ninety three to 38.fifty two (nS) in 180nm technology.

Published By:

it's miles located that the determine 11 as 28T full Adder Circuit Voltage Scale decreases from 5 V to 1 V, total energy reduced from 63150 to 2262 (nW) and put off reduced from 39.93 to 38.52 (nS) in 180nm era.

parent 11: evaluation of 28T complete Adder Circuit electricity and put off in 180nm generation.

determine 12: 28T Schematic diagram of 28T complete Adder in 90nm generation

it is seen from the determine 12, The PMOS and NMOS transistors schematic define include of width are 240nm and 120nm, Load capacitance is 10fF, at supply voltage from [0.8-2] V. both upward thrust time and fall time (100f)sec and the reenactment of the proposed 28T complete Adder schematic graph turned into done making use of 90nm innovation.

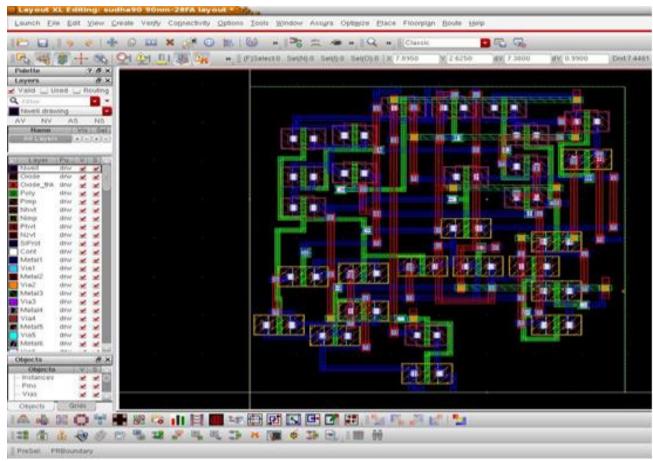

figure 13: format diagram of 28T complete Adder in 90nm era

it's far visible that the parent thirteen 28T complete Adder format graph is blend of PMOS and NMOS transistors comprise of width are 240nm and 120nm ,green shading is poly silicon and blue shading is Metal1,in which A, B, Cin, Sum, Cout, Vdd and ground are associated with Metal1, 28T complete Adder format define at 1 Volts in 90nm generation.11

Table 5: Specification of 28T Full Adder in 90nm technology

| Specification    | NMOS (nm)     | PMOS (nm) |

|------------------|---------------|-----------|

| Library name     | gpdk 90       | gpdk 90   |

| Length           | 90            | 90        |

| Total width      | 120           | 240       |

| Finger width     | 120           | 240       |

| Rise/fall time   | 100f s/100f s |           |

| Load Capacitance | 10fF          |           |

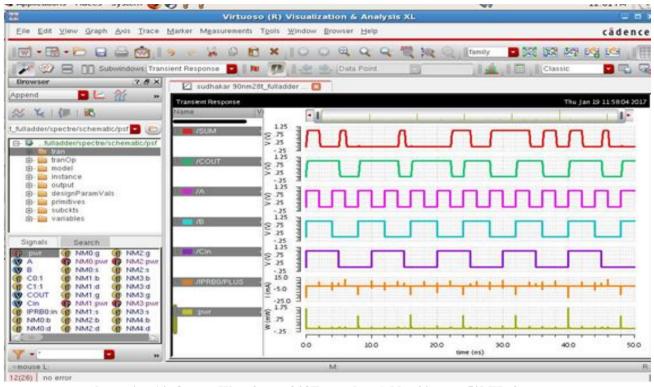

determine 14: Output Waveform of 28T complete Adder 90nm at 50MHz frequency

it is visible from the parent 14, The PMOS and NMOS transistors reproduction aftereffect of yield waveform include of width are 240nm and 120nm, Load capacitance is 10fF, at deliver voltage 1 V. each upward thrust time and fall time (100f) in 90nm innovation.12

Table 6: 28T Full Adder Circuit in 90nm Technology

| Voltage(V) | Delay(nS) | Dynamic Power(μW) |

|------------|-----------|-------------------|

| 0.8        | 4.74      | 2.916             |

| 0.9        | 4.771     | 3.731             |

| 1          | 4.789     | 4.651             |

| 1.5        | 4.91      | 11.01             |

| 2          | 4.939     | 21.39             |

It is observed that the table 6 as 28T Full Adder Circuit Voltage Scale decreases from 2 V to 0.8 V, Total power reduced from 21.39 to 2.916 ( $\mu$ W) and delay reduced from 4.939 to 4.74 (nS) in 90nm technology.

determine 15 : contrast of energy vs put off at 90nm era.

it's miles determined that the determine 15, comparison of energy vs postpone in 90nm generation Voltage Scale decreases from 2 V to 0.8 V, general power reduced from 21.39 to 2.916 ( $\mu$ W) and put off decreased from four.939 to four.seventy four (nS) in 90nm era.

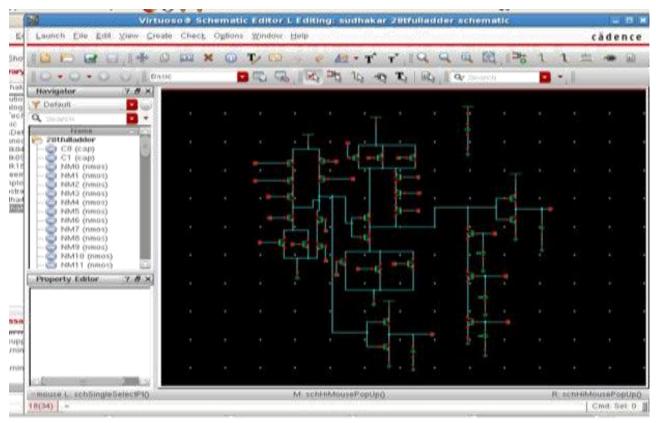

parent sixteen: Schematic diagram of 28T full Adder in 45nm era

'it's miles visible from the determine sixteen, The PMOS and NMOS transistors schematic graph contain of width are 240nm and 120nm, Load capacitance is 10fF, at deliver voltage from [0.7-1.5] V. both upward push time and fall

time (100f)sec and the exercise of the proposed 28T full Adder schematic graph changed into completed using 45nm innovation..

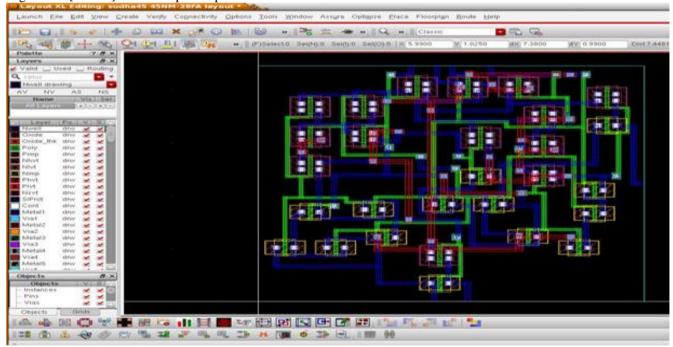

parent 17: layout diagram of 28T complete Adder in 45nm era

it's miles visible from the determine 17 28T full Adder format chart is blend of PMOS and NMOS transistors incorporate of width are 240nm and 120nm ,inexperienced shading is poly silicon and blue shading is Metal1,where A, B, Cin, Sum, Cout, Vdd and ground are associated with Metal1, 28T full Adder format outline at 1 Volts in 45nm generation.14

Table 7: Specification of 28T Full Adder in 45nm technology

| Specification    | NMOS          | PMOS    |

|------------------|---------------|---------|

| Library name     | Gpdk 45       | Gpdk 45 |

| Length           | 45 nm         | 45 nm   |

| Total width      | 120 nm        | 240 nm  |

| Finger width     | 120nm         | 240 nm  |

| Rise/fall time   | 100f s/100f s |         |

| Load Capacitance | 10fF          |         |

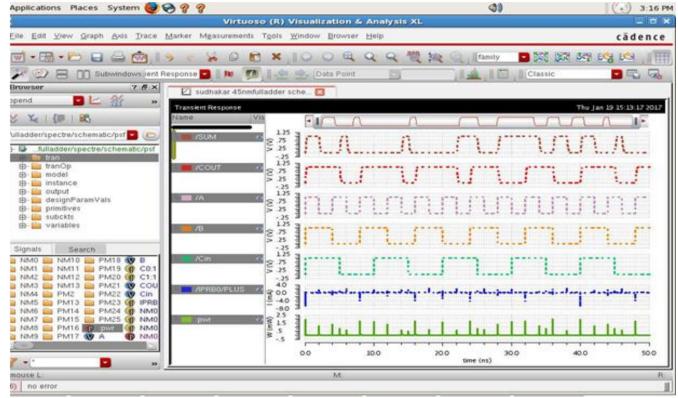

determine 18: Output Waveform of 28T full Adder in 45nm technology at 50MHz frequency & 1V

it is visible from the discern 18, The PMOS and NMOS transistors reenactment aftereffect of yield waveform comprise of width are 240nm and 120nm, Load capacitance is 10fF, at deliver voltage 1 V. each upward thrust time and fall time (100f) in 45nm innovation.

Table 8: Comparison of power and delay for 28T Full Adder Circuit in 45nm Technology

| Voltage(V) | Delay<br>(nS) | Dynamic<br>power(μW) |

|------------|---------------|----------------------|

| 0.7        | 4.581         | 1.713                |

| 0.8        | 4.799         | 2.298                |

| 0.9        | 4.876         | 2.967                |

| 1          | 4.912         | 3.727                |

| 1.2        | 4.945         | 5.597                |

| 1.5        | 4.963         | 8.98                 |

it is observed that the desk 8 as 28T full Adder Circuit Voltage Scale decreases from 1.five V to 0.7 V, general strength decreased from eight.98 to at least one.713 ( $\mu$ W) and postpone reduced from four.963 to 4.581 (nS) in 45nm era.

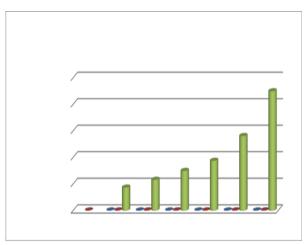

figure 19: 28T full adder strength dissipation vs delay

it's miles observed that the parent 19 as 28T complete Adder Circuit Voltage Scale decreases from 1.5 V to zero.7 V, total power decreased from 8.98 to at least one.713 ( $\mu$ W) and delay decreased from four.963 to four.581 (nS) in 45nm generation.

#### V. CONCLUSION

Its saw that the as CMOS Inverter Transistor length abatements from 1µm to 120nm, manipulate reduced from three.331 to two.644 (µW) and defer diminished from 5.026 to 22.sixty six (playstation). it's far seen that the table four as 28T complete Adder Circuit Voltage Scale diminishes from 5V to 1V, overall power decreased from 63150 to 2262 (nW) and defer reduced from 39.93 to 38.fifty two (nS) in 180nm innovation, it's miles seen that the table 6 as 28T full Adder Circuit Voltage Scale diminishes from 2 V to zero.eight V, general strength reduced from 21.39 to 2.916 (µW) and defer faded from 4.939 to 4.seventy four (nS) in 90nm innovation. it's far seen that the desk 8 as 28T full Adder Circuit Voltage Scale diminishes from 1.five V to 0.7 V, general energy reduced from eight.98 to one.713 (µW) and cast off dwindled from four.963 to four.581 (nS) in 45nm improvement.

#### VI. CONFIRMATION

We apprehend the CMR organization for its economic help as CMRIT for the twelve months 2018-19. We thank all the property within the department of (ECE) Electronics and Communications Engineering and the lab workforce for their assist

#### VII. REFERENCES

- Ashish Yadav, Bhawna P. Shrivastava and Ajay Kumar Dadoria,"Low electricity excessive pace 1-piece full Adder Circuit design in DSM generation", IEEE, global conference on facts, correspondence, Instrumentation and manipulate(ICICIC), 2017.

- Ahmed M. Shams, Tarek ok. Darwish and Magdy A. Bayoumi, "overall performance evaluation of Low-power 1-Bit CMOS complete Adder Cells", IEEE Transactions On Very big Scale Integration (Vlsi) systems, Vol. 10, No. 1, February 2002.

- Manoj Kumar, "unmarried piece complete snake configuration utilising eight transistors with novel 3 transistors XNOR door", international magazine of VLSI plan and verbal exchange structures (VLSICS) Vol.2,

- No.four, December 2011., DOI 10.5121/vlsic.2011.2405

- N.Prathima, okay.Harikishore, "shape of a low energy and high execution advanced multiplier utilizing a completely unique 8T snake", international journal of Engineering research and programs, (IJERA) ISSN: 2248-9622 www.Ijera.Com Vol.

- Vaibhav Gupta, Debabrata Mohapatra, Anand Raghunathan., and Kaushik Roy, Fellow, IEEE., Lowstrength virtual sign Processing using Approximate Adders., 0278-0070/\$31.00 c\_ 2012 IEEE. three, problem 1, January - February 2013, pp.1832-1837.

- Michael Keating, David Flynn., Robert Aitkin Alan G, ibbons, Kaijian Shi., "Low power technique manual For gadget-on-Chip layout., Library of Congress control quantity: 2007928355 .,ISBN 978-0-387-71818-7 e-ISBN 978-0-387-71819-4., springer.Com.

- Ronn B. Brashear, Noel Menezes, Chanhee Oh, Lawrence T.Pillage, and M. Beam Mercer., Predicting Circuit overall performance the usage of Circuit-stage Statistical Timing evaluation., branch of electrical and pc Engineering The university of Texas at Austin, Texas 78712., 1066-1409194 \$three.00 zero 1994 IEEE.

- 8. Yaseer A. Durrani a, Teresa Riesgo b., power estimation technique for DSP models digital sign Processing 19 (2009) 213–219., Contents statistics available at science Direct., www.Elsevier.Com/discover/dsp, 1051-2004/\$ see front problem © 2008 Elsevier Inc. All rights held. Doi:10.1016/j.Dsp.2008.09.zero.five.17

- A. M. hints and M. Bayoumi, "A story superior CMOS1bit complete viper mobile," IEEE Transaction on Circuits structures II, Analog virtual sign procedure, vol. forty seven, no. 5, pp. 478–481, may additionally 2000.

- Ahmed M. hints and Magdy An, "An prepared approach for structuring low strength adders," conference file of the Thirty-First Asilomar conference on indicators, systems and computers, vol. 1, pp.757-761, Nov. 1997.

- R. Zimmermann, and W. Fichtner, "Low-control cause styles: CMOS instead of pass-transistor cause," IEEE J. robust kingdom Circuits, vol. 32, no. 7, pp. 1079-1090, Jul. 1997.

- N. Weste and okay. Eshraghian, principles of CMOS VLSI design, A gadget angle, Addison-Wesley, 1993.

- 13. N. Zhuang and H. Wu, "any other shape of the CMOS complete viper," IEEE J. strong kingdom Circuits, vol. 27, no. five, pp. 840–844, might also 1992.

- 14. Yingtao Jiang Al-Sheraidah, A. Yuke Wang Sha, E. also, Jin-Gyun Chung, "A story multiplexer primarily based completely low-manipulate full viper," IEEE Transactions on Circuits and systems: express Briefs, vol. fifty one, no. 7, pp.345-348, Jul. 2004.

- M. Aguirre-Hernandez and M. Linares-Aranda, "CMOS full-adders for power powerful huge variety juggling packages," IEEE Transaction Very large Scale Integration (VLSI) Syst., vol. 19, no. four, pp. 718–721, Apr. 2011.

- M. Alioto, G. Di Cataldo, G. Palumbo, "blended complete viper topologies for superior low-manage math circuits," Microelectronics magazine, vol. 38, no. 1, pp. 130–139, Jan. 2007.

# International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8, Issue-11S2, September 2019

- R. Zimmermann, W. Fichtner, "Low-manage motive patterns: CMOS as opposed to pass-transistor reason," IEEE journal of robust nation Circuits, vol. 32, no. 7, pp. 1079–1090, Jul. 1997.

- 18. Hung Tien Bui, Yuke Wang, and Yingtao Jiang, "structure and evaluation of Low-strength 10-Transistor full Adders the usage of Novel XOR–XNOR Gates," IEEE Transactions on Circuits and systems-II: Analog and virtual sign Processing, vol. forty 9, #1, Jan. 2002.

- 19. N. Zhuan, H. Wu, "some different plan of the CMOS entire snake," IEEE magazine strong-nation Circuits, vol. 27, no. five, pp. 840–844, may additionally 1992.

- C.- ok. Tung, Y.- C. Hung, S.- H. Shieh, and G.- S. Huang," A low-manipulate fast 1/2 of breed CMOS whole snake for installation framework," IEEE convention design and Diagnostics of electronic Circuits and structures., vol. 13. Pp. 1-4, Apr. 2007.

- Anandi, R. Rangarajan, M. Ramesh, "power green viper mobile For Low power Bio scientific gadgets," IOSR Diary of VLSI and sign Processing (IOSR-JVSP) Vol. four, trouble 2, Ver. III, pp 39-forty five Mar-Apr. 2014.

- 22. Mohanraj S, Maheswari M, "energy SERF and changed SERF Adders for extremely Low power design techniques," worldwide conference on conversation technology and gadget design, 2011.

- Deepa, Sampath Kumar V, "examination of Low power 1-piece Adder Cells using diverse XOR-XNOR doorways," IEEE commonplace conference on Computational Intelligence and communique generation, 2015

- 24. Jin-Fa Lin, Yin-Tsung Hwang, Ming-Hwa Sheu, "a unique high-velocity and electricity green 10-Transistor full Adder layout," IEEE Transactions on Circuits and structures-I: regular Papers, vol. Fifty 4, no. five, might also 2007.

- 25. Sujatha, Hiremath and Deepali Koppad, "Low power full Adder Circuit the usage of Gate Diffusion enter (GDI) MUX," verbal exchange and Computing (ARTCom2012), Fourth worldwide conference on Advances in recent technologies, 19-20 Oct. 2012. 18

- Soolmaz Abbasalizadeh, Behjat Forouzandeh, "complete Adder layout with GDI cellular and independent Double Gate Transistor," 20th Iranian assembly on electrical Engineering, (ICEE2012), Tehran, Iran, might also 15-17, 2012.

- 27. Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang, Edwin Sha, and Jin-Gyun Chung, "a novel Multiplexerbased Low-power full Adder," IEEE Transactions on Circuits and systems-II: explicit BRIEFS, vol. 51, no. 7, July 2004.

- I. S. Abu-Khater, A. Bellaouar, M. I. Elmasry, "Circuit techniques for CMOS low-manage superior multipliers," IEEE journal SolidState Circuits, vol. 31, no. 10, pp. 1535–1546, Oct. 1996.

- 29. Arvind Nigam, Raghvendra Singh, "similar evaluation of 28T full snake with 14T full viper the use of 180nm," standard magazine of Engineering technological know-how improve studies;2(1), pp.27-32, March 2016.

- Anuj Kumar Shrivastava, Shyam Akashe," layout excessive execution and occasional power 10T complete Adder cellular using Double Gate MOSFET at 45nm generation," international convention on control, Computing, conversation and substances (ICCCCM), 2013

- 31. Sneh Lata Murotiya, Anu Gupta, "shape of fast ternary entire viper and three facts XOR circuits the use of CNTFETs," twenty eighth international conference on VLSI design and fourteenth global conference on Embedded systems, 2015

- 32. Partha Bhattacharyya, Bijoy Kundu, Sovan Ghosh, Vinay Kumar," overall performance evaluation of a Low-energy

high-speed Hybrid 1-piece full Adder Circuit," IEEE Transactions on Very big scale Integration (VLSI) structures, vol. 24, no. 11, Non. 2015.