## **REVIEW ARTICLE**

# Physics of semiconductor power devices

To cite this article: A Blicher 1982 Rep. Prog. Phys. 45 427

View the article online for updates and enhancements.

## Related content

- <u>Microwave semiconductors devices</u>

.J.F. Sitch

- New unorthodox semiconductor devices K Board

- The electrical characterisation of semiconductors

P Blood and J W Orton

## Recent citations

- Piezo-phototronic Effect Enhanced Responsivity of Photon Sensor Based on Composition-Tunable Ternary CdSxSe1-x Nanowires Guozhang Dai et al

- The Gamma Irradiation Responses of Yttrium Oxide Capacitors and First Assessment Usage in Radiation Sensors Saleh Abubakar *et al*

- Optimization of the window layer in large area silicon heterojunction solar cells Yue Zhang et al

## Physics of semiconductor power devices

Adolph Blicher†

#### Abstract

Semiconductor power devices are designed to rapidly switch or amplify high currents, to support high voltages, and to control electric power. Because of these requirements, their topographies and structures are different from those of small-signal devices. Specific designs are the result of the understanding of the physics of p-n junction HV breakdown, gain variation at high currents, current instabilities, etc. After introducing elementary semiconductor structures, the article reviews the basic principles of the operation of bipolar and field-effect power transistors and thyristors. This is followed by a discussion of phenomena of special interest for power devices: junction avalanche breakdown, the effect of the current level on the current gain, dynamic and static behaviour at high currents and thermal properties and instabilities. The review includes recent advances in device physics and introduces the reader to new methods of improving device performance.

Power is a relative concept—at microwave frequencies a few watts is a very large quantity; this review therefore includes a section on microwave power devices.

This review was received in September 1981.

<sup>†</sup>Formerly with RCA Laboratories, Solid State Technology Center, Somerville, NJ, USA.

| Co | ni | te | n | ts |

|----|----|----|---|----|

|    |    |    |   |    |

| J ( ) 2. |                                                              | Page       |

|----------|--------------------------------------------------------------|------------|

| 1.       | Introduction                                                 | 429        |

|          | 1.1. Power devices versus small-signal devices               | 429        |

|          | 1.2. Basic components                                        | 429        |

|          | 1.3. Some fabrication techniques                             | 431        |

| 2.       | Basics of power device operation                             | 432        |

|          | 2.1. Bipolar power transistors                               | 432        |

|          | 2.2. Bipolar power thyristors                                | 434        |

|          | 2.3. Junction field-effect power transistors (JFET)          | 437        |

|          | 2.4. Field-effect thyristor                                  | 439        |

|          | 2.5. Metal Schottky barrier field-effect transistor (MESFET) | 441        |

|          | 2.6. Insulated gate field-effect power transistor (IGFET)    | 442        |

| 3.       | Avalanche breakdown                                          | 445        |

|          | 3.1. Avalanche breakdown mechanism                           | 445        |

|          | 3.2. Bipolar transistor breakdown voltage                    | 445        |

|          | 3.3. JFET and MOSFET breakdown voltage                       | 446        |

| 4.       | Improvement methods of breakdown voltage rating              | 446        |

|          | 4.1. Collector and drain structures                          | 446        |

|          | 4.2. Junction contouring                                     | 446        |

|          | 4.3. Depletion and substrate etching                         | 448        |

|          | 4.4. Depletion region control by ion implantation            | 448        |

|          | 4.5. Field plates, guard rings and channel stoppers          | 449        |

| 5.       | Bipolar power transistor current gain                        | 451        |

|          | 5.1. Base widening                                           | 451        |

|          | 5.2. Emitter crowding                                        | 452        |

|          | 5.3. Emitter efficiency                                      | 453        |

|          | 5.4. Current gain fall-off                                   | 454        |

| 6.       | Methods of gain improvement                                  | 454        |

|          | 6.1. Bipolar devices                                         | 454        |

|          | 6.2. Field-effect transistors                                | 455        |

| 7.       | Voltage drop in power devices                                | 456        |

|          | 7.1. On-state voltage drop of bipolar transistors            | 456        |

|          | 7.2. On resistance of MOSFET                                 | 456        |

|          | 7.3. Thyristor on-state voltage drop                         | 456        |

| 8.       | Dynamic behaviour of power devices                           | 457        |

|          | 8.1. Gain-bandwidth product $(f_T)$                          | 457        |

|          | 8.2. Bipolar transistor switching                            | 458        |

|          | 8.3. Thyristor switching                                     | 460        |

|          | 8.4. Thyristor reverse recovery                              | 461        |

| _        | 8.5. Power MOSFET switching                                  | 463        |

| 9.       | Thermal properties and instabilities                         | 463        |

|          | 9.1. Thermal runaway                                         | 463        |

| 1.0      | 9.2. Current constrictions                                   | 464        |

|          | Surface stabilisation and passivation                        | 465        |

| 11.      | Conclusion                                                   | 465<br>466 |

|          | Acknowledgments                                              | 466        |

|          | References                                                   | 400        |

#### 1. Introduction

## 1.1. Power devices versus small-signal devices

The feature that distinguishes semiconductor power devices from small-signal devices is the magnitude of the requisite currents and voltages. Small-signal devices now encountered almost exclusively in integrated chips, are mostly used as logic switches that are either turned on or off, are reproduced thousands of times on the same crystal chip, and operate with very small currents and low voltages to achieve negligibly small power losses.

Power devices, on the other hand, are meant, in most cases, to rapidly switch or amplify high currents and to support high voltages, dissipating as little power as possible. For example, a colour television horizontal deflection transistor is required to turn on a current of 10 A and to support in the off state 2.5 kV. Special techniques such as p-n junction shaping are needed to achieve the requisite high-voltage ratings. The high-current requirement, on the other hand, leads to topographical and structural designs that permit the achievement of high-current gains and minimal internal voltage drops when the device is turned on. The product of this voltage drop and current determines the magnitude of the device's thermal dissipation and its junction temperature, which for silicon is not allowed to exceed 150-170°C.

To achieve a reasonable cost, the area of the semiconductor chip used for the device should be made as small as is compatible with the acceptable internal voltage drop and other requirements such as current gain and speed of operation. A small device area not only reduces the cost of the utilised semiconductor material, but also makes it possible to simultaneously process thousands of devices, thus considerably reducing their cost.

Because of some of these considerations, the physical design of power devices substantially differs from that of small-signal processing devices, both in cross-sectional structures and surface geometry. In some cases, the most recent design of power transistors profitted from the progress made in integrated circuit technology. For example, the power metal-oxide-silicon field-effect transistor (MOSFET) is typically designed with thousands of very small elementary cells integrated on the same chip and all working in parallel, in order to increase device current capability and to decrease its internal resistance and voltage drop.

Semiconductor power devices have found innumerable applications both in industrial and consumer equipment such as power conditioning circuits (inverters, converters, power supplies, etc), motor controls, TV horizontal deflection circuits, light dimmers, audio amplifiers, car ignition systems, temperature control circuits, infrared heating, battery charging, printer solenoids, etc.

## 1.2. Basic components

Semiconductor devices always include some combination of p-n junction diodes, metal-insulator-semiconductor capacitors, Schottky barrier diodes and non-rectifying ohmic contacts.

The current flowing in an ideal bipolar diode upon the application of a potential V is

$$I = I_0 \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right] \tag{1.1}$$

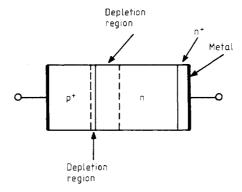

where  $I_0$  is the saturation current flowing when a reverse potential greater than a few kT/q is applied to the diode, T is the junction absolute temperature, k is the Boltzmann constant, q is the electron charge and n equals 1. In non-ideal diodes, the total current contains a component resulting from the generation-recombination of charge carriers in the junction space-charge (depletion) region (figure 1). This component dominates

Figure 1. p<sup>+</sup>-n-n<sup>+</sup> diode. n<sup>+</sup>-region added for better ohmic contact. Plus sign indicates highly doped semiconductor.

the diffusion current for reverse voltages or at low forward biases. Expression (1.1) still holds, but with a different magnitude of  $I_0$  and with n between 1 and 2. At high current densities, 1 in equation (1.1) can be neglected,  $I_0$  acquires a different value, and n = 2 because of the appearance of an electric field in the n-base.

An excessively high reverse voltage applied to the diode results in a very rapid increase in the reverse current due to the carriers' avalanche multiplication and junction breakdown.

A Schottky barrier diode, like a p-n junction, has rectifying properties and consists of a metal electrode deposited on a non-degenerate semiconductor surface. The approximate current-voltage relationship of the Schottky diode with uniformly doped silicon is similar in form to expression (1.1) with the constant n slightly higher than unity for low current levels.

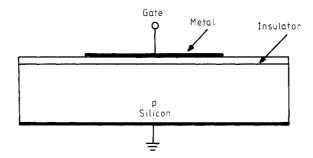

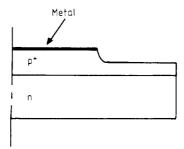

The metal-oxide-silicon (MOS) capacitor, the most important of the metal-insulator-semiconductor capacitors, consists of a metal electrode (gate) deposited on an oxidised silicon substrate (figure 2).

Due to the difference between the magnitudes of the metal and silicon work functions, an electrically charged double layer is formed at the metal-silicon interface even in the absence of any external voltage. In the case where the metal work function  $q\varphi_{\rm m}$  is smaller than that of silicon  $q\varphi_{\rm Si}$  some electrons are transferred from the gate to the silicon substrate by some very slightly conductive path external to the insulator, and the gate becomes positively charged. The p-silicon substrate becomes negatively charged at the surface because some of the mobile holes are repelled by the positive bias of the gate. The p-type silicon behaves like being less p-doped (depletion) so

Figure 2. Metal-oxide-silicon (MOS) capacitor.

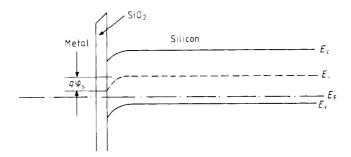

that, at the surface, the silicon band diagram bends as shown in figure 3. The amount of band bending is measured by the surface potential  $\varphi_s$ .

In order to revert the bands to the flat-band condition, it is necessary to apply a flat-band voltage  $V_{\rm FB}$  to the gate equal to the metal-oxide-silicon work function difference.

Figure 3. Energy band bending at the silicon surface.  $\varphi_s$  is the surface potential.

The application of a small positive external gate potential  $V_{\rm G} > V_{\rm FB}$  results in the repulsion of holes from the surface and in the downward band bending. A still higher positive gate voltage attracts electrons to the silicon surface so that it may acquire an excess of electrons and become n-type. This is known as surface inversion and is characterised by the Fermi level (figure 3) crossing the intrinsic level  $E_{\rm i}$ . The gate voltage required for strong inversion is known as the threshold voltage  $V_{\rm T}$ .

A negative gate potential results in an increase in the number of holes at the silicon surface, i.e. in surface accumulation. In present-day MOs power devices, the gate consists of some refractory metal such as tungsten or, more often, highly-doped polycrystalline silicon.

Fixed and mobile positive oxide charges and interface states have a pronounced effect on the MOS capacitor flat-band and threshold, and also on the silicon surface stability.

#### 1.3. Some fabrication techniques

The most commonly used junction formation technique consists of high-temperature surface impurity deposition with subsequent high-temperature diffusion. Impurity

deposition can also be accomplished by the HV implantation of an appropriate impurity ion.

Commonly used n-type impurities are phosphorus and arsenic. Boron, aluminium and gallium, on the other hand, are frequently used as p-type impurities.

An 'infinite' impurity source, such as phosphorus oxychloride (POCl<sub>3</sub>) vapour, results in a deposited impurity profile with a complementary error function distribution. On the other hand, diffusion from a *thin* predeposited layer results in a Gaussian impurity distribution.

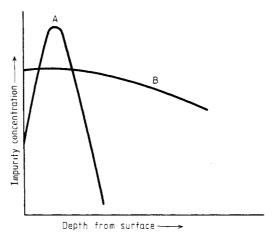

Ion implantation is widely employed for those cases when an accurately reproducible doping profile is essential. It consists of bombarding the semiconductor surface with the desired impurity ions in an apparatus that is essentially a modified mass spectrometer in which the impurity ions are accelerated to very high velocities by electrical potentials of up to some hundreds of thousands of volts. The implanted impurity distribution is Gaussian but it flattens when followed by a diffusion step so that the concentration peak shifts from under the silicon surface to the surface itself (figure 4). Ion implantation is not useful, however, for very deep diffusions.

Figure 4. Concentration profile of ion implant (A) before and (B) after diffusion.

The high-resistivity silicon substrate used for the fabrication of high-voltage devices may be either bulk or epitaxially grown. For breakdown near or above 1 kV, the best material is the transmutation-doped silicon crystal (Herrman and Herzer 1975). Very uniformally doped silicon, free of resistivity striations, is produced by bombarding silicon crystal with slow thermal neutrons, which transmute the uniformly distributed silicon isotope <sup>30</sup>Si into phosphorus <sup>31</sup>P. Thus, the silicon crystal becomes lightly and very uniformly doped with an n-type impurity. For voltages below 1 kV, silicon epitaxial layers are often adequate for the fabrication of bipolar and field-effect devices.

## 2. Basics of power device operation

#### 2.1. Bipolar power transistors

A bipolar type transistor consists of the emitter base and collector-base junctions separated by a base of width  $W_{\rm B}$  smaller than the minority carrier diffusion length L.

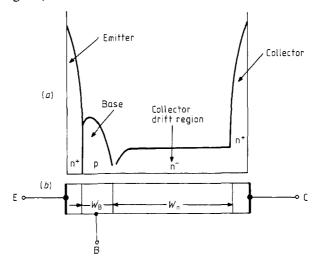

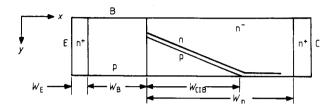

The collector structure of an n-p-n power device comprises an n -drift region (figure 5) to support the requisite high collector voltage. (A p-n-p power transistor would have a p-drift region.)

Figure 5. (a) Diffusion profile and (b) structure of the  $n^+pn^-n^+$  power transistor.

With the emitter forward-biased and the collector reverse-biased the DC current gain of a transistor in the common-base circuit is

$$\alpha = \gamma \alpha_{\rm T} \tag{2.1}$$

where  $\alpha_T$  is the base transport factor given by

$$\alpha_{\rm T} = \frac{1}{\cosh\left(W_{\rm B}/L\right)}.\tag{2.2}$$

$\gamma$  is the emitter efficiency defined as the ratio of the current injected by the emitter into the base to the sum of the currents injected into the base and from the base into the emitter.

The collector current  $I_{\rm C}$  is related to the emitter current  $I_{\rm E}$  by

$$I_{\rm C} = \alpha I_{\rm E} + I_{\rm CBO} \tag{2.3}$$

where  $I_{\rm CBO}$  is the collector leakage current.

At the common-emitter configuration the current gain is

$$h_{\rm FE} = \frac{\alpha}{1 - \alpha} \tag{2.4}$$

and the emitter efficiency

$$\gamma_{\rm E} = \frac{\gamma}{1 - \gamma} \tag{2.5}$$

is the ratio of the current injected by the emitter into the base to the current injected by the base into the emitter.

It can be shown (see, for example, Blicher 1981) that for an n-p-n transistor

$$\gamma_{\rm E} = \frac{Q_{\rm E}}{D_{\rm p}} \frac{D_{\rm n}}{Q_{\rm B}} \tag{2.6}$$

where  $Q_{\rm E}$  is the total *number* of charges per unit area in the effective emitter and  $Q_{\rm B}$  is the total *number* of charges per unit area in the base.  $D_{\rm p}$  and  $D_{\rm n}$  are the hole and electron diffusivities, respectively. Q/D ratios are known as *Gummel numbers* (Gummel 1961, Gummel and Poon 1970).

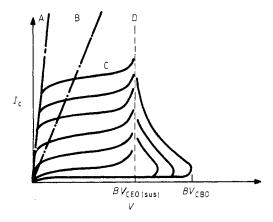

The I-V characteristics of a high-voltage power transistor in the common-emitter configuration can be represented by the diagram of figure 6 with four distinct parts:

Figure 6. Saturation (A), quasi-saturation (B), active (C) and breakdown (D) regions of an  $n^+pn^-n^+$  power transistor.

the saturation, quasi-saturation, active and breakdown regions. If the load line intersects the saturation or quasi-saturation region the device is turned on when operating as a switch with the collector forward-biased. The active region is traversed by the load line during turn-off and intersected when the device operates as an amplifier. The collector breakdown voltage  $BV_{\rm CBO}$  occurs with the emitter circuit open and is equal to the collector junction breakdown voltage. The  $BV_{\rm CEO(sus)}$  is the lowest sustained collector-to-emitter breakdown voltage with the base circuit open. It is substantially lower than  $BV_{\rm CBO}$  (Moll  $et\ al\ 1970$ )

$$BV_{\text{CEO(sus)}} = fBV_{\text{CBO}}(1 - h_{\text{FEO}})^{-1/n}$$

(2.7)

where  $h_{\rm FEO}$  is the common-emitter peak current gain. For step junctions,  $f \approx 0.65$  and n = 4 for an n-p-n transistor and lower voltages, and n = 6 for higher (1000 V) voltages.

#### 2.2. Bipolar power thyristors

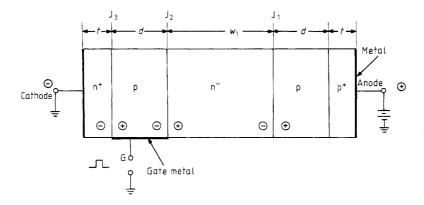

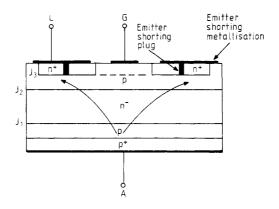

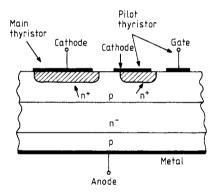

The silicon-controlled rectifier (SCR), the Triac (triode AC switch) and the Shockley diode belong to the class of semiconductor devices known as thyristors (see, for example, Blicher 1976). The SCR is a four-layer pnpn structure (figure 7) consisting of an n<sup>+</sup> cathode emitter, p-base, n<sup>-</sup>-base, and p-anode emitter. The control electrode

Figure 7. Schematic representation of an SCR. Junction polarities shown are for the forward blocking state.

G is known as the gate. Without the gate, the structure is known as the pnpn Shockley diode which can be activated by the application of a high anode voltage.

In the turn-off state the positive (forward) potential applied to the thyristor anode is blocked by the reverse-biased centrally located junction,  $J_2$ . Junction polarities for this situation are shown in figure 7. A negative potential applied to the anode is supported by the then-reverse-biased junctions  $J_1$  and  $J_3$ . The thyristor is turned-on by the application of a short positive-current pulse to the gate G but is turned off either by opening the anode circuit or by applying a negative (reverse) potential to the anode. When the thyristor is turned on, all three junctions are forward-biased.

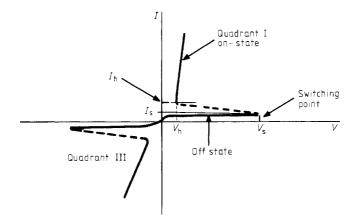

An SCR conducts only in one current direction; its I-V characteristic is shown on the right of figure 8 (quadrant I). To obtain the bidirectional conduction necessary for AC applications, two pnpn structures with one p-gate are integrated back-to-back on the same silicon chip, forming a Triac, with the I-V characteristics of figure 8. The Triac can be turned on in either quadrant I or III.

$I_s$  and  $V_s$  are the coordinates of the variously called switching, turn-on or breakover point.  $I_h$  and  $V_h$  are the coordinates of the holding point beyond which the device is in the on state.

Figure 8. I-V characteristics of an SCR (quadrant I) and of a Triac (quadrants I and III).

An SCR can be considered as consisting of an npn and a pnp transistor sharing the same junction  $J_2$  as their common collector junction. The gate is usually connected to the p-base. Only a small saturation (leakage) current flows in the device when a positive potential is applied to the anode. Upon the application of a positive gate potential, the  $n^+$ -emitter (cathode) starts emitting electrons and the collector of the npn transistor provides the n-base with electrons which bias the p-emitter (anode) in the forward direction. The pnp transistor becomes activated, supplying a hole current that is collected by  $J_2$  and drives the p-base of the npn transistor. The effect becomes regenerative so that both transistors become saturated, i.e. highly conductive with all three junctions forward-biased.

The turn-on at the  $I_s$ - $V_s$  point takes place when the anode current  $I_A$  starts growing extremely fast as a function of the gate current  $I_G$ , i.e. when

$$\frac{\mathrm{d}I_{\mathrm{A}}}{\mathrm{d}I_{\mathrm{G}}} = \frac{\alpha_2}{1 - (\alpha_1 + \alpha_2)} \to \infty. \tag{2.8}$$

$\alpha_1$  and  $\alpha_2$ , the small-signal common-base current gains of the pnp and the npn transistors, respectively, are very small at low current levels but rapidly increase as the current density increases. The region between the turn-on and the holding points is unstable so that the device switches very fast for sufficiently high gate driving current.

To avoid undesirable switching either by the leakage currents at high temperatures or by capacitive currents, SCR are usually provided with an n-emitter short that consists of, for example, cathode metallisation extended over the p-base as shown by figure 9. A shorted emitter has zero efficiency at low currents but a high efficiency at high

Figure 9. SCR cathode with two types of emitter shorts.

currents since some part of the anode current is flowing toward the shorts without reaching the  $n^+$ -emitter. The capacitive and thermally generated currents flow at least partially through the shorts so that the sum of the  $\alpha$  reaches unity much later. This way a shorted emitter provides immunity to the capacitive current  $C \, dv/dt$  and allows the device to operate at higher temperatures. Laterally flowing current causes a lateral voltage drop and forward-biases the emitter, making the emitter shorting less effective. This can be avoided by designing emitters consisting of narrow fingers and/or by providing additional shorts, known as shorting holes or plugs as depicted by figure 9.

2.2.1. Forward and reverse thyristor blocking capability. In the off state (no conduction) the thyristor centre junction  $J_2$  must support the high positive (forward) potential applied to the anode, since the  $J_1$  and  $J_3$  junctions are forward-biased. In the case of the non-shorted emitter, the  $J_2$  junction breakdown BV and the breakover voltage  $V_{\rm BRO}$  (the voltage that causes the thyristor to turn-on without gate action) is given very approximately by (Herlet 1968a, b)

$$V_{\rm BRO} = BV(1 - \alpha_1 - \alpha_2)^{1/n} \tag{2.9}$$

where *n* is between 4 and 6 for the step junctions. With a shorted cathode (2.9) simplifies still further since at low currents  $\alpha_2 \approx 0$ .

To turn off the thyristor, the anode voltage is made negative. This reverse voltage is supported by the  $J_1$  junction since  $J_2$  becomes forward-biased, and  $J_3$  breaks down at very low voltages due to the highly-doped p-base. The device breakdown voltage is, therefore, that of an open-base pnp transistor and is about the same as the breakover voltage with shorted n-emitter (Herlet 1968a, b), i.e.

$$V_{\text{CEO(sus)}} = BV(1 - \alpha_1)^{1/n}.$$

(2.10)

In many circuits, such as those used for inverters, the reverse-voltage blocking capability is not utilised and the SCR may be designed to block only the forward potential. This allows more freedom to improve other device parameters such as the forward-blocking capability or the forward voltage drop. Such a device is known as a reverse conducting thyristor (RCT) (Kokosa and Tuft 1970). Since the anode of an RCT does not support any appreciable voltage, it may be shorted similarly to the cathode. This prevents the pnp transistor from magnifying the  $J_2$  junction leakage current and makes the forward breakdown voltage equal to the  $J_2$  junction breakdown voltage since now both  $\alpha_1$  and  $\alpha_2$  are negligibly small at low temperatures.

2.2.2. Light-activated thyristors. These devices are mainly useful for effective isolation of the triggering device from the main thyristor switch. They are used, for example, to turn on high-voltage transmission lines (Gerlach 1977).

To optically trigger the thyristor, the active region of the pnpn structure is illuminated with light whose energy  $h\nu$  exceeds that of the silicon energy gap. The incident light may be introduced into the p-base through an opening in the central portion of the cathode or through a thin n<sup>+</sup>-emitter (Konishi *et al* 1980). The light generates charge carriers that provide hole and electron currents for the thyristor's p- and n-base, respectively. For very high power devices, smaller auxiliary optically activated thyristors are used to fire the main device. Light-activated thyristors may be easily connected in series to support very high potentials of the order of several kilovolts.

## 2.3. Junction field-effect power transistors (JFET)

Field-effect (unipolar) transistors operate primarily by the drift of the majority carriers whereas the bipolar devices operate by diffusion and drift of the minority and majority carriers.

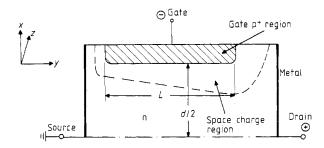

Figure 10 represents schematically one-half of an n-channel JFET. The electron current flowing in the device from the negative source to the positive drain is modulated by the device control electrode, the gate, consisting of the p<sup>+</sup>-n junction. The variable reverse potential applied between the gate and the source changes the width of the

Figure 10. Schematic representation of an n-channel junction field-effect transistor (JFET).

gate junction space-charge region and thus controls the magnitude of the electron current.

By computing the ohmic voltage drop along the conducting channel (see, for example, Blicher 1981), it can be shown that at drain voltages much smaller than the gate-to-source voltage the drain current can be expressed by

$$I_{\rm D} = G_0 V_{\rm D} f(V_{\rm G})$$

(2.11)

where

$$G_0 = q\mu_{\rm n} N_{\rm D} Z d/L \tag{2.12}$$

and

$$f(V_{\rm G}) = 1 - \left(\frac{8\epsilon_{\rm s}(V_{\rm i} - V_{\rm G})}{qN_{\rm D}d^2}\right)^{1/2}$$

(2.13)

where q is the electron charge,  $\mu_{\rm n}$  is the electron mobility in the n-type channel,  $\epsilon_{\rm S}$  is the silicon permittivity, Z is the channel width in the Z direction perpendicular to the page, L is the channel length (figure 10), d is the maximum possible channel width,  $V_{\rm i}$  is the gate-junction built-in voltage,  $V_{\rm G}$  is the applied gate potential and  $V_{\rm D}$  is the drain-to-source voltage. At low drain voltages, the current depends linearly on  $V_{\rm D}$  but varies as the square root of the gate voltage as one would expect because of the assumption that the gate is an abrupt junction.

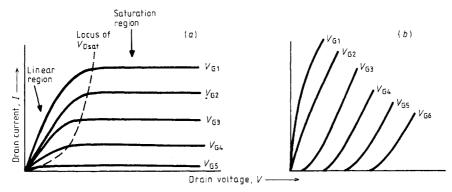

The output characteristics of a JFET (figure 11(a)) show that close to the origin the drain current  $I_{\rm D}$  varies linearly with the drain voltage. At larger voltages its growth slows down; eventually,  $I_{\rm D}$  becomes almost constant and independent of  $V_{\rm D}$ , i.e. it saturates. This takes place when the gate-junction space-charge regions begin to touch each other at some saturation voltage  $V_{\rm Dsat}$ . For drain voltages greater than  $V_{\rm Dsat}$ , the drain current partially flows through the drain space-charge region, where, for electronic fields greater than  $10^4~{\rm Vcm}^{-1}$  the electron velocity reaches its maximum value of  $v_{\rm s} \simeq 10^7~{\rm cm~s}^{-1}$ . As the drain voltage increases beyond  $V_{\rm Dsat}$ , the space-charge region moves toward the source, only very slightly decreasing the channel length and increasing the drain current somewhat. Consequently, the I-V characteristic in the saturation region has a non-zero slope, i.e. the saturation conductance has some finite value. The drain current in the saturation region is proportional to  $G_0$  and depends on the first and 3/2 power of the gate voltage.

Figure 11. (a) Pentode-like and (b) triode-like I-V characteristics of a n-channel JFET or n-channel MOSFET with the gate voltage as a parameter. The JFET drain current increases with the decreasing magnitude of the negative gate potential; the MOSFET current increases with increasing positive gate voltage.

The effectiveness of the gate voltage's control over the drain current is expressed by the transconductance

$$g_{\rm m} = \frac{\partial I_{\rm D}}{\partial V_{\rm G}} \Big|_{V_{\rm D} = \text{constant}}.$$

(2.14)

In the saturation region the transconductance reaches its maximum value which is equal to the conductance in the linear region.

2.3.1. IFET with non-saturating triode-like characteristics. The I-V characteristics of figure 11(a) are known as pentode-like; those of figure 11(b) are triode-like (Yamaguchi et al 1975, Nishizawa et al 1975, Yamaguchi and Kodera 1977, Nishizawa and Yamamoto 1978, Gupta 1980, Ohmi 1980). In a very short completely depleted channel a potential barrier at the source prevents the current from flowing at low drain voltages. At sufficiently high drain potential, the barrier is lowered by the drain's electrostatic field so that an electron current starts flowing. The magnitude of this current depends exponentially on the drain voltage  $V_D$ . In order to obtain triode-like operation, the maximum channel width should be small, of the order of a few  $\mu$ m, and the gate length should be smaller than one-half of the channel width (figure 10). If the gate is too long, the drain electrostatic field becomes too small to reduce the barrier height and the characteristics remain pentode-like.

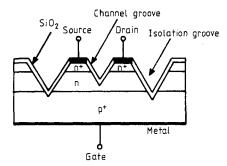

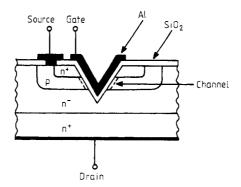

An example of a JFET structure known as the V-groove JFET is shown by figure 12 (Mok and Salama 1978). The V-shaped channel region is obtained by anisotropic etching of the silicon crystal. For the high-current handling capability, there are many such devices on the same chip connected in parallel. Therefore, there are special isolation grooves etched as shown in the figure.

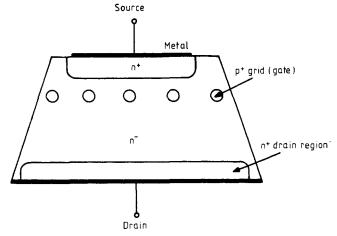

Another JFET structure, depicted by figure 13, is known as the static induction transistor (Nishizawa et al 1975). The embedded mesh-like p<sup>+</sup>-grid acts as a field-effect transistor gate. This device was constructed with a very short channel length and minimised source series resistance to obtain triode-like characteristics.

#### 2.4. Field-effect thyristor

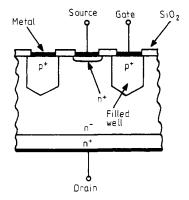

The field-effect thyristor (figure 14) (Wessels and Baliga 1978, Baliga 1981) is fabricated by using anisotropic preferential etching to obtain deep wells (grids) filled

Figure 12. Vertical V-grooved JFET (from Mok and Salama 1978).

Figure 13. Static induction transistor (SIT) (from Nishizawa et al 1975).

Figure 14. Junction field-effect thyristor (from Baliga 1981).

by epitaxial p<sup>+</sup> single-crystal silicon. The grid acts as a junction gate, forming a depletion region that modulates the current flowing from the cathode to the anode. These devices are normally in the on state with the anode positively biased. The current flow can be stopped by reverse-biasing the grid. Field-effect thyristors are capable of operation at temperatures up to 200°C, considerably higher than bipolar

thyristors which normally cannot work above 140°C. This is possible because this type of device does not exhibit the regenerative switching mechanism which is very sensitive to the device temperature.

## 2.5. Metal Schottky barrier field-effect transistor (MESFET)

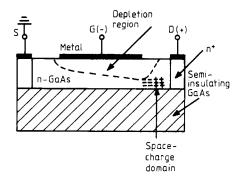

The p<sup>+</sup>-n junction gate of the junction field-effect transistor can be replaced by a Schottky barrier consisting of a metal electrode deposited on a semiconductor surface. This type of gate is particularly useful for GaAs devices where good-quality p-n junctions or high-quality surfaces are more difficult to achieve than in silicon. MESFET are very useful as microwave devices at frequencies above 4 GHz. Figure 15 (Liechti

Figure 15. Schematic representation of MESFET (from Liechti 1976).

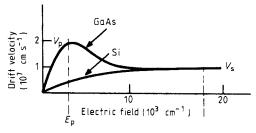

1976) represents a schematic cross section of a device consisting of an n-type GaAs film deposited on a semi-insulating GaAs substrate which also provides a thermal path to a heat sink. Some part of the n-region surface is metallised to form the Schottky barrier. The conducting channel lies below the surface so that the high bulk mobility of GaAs can be fully utilised (the surface mobility is always lower than that of the bulk). Electron mobility in GaAs at room temperature is  $8800 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$  whereas that for very lightly doped silicon crystal is only  $1350 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . The dependence of the GaAs electron mobility on the electric field is different from that of silicon (figure 16). The upper curve for GaAs shows the presence of a peak value equal to about  $2v_s$  at an electric field of about  $3 \times 10^3 \text{ V cm}^{-1}$ . For higher fields, the velocity eventually drops down to the saturated velocity  $v_s \approx 10^7 \text{ cm s}^{-1}$  at an electric field of about  $1.8 \times 10^4 \text{ V cm}^{-1}$ . The theory of GaAs MESFET operation is further complicated by the appearance of the Ridley-Gunn stationary space-charge domain

Figure 16. Electron mobility of silicon and GaAs as a function of electric field (from Ruch 1972).

formation (figure 15) (Liechti 1976, Shur 1978). The electron drift velocity in a short channel device reaches its peak velocity  $v_p$  close to the channel centre but drops down to its  $v_s$  value under the drain side of the gate edge, where the channel width is narrowest (figure 15). As a result, electrons accumulate in this region to preserve the current continuity. Beyond this region the channel thickness increases, the field decreases and the electron velocity goes up so that less electrons are needed to carry the same current; therefore, a positive space-charge region is formed.

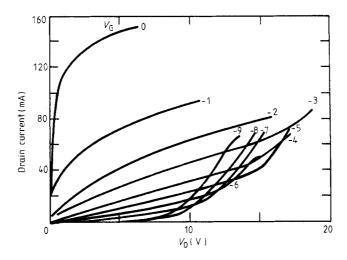

Figure 17 (Wemple et al 1980) represents the I-V characteristics of a power GaAs MESFET. At a drain voltage  $V_D \approx 5 \, \mathrm{V}$  and  $V_G \approx -8 \, \mathrm{V}$ , there is a change in the characteristics' shape and the current beyond this point increases as the magnitude of the reverse gate potential increases. This anomaly, attributed to avalanche breakdown in the drain-gate region, limits the maximum obtainable power output. GaAs MESFET can be fabricated to deliver several watts of power even at frequencies as high as 20 GHz.

Figure 17. MESFET I-V characteristics with gate voltage as a parameter (from Wemple et al 1980).

## 2.6. Insulated gate field-effect power transistor (IGFET)

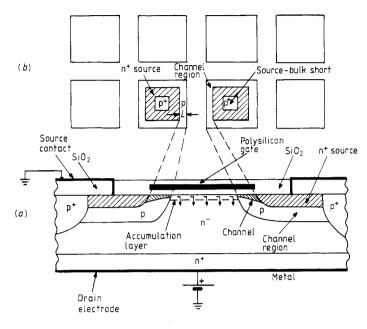

The most common among the insulated gate field-effect transistors is the metal-oxide-silicon field-effect transistor (MOSFET) with silicon dioxide as the gate insulator. The most useful, because of the high electron mobility, is the n-channel enhancement power MOSFET (figure 18). The  $n^+$ -source region and the p-type bulk (channel region) are connected together by the highly conducting  $p^+$ -diffusion and are kept at ground potential. The drain junction is positively biased with respect to the source. For a positive gate-to-source voltage greater than the threshold voltage  $V_T$ , the p-channel becomes induced at the surface and starts conducting electrons from the source to the drain. The drain is a vertical structure for better silicon surface utilisation and easier heat sinking. The device drain contains an  $n^-$ -drift region to support the requisite high voltage.

The I-V characteristics of a MOSFET are very similar to those of a JFET (figure 11(a)). As the positive gate voltage is increased, the conductance of the channel increases and so does the drain current. At low drain voltages, the drain current is

Figure 18. (a) Schematic cross section of a multichannel MOSFET with vertical n<sup>-</sup>-drain drift region. (b) Schematic representation of the multiple cell geometry.

linearly dependent on the drain and gate voltages and is given by

$$I_{\rm D} \simeq G_0(V_{\rm G} - V_{\rm T})V_{\rm D}$$

(2.15)

with

$$G_0 = \frac{Z}{L} \mu_n \frac{\epsilon_i}{x_i}.$$

(2.16)

Z is the channel width, L is the channel length,  $\mu_n$  is the electron mobility at the surface,  $x_i$  is the insulator thickness under the gate and  $\epsilon_i$  is the insulator permittivity. The threshold voltage  $V_T$  is the gate voltage necessary to obtain strong inversion. Its magnitude depends on the nature of the metal used for the gate, channel length, various surface charges, etc. In power devices, the gate conductor is most often highly doped polycrystalline silicon, which lends itself to the fabrication of the self-aligned gates.

The MOSFET I-V characteristics (figure 11(a)) exhibit a linear portion at low currents and become saturated at the drain voltage  $V_{Dsat}$ . Beyond this point, the drain current increases only very slightly with the drain voltage. If the drain voltage is made high enough, the drain junction eventually undergoes an electrical breakdown.

A very approximate analysis gives for the saturation current (see, for example, Blicher 1981)

$$I_{Dsat} \simeq \frac{1}{2}G_0(V_G - V_T)^2$$

(2.17)

with

$$V_{\rm G} - V_{\rm T} \simeq V_{\rm Dsat}. \tag{2.18}$$

$V_{\mathrm{Dsat}}$  is constant for a given gate voltage. The channel resistance is only very slightly affected by the extension of the space-charge region into the channel; consequently, the saturation drain current is almost independent of the drain voltage. However, in very short channels—of the order of a few micrometres—the depletion region affects appreciably the channel length. If the channel region (also known as the body or substrate) is very lightly doped, the drain depletion layer is wide even at the small drain voltages. In this situation, current carriers may be injected from the source over a potential barrier into the drain depletion region (Ohmi 1979). The modulation of barrier height by the drain electrostatic field results in the non-saturating triode-like I-V characteristics, with the drain current exponentially dependent on the drain voltage (figure 11(b)).

The MOSFET transconductance  $g_m$  is defined the same way as that of the JFET. In the linear region

$$g_{\rm m} = G_0 V_{\rm D} \tag{2.19}$$

and in the saturation region

$$g_{\text{msat}} \simeq G_0(V_{\text{G}} - V_{\text{T}}). \tag{2.20}$$

The transconductance is larger for smaller channel lengths and larger channel widths. The MOSFET structure of figure 18 is known as the vertical D-MOS transistor. D stands for the double-diffusion process. First the p-channel region (bulk) is diffused into the n<sup>-</sup>-drain region; then the n<sup>+</sup>-source is diffused. This way, it is possible to accurately define the very small lateral spacing between the two diffusions necessary for small channel lengths. The vertical structure allows excellent silicon 'real estate' utilisation and effective device heat sinking. High current capability is achieved by making the channel width Z very large by using a multiplicity of elementary MOSFET (cells) (figure 18).

Another important power transistor structure is the vertical VMOSFET (figure 19) (Salama and Oakes 1978). The channel region is established here by double diffusion of the p-channel region and the  $n^+$ -source with subsequent preferential etching of a V-groove on  $\langle 100 \rangle$  oriented surface. The V-groove defines the gate region. A power device contains a multiplicity of such structures on the same silicon chip.

If the groove etching is stopped at the right moment then the groove is shaped like the letter U, whose flat bottom helps to reduce the device series resistance.

Figure 19. V-groove MOSFET (from Salama and Oakes 1978).

#### 3. Avalanche breakdown

#### 3.1. Avalanche breakdown mechanism

The electrical breakdown of HV pn junctions takes place by impact ionisation (avalanche breakdown). The free carriers present in the junction depletion region acquire enough energy at the fields higher than  $10^5$  V cm<sup>-1</sup> to break the silicon crystal covalent band, liberating more free carriers, which in turn create more electron-hole pairs and so on. This positive feedback mechanism results in an avalanche of holes and electrons and in the junction electric breakdown. The ratio of the output current to the input current entering the avalanche multiplication region is given by the multiplication factor M which at junction breakdown goes to infinity. If the reverse junction potential is  $V_R$  and the junction breakdown voltage is BV (Moll et al 1970) then the following empirical relationship exists for the multiplication factor:

$$M = \left[1 - \left(\frac{V_{\rm R}}{fBV}\right)^n\right]^{-1} \tag{3.1}$$

where f is a parameter depending on the type of the junction impurity profile, the carrier type and the breakdown voltage. At about 1 kV and for a step junction  $f \approx 0.65$  for electrons. The exponent n is equal to about 6 under the same conditions.

The pn junction breakdown voltage depends on its impurity profile. The breakdown voltage of an abrupt, *plane*, one-dimensional silicon junction with one side heavily doped is (Fulop 1967)

$$BV_1 \simeq 5.3 \times 10^{13} N^{-3/4} V \tag{3.2}$$

where N is the impurity concentration of the lightly doped side.

The breakdown voltage of a linearly graded, unidimensional junction is given by

$$BV_2 \approx 8.93 \times 10^9 a^{-2/5} \text{ V}$$

(3.3)

where a is the net impurity gradient. The avalanche breakdown voltage of the erfc diffused junction lies somewhere between the values given by (3.2) and (3.3).

Due to the high fields present at the corners, the breakdown voltage of diffused planar junctions is always lower than that of plane junctions. The planar junction with cylindrical or spherical corners breaks down at (Sze and Gibbons 1966)

$$BV_3 \simeq 6 \times 10^{13} N^{-3/4} \{ [(n+1+\gamma)\gamma^n]^{1/(n+1)} - \gamma \}$$

(3.4)

where  $\gamma$  is the ratio of the junction depth to the junction depletion layer width at breakdown of the one-sided *plane* abrupt junction. n=1 and 2 for cylindrical and spherical junction, respectively. High breakdown voltages require very deep diffusions unless additional breakdown voltage improvement methods are employed.

#### 3.2. Bipolar transistor breakdown voltage

The collector-to-base breakdown voltage  $BV_{\rm CBO}$ , with the emitter circuit open, is equal to the collector junction breakdown voltage. The lowest collector-to-emitter breakdown voltage is given by (Moll *et al* 1970)

$$BV_{\text{CEO(sus)}} = BV_{\text{CBO}} f (1 - \alpha_0)^{1/n}$$

(3.5)

where  $\alpha_0$  is the peak current gain. For npn transistors f is that for electrons since it is mainly the electrons traversing the collector depletion region that are multiplied. The collector-to-emitter breakdown voltage is considerably lower than  $V_{\rm CBO}$ .

## 3.3. JEET and MOSFET breakdown voltage

In a JFET, the voltage breakdown normally occurs in the drain-gate depletion region where the field is the highest. The drain-gate breakdown voltage is given by

$$BV_{\rm D} \simeq BV_{\rm i} - V_{\rm G} \tag{3.6}$$

where  $BV_i$  is the drain junction avalanche breakdown voltage.

The drain-to-source breakdown voltage of a long channel n-MOSFET is essentially that of the drain junction. This is also true for p-channel devices, regardless of the channel length. n-MOSFET with short channels, of the order of a few micrometres, have the drain-to-source breakdown behaviour like that of npn transistors. The drain-to-source breakdown characteristics exhibit differential negative resistance regions similar to those obtained with bipolar transistors operated in the common-emitter configuration, because the main MOSFET is in parallel with an open base, parasitic, bipolar n<sup>+</sup>pn<sup>+</sup> transistor. The source current undergoes avalanche multiplication in the drain depletion region and creates an excess current flowing laterally from the drain region to the source, creating a voltage drop in the device substrate. This voltage drop forward-biases the source-to-bulk junction which starts acting as the bipolar transistor emitter. The ensuing positive feedback mechanism leads to breakdown characteristics similar to that of open-base transistors. The immunity of the long channel n-MOSFET to the second breakdown (§ 9.2.3) is due to the low current gain of the parasitic device.

The gate oxide breakdown is another important mechanism limiting MOSFET performance. It depends on many factors such as oxide thickness, thermal treatment, temperature, etc. At room temperature, the electric field at breakdown is very approximately equal to  $8 \text{ MV cm}^{-1}$ . Under circumstances that allow metal gate vaporisation, the  $SiO_2$  breakdown can become self-healing.

#### 4. Improvement methods of breakdown voltage rating

#### 4.1. Collector and drain structures

In devices operating above 200 V the requisite breakdown voltage is achieved by adding a high-resistivity n<sup>-</sup>-drift region to the collector or the drain. Further improvement may be achieved by adding a lightly doped epitaxially grown p<sup>-</sup>-region sandwiched between the p-base and the n<sup>-</sup>-collector region. Such an arrangement is known as the n<sup>+</sup>-p- $\pi$ - $\nu$ +n<sup>+</sup> structure (Blicher and Czorny 1969), where  $\pi$  and  $\nu$  stand for the lightly doped p and n regions, respectively. In this case, the depletion layer spreads into both the  $\nu$  and  $\pi$  region and the maximum junction field is lowered.

#### 4.2. Junction contouring

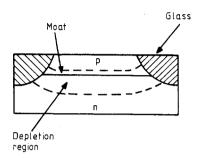

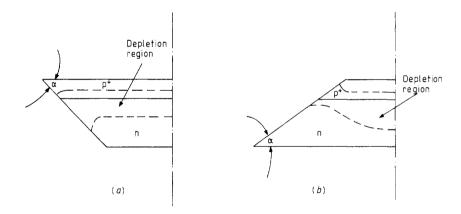

The junction breakdown voltage can be considerably increased by the proper contouring of side surfaces. For devices operating below about 500 V, deep moat etching

(figure 20) sufficiently lowers the surface field avoiding surface breakdown, which always occurs at a lower voltage than the breakdown of the bulk silicon. Moat etching for voltages greater than 500 V is, however, much too erratic to be useful. Mechanical bevelling, used mainly for larger devices, guarantees more uniform and better results. By convention (Davies and Gentry 1969) the bevel angle is positive if the junction area decreases when moving from the more heavily doped to the less-doped junction side (figure 21(a)). It is negative as the area increases (figure 21(b)).

Figure 20. Glass-filled moat for breakdown voltage improvement.

Figure 21. (a) Positive and (b) negative bevel angle convention.

- 4.2.1. Positive bevel. Positively bevelled junctions can achieve maximum possible bulk breakdown voltages. The surface field for the positive bevel is reduced below that in the bulk because at the surface, due to the junction shape, the depletion region expands on the lightly doped junction side and contracts on the heavily doped side. Consequently the breakdown will occur in the bulk, where higher electric fields are acceptable. A device with 45° positive bevel angle will have the peak surface field reduced to about 45% of the maximum bulk field at breakdown (Davies and Gentry 1969).

- 4.2.2. Negative bevel. The peak surface field is also reduced by negative bevelling; however, much smaller bevelling angles are needed than for the positive bevelling. For a negative bevel the minimum distance between the depletion layer boundaries

occurs in the silicon interior (figure 21(b)) so that the maximum electric field is shifted from the surface to the device interior (Cornu 1973, Adler and Temple 1976, 1978). The smaller is the negative angle, the higher is the achieved breakdown. Unfortunately, small angles lead to poor silicon area utilisation and high cost. The dielectric constant of the junction protective coating and various oxide charges can substantially modify the device breakdown voltage with any type of bevelling.

## 4.3. Depletion and substrate etching

Mechanical etching may be expensive; chemical etching is more acceptable. Temple and Adler (1976) increased junction breakdown voltage by chemically etching away (figure 22) some part of the highly doped region beyond the metal contact. This partial etching is applicable to both the plane and planar junctions and results, as in the negative bevelling, in the deeper penetration of the depletion region into the more heavily doped side of the junction. The results surpass those of negative bevelling but the method requires very accurate etch depth control.

Figure 22. Depletion etching of a plane junction (from Temple and Adler 1976).

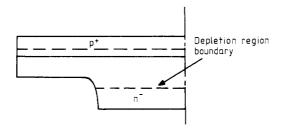

By etching away a portion of the lightly doped junction region (figure 23), it is possible to achieve high breakdown voltages—as high as with positive bevelling—both for the plane and planar junctions. This method is known as substrate etch termination (Temple and Adler 1977) and is less critical than the depletion etch method.

Figure 23. Substrate etch termination (from Temple and Adler 1977).

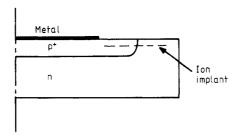

#### 4.4. Depletion region control by ion implantation

Shaping of the depletion region can be achieved by ion implantation (figure 24) (Temple 1977). This technique is applicable to the plane and planar junctions, and permits a much more precise charge control than the chemical etching. The achieved breakdowns have been close to 95% of the maximum possible.

Figure 24. Depletion region control by ion implantation (from Temple 1977).

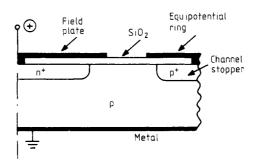

## 4.5. Field plates, guard rings and channel stoppers

Planar junction breakdown voltage is considerably increased by the use of a metal field plate (figure 25). The plate extends beyond the junction region and remains at the same potential as the n<sup>+</sup>-region. When reverse potential (positive for the n<sup>+</sup>-p junction) is applied, the p-region, under the plate edge and the oxide, becomes at least partially depleted of holes for oxides thicker than about 100 nm. With thinner oxides the surface easily inverts and becomes n-type. Surface depletion increases the resistivity of the p-region at the surface and hence the electric breakdown voltage.

Figure 25. pn junction with a metal field plate, metal guard ring and channel stopper.

Rusu and Bulucea (1979) and Rusu et al (1980) analysed the two-dimensional behaviour of the field plate and found that the breakdown voltage of a planar junction provided with a field plate may be represented by the same formula as given for the cylindrical planar junction (expression (3.4)) but with

$$\gamma = \gamma' = (\epsilon_{\rm S}/\epsilon_{\rm i})(x_{\rm i}/x_{\rm d}) \simeq 3x_{\rm i}/x_{\rm d}$$

(4.1)

where  $\epsilon_s$  and  $\epsilon_i$  are the permittivities of silicon and silicon dioxide, respectively, and  $x_i$  and  $x_d$  are the thicknesses of the oxide and the depletion region, respectively. Making the oxide thicker reduces the field crowding effect at the field plate edge and reduces the field more than an equal increment in the junction diffusion depth.

The field plate is usually used together (figure 25) with an equipotential ring surrounding the plate and electrically connected to the negatively biased substrate. The ring attracts holes nullifying the field plate's inverting effects, and conducts to ground the mobile positive charges accumulated on the oxide surface. The  $n^+$ -region under the ring improves the quality of the contact and also serves as an inversion layer (channel) stopper.

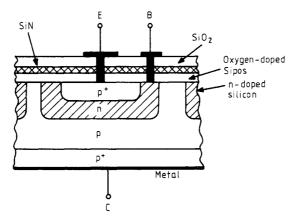

A very important variation of the field plate technique is the resistive plate formed by bridging the plate and the ring by a semi-insulating film such as semi-insulating oxygen-doped polycrystalline silicon (Sipos) (Matsushita et al 1976). The presence of the very slightly conducting film homogenises the electric field at the surface, avoiding field plate edge effects, improves the breakdown, suppresses arcing and stabilises (passivates) the surface. Figure 26 shows the Sipos film applied to a p<sup>+</sup>npp<sup>+</sup> transistor. The collector reverse bias is also applied to the oxygen-doped Sipos film so that the n-base region surface is able to support high breakdown voltage. The silicon nitride Si<sub>3</sub>N<sub>4</sub> film deposited on the top acts as a sealing agent against the penetration of moisture and highly mobile alkaline ions. The uppermost SiO<sub>2</sub> layer prevents the surface breakdown of the nitride layer.

Figure 26. Passivating resistive plate (Sipos) applied to a p-n-p transistor (from Matsushita et al 1976).

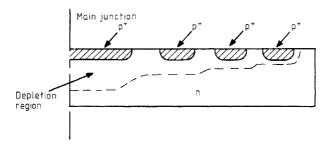

Another very useful technique for avalanche breakdown voltage improvement consists of surrounding the main junction by one or more diffused concentric rings (figure 27) (Kao and Wolley 1967). These field-limiting rings, electrically floating, are of the same semiconductor polarity as the highly doped side of the main junction. The spacing between the first ring and the main junction is small enough to permit the two depletion regions to touch each other before avalanche breakdown takes place. The field limiting rings play a double role: they act as voltage dividers and at the same time increase the radius of curvature of the main junction depletion region, thus improving the breakdown voltage capability.

Figure 27. p<sup>+</sup>n junction with p<sup>+</sup> field-limiting rings (from Kao and Wolley 1967).

## 5. Bipolar power transistor current gain

#### 5.1. Base widening

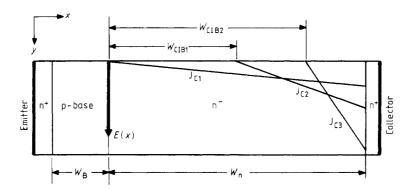

One of the serious limitations of bipolar transistors is the great dependence of their current gain on the current density. In the low-power devices, this dependence is mainly due to current conductivity modulation in the base which lowers the emitter efficiency (Webster 1954). In power devices, particularly those which are provided with  $n^-$ -collector drift regions, the current gain drops rapidly with the appearance of base widening (Kirk 1962). At high currents, in the  $n^+$ pn $^-$ n $^+$  transistor, the electron concentration in transit through the  $n^-$ -region becomes comparable to or larger than the  $n^-$ -region doping concentration. Assuming that the electrons in the collector depletion region reach the saturation velocity  $v_s$ , it is possible to write the Poisson equation in this region as

$$\frac{\mathrm{d}E}{\mathrm{d}x} = \frac{q}{\epsilon_{\mathrm{s}}} \left( N_{\mathrm{D}} - \frac{J_{\mathrm{C}}}{qv_{\mathrm{s}}} \right) \tag{5.1}$$

where  $N_D$  is the n<sup>-</sup>-region donor concentration and  $J_C$  is the collector current density. The solution of this equation is

$$E(x) = E(0) + \frac{q}{\epsilon_s} \left( N_D - \frac{J_C}{qv_s} \right) x. \tag{5.2}$$

E(0) is the field at x=0 at the base edge of the depletion region. The field distribution in the depletion region is, therefore, linearly dependent on the position x with a slope dependent on the current density. For  $J_C = qv_sN_D = J_0$  the slope is zero and the field is uniform. For greater currents (figure 28) (Whittier and Tremere 1969) the slope

Figure 28. Field distribution in the  $n^-$ -drift region of an  $n^+$ pn $^-$ n $^+$  transistor as a function of the collector current density (high-field case). The extended base  $W_{CIB}$  is wider for higher current densities (from Whittier and Tremere 1969).

changes its sign and the maximum field shifts away from the p-n<sup>-</sup> junction and eventually occurs at the n<sup>-</sup>-n<sup>+</sup> interface. Part or all of the n<sup>-</sup>-drift region becomes field-free, i.e. neutral, and can therefore be considered to be an extension of the neutral p-base. The current-induced base width  $W_{\rm CIB}$  has a maximum value equal to the drift region width  $W_{\rm n}$ . The case described above is known as high-field base widening.

When a power transistor operates as a switch, the collector junction voltage in the turn-on state becomes forward-biased, the depletion layer collapses and the device operates in saturation. As a result, the p-base starts injecting holes into the n<sup>-</sup> region (figure 29) which are neutralised by electrons coming from the n<sup>+</sup>-emitter and the n<sup>+</sup>-collector. Part or all of the n<sup>-</sup>-region becomes conductivity modulated and neutral, i.e. becomes an extension of the p-base (low-field base widening). The total effective

Figure 29. Mobile charge distribution in the n<sup>-</sup> collector drift region for the low-field case.

base width is therefore

$$W_{\text{eff}} = W_{\text{B}} + W_{\text{CIB}}.\tag{5.3}$$

Van der Ziel and Agourdis (1966) proposed a two-dimensional model for base widening, assuming that the emitter current spreads laterally in the base before reaching the collector region. A more complete base widening analysis would probably show that both effects might take place under some circumstances.

The widening of the base decreases the transistor transport factor  $\alpha_T$ , the emitter efficiency and lowers the frequency capability.

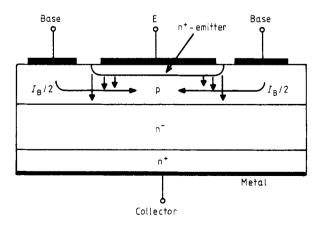

#### 5.2. Emitter crowding

The base current  $I_{\rm B}$  flowing laterally beneath the emitter (figure 30) causes a lateral voltage drop which makes the emitter centre less forward-biased than its edges so that the current crowds near the periphery with a density sufficient to cause the p-base to widen. Current crowding was analysed by Fletcher (1955) for a semi-infinitely long emitter and by Hauser (1964) for an emitter of finite length. A very simplified analysis

Figure 30. Current crowding at the emitter edges.

(Olmstead et al 1971) shows that the emitter current density along the emitter decays exponentially from the edge toward the centre with a characteristic length

$$y_0 = KW_{\rm B}h_{\rm FE}^{1/2} \tag{5.4}$$

where K is a constant. Here,  $y_0$  determines that part of the emitter which carries most of the current.

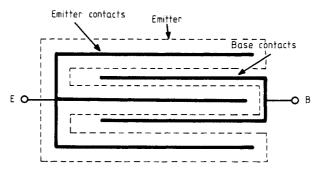

More recent analysis (Hower and Einthoven 1978) makes use of the integral charge control model (Gummel and Poon 1970) to take account of base widening effects in power transistors with n<sup>-</sup>-drift regions. All the analyses stress the need for narrow emitter fingers interlaced with the base metal contacts (figure 31) to minimise the current crowding which affects severely the current gain and may result in the device second breakdown (§ 9.2).

Figure 31. Schematic representation of the emitter and base interlacing.

## 5.3. Emitter efficiency

The emitter efficiency in the common-emitter configuration is given by expression (2.6). At high emitter impurity concentrations ( $N_D > 10^{18} \, \mathrm{cm}^{-3}$ ), the energy gap of silicon narrows (Mahan 1980) due to several effects such as impurity energy-level banding, random impurity distribution, free-carrier interaction, electron-donor interaction, etc. There is a wide disagreement about the most significant band-gap narrowing mechanism and about the amount of the change. A reasonable figure (Possin et al 1980) seems to be  $\Delta E_g = 100 \, \mathrm{meV}$  at the carrier concentration of  $5 \times 10^{19} \, \mathrm{cm}^{-3}$ . Band-gap narrowing results in an increased intrinsic carrier concentration, which at low concentrations is equal to  $n_i$ , but at high concentrations becomes

$$n_{\rm ie}^2 = n_{\rm i}^2 \exp{(\Delta E_{\rm g}/kT)}.$$

(5.5)

For silicon  $n_i^2 = 2 \times 10^{20} \text{ cm}^{-3}$ . The increase in the intrinsic carrier concentration changes the emitter charge per unit area to (Mertens *et al* 1973)

$$Q_{\rm E} = \int_0^{W_{\rm E}} N_{\rm D} (n_{\rm i}/n_{\rm ie})^2 \, \mathrm{d}x \tag{5.6}$$

where  $W_{\rm E}$  is the active emitter depth. Thus, the effective emitter charge becomes considerably smaller at higher carrier concentrations and leads to a lower emitter efficiency (expression (2.6)).

At large carrier concentrations the carrier diffusivities and mobilities are substantially reduced due to carrier-carrier scattering effects. At carrier concentrations n greater than about  $10^{18}$  cm<sup>-3</sup> the hole and electron diffusion constants become almost

equal and approximately follow the relationship (Howard and Johnson 1965)

$$D \propto n^{-1/2}.\tag{5.7}$$

This decreases the effective emitter width  $W_{\rm E}$  and lowers the emitter efficiency as well. High carrier concentration also leads to the reduction of the minority carrier lifetime and diffusion length. At concentrations above  $10^{17}\,{\rm cm}^{-3}$  the carrier recombination takes place both by the Shockley-Read-Hall (SRH) mechanism, involving recombination centres, as well as by Auger recombination. In Auger recombination, when a hole and an electron recombine the liberated energy is imparted to a third charge carrier—either a hole or an electron.

There is not complete agreement as to the relative importance of these various effects in determining the emitter efficiency (Sheng 1975, Adler *et al* 1976, McGrath and Navon 1977, Amantea 1980). There is a consensus, however, that the band-gap narrowing mainly affects shallow emitters  $1-3 \mu m$  deep, whose efficiencies drop for surface concentrations exceeding  $5 \times 10^{19}$  cm<sup>-3</sup>.

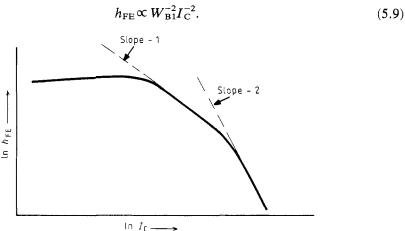

## 5.4. Current gain fall-off

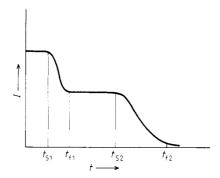

Collector current gain is plotted as a function of current in figure 32. The gain at first increases, reaches a plateau, then starts falling off with a slope equal to -1 since

$$h_{\rm FE} \propto W_{\rm B1}^{-2} I_{\rm C}^{-1}$$

(5.8)

where  $W_{\rm B1}$  is the total effective base width. Further increase in the current density results in severe current crowding and causes the gain to decrease more rapidly with a slope of -2 (Olmstead *et al* 1971, Hower and Einthoven 1978), since the gain then obeys the relationship

Figure 32. In  $h_{\rm FE}$  plotted against the ln of the collector current  $I_{\rm C}$ .

## 6. Methods of gain improvement

#### 6.1. Bipolar devices

One approach to improving bipolar device current gain is to use highly interlaced narrow emitter fingers. In microwave transistors, this approach is pushed to the limits

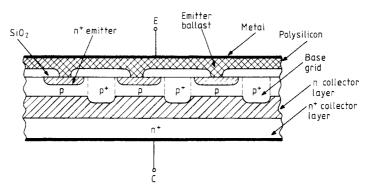

to ameliorate high-frequency current gain. One of the structures used for microwaves, the overlay transistor (Carley et al 1965), is depicted in figure 33. It uses a large number of discrete emitter sites paralleled by a thin overlayed metallisation. The p<sup>+</sup>-base regions carry the base currents. For uniform current distribution, each emitter site is provided with a ballasting resistor, consisting of resistive polycrystalline silicon. Optimum power output is obtained by maximising the ratio of emitter periphery to area, and also the ratio of emitter periphery to base area.

Figure 33. Overlay microwave power transistor with multiple emitters and ballasting resistors.

The emitter efficiency may be improved (Yagi et al 1974) by using an emitter consisting of a highly doped  $n^+$ -region and lightly doped  $n^-$ -region forming an  $n^+n^-pn^-n^+$  transistor. The holes injected by the p-base into the  $n^-$ -emitter cannot reach the emitter contact as they are reflected away from the  $n^+-n^-$  high-low barrier. This minimises the base-injected hole current and improves the emitter efficiency.

The use of arsenic in place of the more commonly used phosphorus gives steeper diffusion gradients and small band-gap narrowing (Fair 1973, Lillard *et al* 1973) leading to improved emitter efficiencies. Also avoided is so-called emitter push-out, which consists of pushing the base region ahead of the emitter diffusion. This is particularly troublesome for RF devices with narrow bases.

Excellent emitter efficiencies are possible by making the emitter from a semiconductor with a wider energy gap than that of the base. In such heterojunction structures the flow of the base current injected into the emitter is almost completely stopped and the emitter efficiency is unity. The realisation of such an emitter presents serious difficulties due to the presence of a large number of recombination centres at the interface of the two semiconductors. Recently Oh-uchi et al (1979) reported successful use of an oxygen- and phosphorus-doped polycrystalline layer (Sipos) as an emitter. According to Oh-uchi et al, highly phosphorus-doped Sipos has an energy gap of 1.5 eV, whereas that of silicon is 1.1 eV at room temperature.

A GaAs bipolar transistor with GaAlAs emitter (Bailbey et al 1980), developed for UHF applications, is another example of a heterojunction device capable of high current gains at very high current densities  $(3 \times 10^3 \text{A cm}^{-2})$ .

## 6.2. Field-effect transistors

The gain factor  $G_0$  largely determines the maximum allowable current, transconductance and power output of a field-effect transistor.

Large channel widths Z, small channel lengths L and thin gate oxides make  $G_0$  large. Channel widths in MOSFET devices operating at high currents may reach tens of cm. Typically the current per cm of channel width is of the order of  $0.5-1.0 \text{ A cm}^{-1}$ .

In contrast to bipolar transistors, no ballasting resistors are necessary to equalise the elementary cell gate currents because of the extremely high DC input resistances.

Channel lengths of the order of 3-5  $\mu$ m are required to obtain adequate transconductances and gain bandwidths. Shorter channel lengths are feasible, although some new effects, such as hot electron injection into the oxide, may, for instance, alter the threshold voltage and cause instabilities.

## 7. Voltage drop in power devices

All power devices should exhibit low power dissipation in order to keep their area and cost to a minimum. This leads to the requirement of low voltage drop in the device during switching and in the on state.

## 7.1. On-state voltage drop of bipolar transistors

When an  $n^+pn^+$  transistor is turned on, both the emitter and the collector are forward-biased, i.e. the device is in saturation (Ebers and Moll 1954) and exhibits minimum resistance to the current flow. In the  $n^+pn^-n^+$  transistors the voltage drop is higher because there is a quasi-saturation region, due to base widening. The voltage drop is the algebraic sum of the base-emitter voltage, the drop across the  $p^-n^-$  junction, the drop across the current-unmodulated region  $W_n - W_{CIB}$  (figure 29) and the drop in the extended base (Chudobiak 1970). In most cases the voltage in the unmodulated  $n^-$ -region dominates over other drops so that the total voltage drop is

$$V_{\text{CE(sat)}} \simeq J_{c} \rho_{c} (W_{n} - W_{\text{CIB}}) \tag{7.1}$$

where  $\rho_c$  is the n<sup>-</sup>-region resistivity. Using charge control equations, it is possible to more accurately compute the total voltage drop (Hower 1973, 1976) for devices with narrow emitter stripes.

#### 7.2. On resistance of MOSFET

The series device resistance in a MOSFET in the on condition is the sum of the active channel resistance and the drain structure resistances. The channel resistance, inversely proportional to the positive gate voltage, is small compared to the drain resistance. In the structure with a vertical drain the accumulation layer at the drain top surface (figure 18) distributes the current flow more uniformly and improves the drain region voltage drop. The series resistances of various MOSFET structures were computed by Sun and Plummer (1980).

## 7.3. Thyristor on-state voltage drop

In the forward conducting state all three SCR junctions are forward-biased and the total voltage drop is the algebraic sum of the voltage drops across the  $J_1$ ,  $J_2$  and  $J_3$  junctions and the voltage drops in all other regions of the  $n^+pn^-pn^+$  structure. For

simplicity, we can assume that the only significant voltage drop outside the three junctions is in the n-base which is usually very long in order to support the requisite anode potential. Consequently, the voltage drop across the thyristor is given by

$$V_{\rm T} = V_1 - V_2 + V_3 + V_{\rm n} \tag{7.2}$$

where  $V_n$  is the drop in the n-base. If we further assume that the device is symmetrical so that the thicknesses and doping levels of the two p-regions are the same, then expression (7.2) reduces to

$$V_{\rm T} = V_3 + V_{\rm n} \tag{7.3}$$

with

$$V_3 = \frac{kT}{q} \ln \left( \frac{I_A}{I_s} \right) \tag{7.4}$$

where  $I_s$  is the saturation current of the  $J_3$  junction. The voltage drop across the n-base region was studied by several authors (Herlet and Raithel 1966, Kokosa 1967, Otsuka 1967, Burtscher *et al* 1975, Adler 1978, Hayashi *et al* 1981). There are rather big discrepancies among the proposed voltage drop expressions. It is possible, however, to generalise the results by expressing the voltage drop in the n-base at high current densities as

$$V_{\rm p} = f(W_1/L)J^{1/2} \tag{7.5}$$

where  $f(W_1/L)$  is a sensitive function of the ratio of the n-base width  $W_1$  to the ambipolar carrier diffusion length L at high current densities. Long n-bases and short diffusion lengths rapidly increase the n-base voltage drop.

## 8. Dynamic behaviour of power devices

## 8.1. Gain-bandwidth product $(f_T)$

The gain-bandwidth product  $f_T$ , i.e. the frequency at which the common-emitter current gain drops to unity, largely determines the switching speed or the frequency response of a transistor. It is related to the total emitter-to-collector delay time  $\tau_{EC}$  by

$$f_{\rm T} = \frac{1}{2\pi\tau_{\rm TC}}.\tag{8.1}$$

$au_{\rm EC}$  is composed of the emitter and collector capacitance charging times, the base transit time and the collector depletion region transit time. At high current levels base widening causes the base transit time to greatly increase from the value of  $W_{\rm B}/2D_{\rm n}$  at low levels to

$$\tau_{\rm B} = \frac{W_{\rm B} + W_{\rm CIB}}{4D_{\rm n}}.\tag{8.2}$$

The factor of 4 in the denominator is due to the base current conductivity modulation effect which doubles the diffusion constant (Webster 1954).

In the MOSFET or JFET,  $f_T$  depends on the total electron transit time between the source and the drain. There is no channel widening effect. There exists, however, a

channel shortening effect due to the presence of the drain depletion region. This effect, primarily important for very short channels, decreases the transit time since in the space-charge region, the carriers move with the limiting velocity  $v_s \approx 10^7 \text{cm s}^{-1}$ .

## 8.2. Bipolar transistor switching

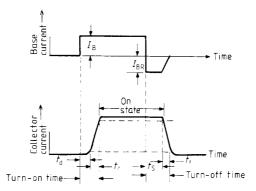

In bipolar transistors with resistive load, the switching transient can be described by the *idealised* waveforms of figure 34. The upper waveform depicts the base turn-on and turn-off current pulses. The lower waveform represents the resulting (output) collector current. The idealised waveforms are mainly helpful in understanding the manufacturers' data regarding various collector current time delays.

Figure 34. Bipolar power transistor switching transient  $t_d$ ,  $t_r$ ,  $t_s$  and  $t_f$  are the delay time, rise time, storage time and fall time, respectively.

In order to turn the transistor on, a current  $I_{\rm B}$  is applied to the base. The collector current starts appreciably flowing only after a delay time  $t_{\rm d}$ . This amount of time is necessary to charge the emitter and the collector junction transition capacitances and to allow the emitted minority carriers to reach the collector. This time interval ends by convention when the collector current reaches 10% of its final value. The rise time  $t_{\rm r}$  is the time necessary for the collector current to reach 90% of the final value. The total turn-on time is the sum of  $t_{\rm d}$  and  $t_{\rm r}$ .

In order to turn the transistor off, a reverse current  $I_{\rm BR}$  is applied to the base. Because of electric charges stored in various transistor regions, the collector current continues flowing unchanged for a time  $t_{\rm S}$ . Upon the removal of most of these charges, the collector current starts falling off and becomes equal to 10% of the maximum collector current after a time interval  $t_{\rm f}$  known as fall-off time. The total turn-off time is the sum of  $t_{\rm S}$  and  $t_{\rm f}$ . All of these various time intervals can be calculated comparatively easily (Moll 1954) for small-signal transistors, using the linear differential equations of the charge-control analysis. This type of transistor analysis ties the base and the emitter currents to the base charge. For power transistors, particularly those with n high-resistivity regions, the problem becomes much more complex because the transistor current gain, due to the base widening effect, changes much more drastically with current level than in small-signal devices. This makes the charge-control equations non-linear so that the simplicity of the solution of linear equations is lost. To overcome these difficulties, the collector current rise time of a power transistor can be divided into two time intervals (Hower 1976): the initial one with

the device operating in the active region of the I-V characteristics, and another one when the transistor reaches deep saturation, i.e. the collector becomes heavily forward-biased, starts emitting electrons (a  $n^+pn^-n^+$  transistor is considered here) and the transistor p-base widens. In this approach, the collector rise time is described by two linear differential equations which can be easily solved. The analysis shows that, prior to the base widening, when the device is in the active region, the collector current rises with the time constant

$$\tau_1 = h_{\text{FEO}} \tau_{\text{B1}} \tag{8.3}$$

where  $h_{\text{FEO}}$  is the peak value of the common-emitter current gain and  $\tau_{\text{b1}}$  is the minority-carrier transit time in the device's metallurgical base. During the first time interval, the collector current can be expressed by

$$I_{C1}(t) = h_{FEO}I_{B}[1 - \exp(-t/\tau_{1})]$$

(8.4)

where  $I_{\rm B}$  is the turn-on base current and t denotes time. As the current further increases beyond some critical value, the base starts widening and the current-induced base width during the rise time varies from zero to its maximum possible value  $W_{\rm CIB}$ . Neglecting the comparatively small width of the metallurgical base, it is possible to introduce an effective transit time  $\tau_{\rm B2}$  for the minority carriers traversing the current-induced base. This effective transit time is obviously shorter than the transit time through the fully current-induced base width  $W_{\rm CIB}$ .

In the second region, the current rise can be expressed by

$$I_{C2}(t) = h_{FE}I_{B}\{1 - \exp\left[-(t + t_{a})/\tau_{B2}\right]\}.$$

(8.5)

In this expression,  $h_{\rm FE}$  is the DC current gain at high current levels with the base fully widened and  $t_{\rm a}$  is a factor introduced to ensure the continuity of transition from the first to the second time interval.

Equations (8.4) and (8.5) permit the calculation of the total time necessary for the collector current to rise from 10% to 90% of its final value.

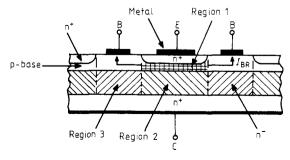

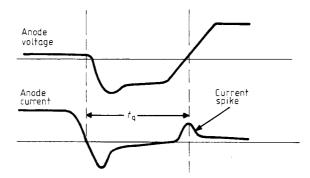

The turn-off transient of an  $n^+pn^-n^+$  power transistor, because of its complexity, has not been fully studied from the physical point of view and the existing numerical modelling techniques are not satisfactory from the device design point of view. To turn-off an  $n^+pn^-n^+$  transistor from the conducting state, i.e. from deep saturation, it is necessary to remove all the charges in excess of the equilibrium charges stored in the various device regions (figure 35). This can be accomplished, for example, by the application of a reverse base current pulse  $I_{BR}$ . The problem of charge removal

Figure 35. Three transistor regions with stored charges (from Hower 1980).

is two-dimensional and is further complicated by the appearance of a lateral voltage drop in the base caused by  $I_{\rm BR}$ . Due to this effect, the emitter current concentrates in the emitter and base central regions. The charge withdrawal time is thus further increased. During the turn off (Hower 1980), the charge is first removed from region 3 ('remote' base), the closest to the base metal contact. After that, the charge is removed from region 2, i.e. from the current-induced base, and finally from the metallurgical base (region 1). In the most recent, but still rather incomplete model of Hower (1980), the charge moves toward the base metal contact with a lateral velocity  $v_{\rm L}(t)$ . Since the base current is the product of the net excess charge its velocity  $v_{\rm L}(t)$  increases as the charge decreases with the lapse of time in order to keep the reverse base current constant.