ABSTRACT

Title of dissertation: PHYSICAL ASPECTS OF VLSI DESIGN

WITH A FOCUS ON THREE-DIMENSIONAL INTEGRATED CIRCUIT APPLICATIONS

Zeynep Dilli

Doctor of Philosophy, 2007

Dissertation directed by: Professor Neil Goldsman

Dept. of Electrical and Computer Engineering

This work is on three-dimensional integration (3DI), and physical problems and aspects of VLSI design. Miniaturization and highly complex integrated systems in microelectronics have led to the 3DI development as a promising technological approach. 3DI offers numerous advantages: Size, power consumption, hybrid integration etc., with more thermal problems and physical complexity as trade-offs. We open this work by presenting the design and testing of an example 3DI system, to our knowledge the first self-powering system in a three-dimensional SOI technology. The system uses ambient optical energy harvested by a photodiode array and stored in an integrated capacitor.

An on-chip metal interconnect network, beyond its designed role, behaves as a parasitic load vulnerable to electromagnetic coupling. We have developed a spatially-dependent, transient Green's Function based method of calculating the response of an interconnect network to noise. This efficient method can model network delays and noise sensitivity, which are involved problems in both planar

and especially in 3DICs.

Three-dimensional systems are more susceptible to thermal problems, which also affect VLSI with high power densities, of complex systems and under extreme temperatures. We analytically and experimentally investigate thermal effects in ICs. We study the effects of non-uniform, non-isotropic thermal conductivity of the typically complex IC material system, with a simulator we developed including this complexity. Through our simulations, verified by experiments, we propose a method of cooling or directionally heating IC regions.

3DICs are suited for developing wireless sensor networks, commonly referred to as "smart dust." The ideal smart dust node includes RF communication circuits with on-chip passive components. We present an experimental study of on-chip inductors and transformers as integrated passives. We also demonstrate the performance improvement in 3DI with its lower capacitive loads.

3DI technology is just one example of the intense development in today's electronics, which maintains the need for educational methods to assist student recruitment into technology, to prepare students for a demanding technological landscape, and to raise societal awareness of technology. We conclude this work by presenting three electrical engineering curricula we designed and implemented, targeting these needs among others.

# PHYSICAL ASPECTS OF VLSI DESIGN WITH A FOCUS ON THREE-DIMENSIONAL INTEGRATED CIRCUIT APPLICATIONS

by

#### Zeynep Dilli

Dissertation submitted to the Faculty of the Graduate School of the University of Maryland, College Park in partial fulfillment of the requirements for the degree of Doctor of Philosophy

2007

Advisory Committee:

Professor Neil Goldsman, Chair/Advisor

Professor Martin Peckerar

Associate Professor Reza Ghodssi

Associate Professor Timothy Horiuchi

Associate Professor Linda Schmidt

© Copyright by Zeynep Dilli 2007

## Dedication

To all my teachers

#### Acknowledgements

First and foremost I am indebted to Dr. Neil Goldsman for his invaluable support and guidance. He has been a great advisor and teacher.

I am grateful to Dr. Martin Peckerar and Dr. Linda Schmidt for the privilege to work with them on different sections of this dissertation, and for joining my committee. I am grateful to Dr. Reza Ghodssi and Dr. Timothy Horiuchi for agreeing to serve in my committee, and for their time and effort.

I have been lucky to collaborate with brilliant and supportive people. I must mention Dr. Akın Aktürk especially. I also owe thanks to Dr. Janet Schmidt, Mr. Todd Firestone, Ms. Datta Sheth, Ms. Bo Yang, Mr. Yves Ngu and Mr. Bai Yun for their assistance and collaboration, for Mr. Jay Renner and Mr. Shyam Mehrotra for technical support, and to Dr. Volkan Cevher, Mr. Susitha Jayaratne, Dr. Gary Pennington, Mr. Siddharth Potbhare and Dr. John Rodgers for very profitable discussions. Through the years I have had many inspiring teachers, and while I cannot name them all, I thank them all.

I would like to thank Dr. George Metze at LPS and the Dept. of Electrical and Computer Engineering for supporting the majority of this work.

My thanks and gratitude go to my mother Yıldız for teaching me how to read resistors (and for much more), to my father Budak for teaching me how to analyze filters at a glance (and for much more), and to my sister Gökçe for being the ray of sunshine she is (and for much more). I give thanks to all my extended family for their support and love. Size gerektiği kadar teşekkür edemem hiç.

Many precious people have supported me and offered their confidence, counsel, experience and friendship during this work. Dr. Breno Imbiriba, Dr. Hilmi Volkan Demir, Mrs. Paula and Mr. Chort Montrie, Dr. Kristy Henscheid, Dr. Jeff Huo, Mrs. Maggie Brazeau, Mr. John Novak, Mrs. Loreen and Mr. Martijn de Kort, Mrs. Frederica and Mr. Herb Baer, all those who attend the Conservatory and members of Three Left Feet, all the newsgroup people, more others than I can name and once again my family—I hope I have been and will be able to give back some of all that I received from you.

### Table of Contents

| Li | st of 1 | Figures  |                                                                 | X               |

|----|---------|----------|-----------------------------------------------------------------|-----------------|

| 1  | Intro   | oductio  | n                                                               | 1               |

|    | 1.1     | Three    | -Dimensional Integration and Self-Powering: Motivation and      |                 |

|    |         |          | s of VLSI Physics                                               | 2               |

|    | 1.2     |          | in the Physics of VLSI Design: Interconnect Modeling            | 6               |

|    | 1.3     |          | in the Physics of VLSI Design: Thermal Effects and Modeling .   | 9               |

|    | 1.4     |          | in the Physics of VLSI Design: Reactive Components              | 12              |

|    | 1.5     | Electr   | ical Engineering Education: Motivation                          | 14              |

| 2  | Thre    | ee-Dime  | ensional Integration: Physical Design of A Self-Contained Elec- |                 |

|    | tron    | ic Syste |                                                                 | 16              |

|    | 2.1     | Introd   | luction and Overview                                            | 16              |

|    | 2.2     | Exam     | ple Implementation: A Self-Powering 3-D System on SOI CMOS      | 17              |

|    |         | 2.2.1    | Design Introduction                                             | 17              |

|    |         | 2.2.2    | Process Information                                             | 19              |

|    |         | 2.2.3    | Photodiodes: Design Issues                                      | 22              |

|    |         |          | 2.2.3.1 Photocurrent Calculation                                | 22              |

|    |         | 0.0.4    | 2.2.3.2 Photodiode Design and Layout                            | 28              |

|    |         | 2.2.4    | Layout and Chip Microphotographs                                | 34              |

|    |         |          | 2.2.4.1 Tier 1: The Local Oscillator                            | 34              |

|    |         |          | 2.2.4.2 Tier 2: The Capacitor                                   | $\frac{35}{26}$ |

|    |         |          | <i>'</i>                                                        | $\frac{36}{37}$ |

|    |         | 2.2.5    | 2.2.4.4 Chip Microphotographs                                   | 37<br>40        |

|    |         | 2.2.0    | 2.2.5.1 Circuit Operation: Qualitative Description              | 40              |

|    |         |          | 2.2.5.1 Circuit Operation: Quantitative Description             | 45              |

|    |         | 2.2.6    | Measurement Results                                             | 49              |

|    |         | 2.2.0    | 2.2.6.1 Rail Voltage Measurements                               | 49              |

|    |         |          | 2.2.6.2 Oscillator Output Measurements                          | 49              |

|    |         | 2.2.7    | Concluding Remarks on the First Self-Powering SOI 3DIC          | 50              |

|    | 2.3     |          |                                                                 | 51              |

|    |         | 2.3.1    | Introduction                                                    |                 |

|    |         | 2.3.2    | Overview of of the Second-Generation Chip                       | 52              |

|    |         | 2.3.3    | New Diode Arrays                                                | 53              |

|    |         |          | 2.3.3.1 Diode Layouts with No-Silicide                          | 54              |

|    |         |          | 2.3.3.2 Diode Array with Two Serial Diodes per Branch           | 55              |

|    |         | 2.3.4    | Integrated Externally-Powered Amplifier                         | 57              |

|    |         | 2.3.5    | Self-Powered Amplifier                                          | 59              |

|    | 2.4     | 3-D Ir   | ntegration: Current Research, Challenges and Directions         | 62              |

|    |         | 2.4.1    | Sequential Fabrication Techniques for 3DI                       | 63              |

|    |         | 2.4.2    | Parallel Fabrication Techniques for 3DI                         | 64              |

|   |      |          | 2.4.2.1    | Chip Stacks with Peripheral Connections               | 64  |

|---|------|----------|------------|-------------------------------------------------------|-----|

|   |      |          | 2.4.2.2    | Chip Stacks with Through-Wafer and Through-Die        |     |

|   |      |          |            | Connections                                           | 66  |

|   |      |          | 2.4.2.3    | Alternate Vertical Connection Methods                 | 68  |

|   |      | 2.4.3    |            | lysis of State-of-the-Art in the Advantages and Prob- |     |

|   |      |          | lems of 3  | 3-D Integration                                       | 69  |

|   |      |          | 2.4.3.1    | Gains in System Size                                  | 69  |

|   |      |          | 2.4.3.2    | Enabling Higher System Complexity                     | 70  |

|   |      |          | 2.4.3.3    | Gains in System Speed and Power Consumption           | 71  |

|   |      |          | 2.4.3.4    | Noise and Crosstalk Problems and Proposed Solutions   | 72  |

|   |      |          | 2.4.3.5    | Thermal Problems and Proposed Solutions               | 73  |

|   |      |          | 2.4.3.6    | Layout Issues                                         | 74  |

|   |      |          | 2.4.3.7    | New Process Requirements                              | 74  |

|   | 2.5  | Recent   | t Progress | s in Self-Powering Methods                            | 75  |

|   |      | 2.5.1    | Photoele   | ectric Methods                                        | 76  |

|   |      | 2.5.2    | Piezoele   | ctric, Vibrational and Thermoelectric Methods         | 76  |

|   |      | 2.5.3    | Rectifyin  | ng Antennas                                           | 77  |

|   |      | 2.5.4    | Small B    | atteries                                              | 80  |

|   | 2.6  | Summ     | ary        |                                                       | 80  |

| 3 | Phys | sical As | pects of V | LSI Systems: A Transient Spatially-Dependent Green's  |     |

|   |      |          | -          | o Modeling 3-D On-Chip Interconnect Networks          | 82  |

|   | 3.1  | -        |            | -                                                     | 82  |

|   |      | 3.1.1    |            | ology: Linear Time-Invariant Systems and Green's      |     |

|   |      |          |            | 1                                                     | 83  |

|   | 3.2  | Numer    | rical Mod  | eling                                                 | 85  |

|   |      | 3.2.1    |            |                                                       | 85  |

|   |      |          | 3.2.1.1    |                                                       | 87  |

|   |      | 3.2.2    | Comput     |                                                       | 90  |

|   | 3.3  | Impler   | nentation  |                                                       | 91  |

|   |      | 3.3.1    | Intercon   | nect Network Construction                             | 91  |

|   |      | 3.3.2    | Impulse-   | Response Solver                                       | 94  |

|   |      |          | 3.3.2.1    | KCL Network, Equations and Discretization             | 94  |

|   |      | 3.3.3    | Convolu    | tion Routine                                          | 96  |

|   | 3.4  | Simula   | ation Res  | ults                                                  | 97  |

|   |      | 3.4.1    | Compar     | ison with SPECTRE                                     | 97  |

|   |      |          | 3.4.1.1    | Convergence Test                                      |     |

|   |      | 3.4.2    | Example    | e 3D Network Simulations                              |     |

|   | 3.5  | Summ     | ary        |                                                       | 106 |

| 4 | Phys | sical As | spects of  | VLSI Systems: On-Chip Heat Generation and Dissipa-    |     |

| _ | tion |          | r          | v                                                     | 107 |

|   | 4.1  | Introd   | uction an  | d Motivation                                          |     |

|   | 4.2  |          |            |                                                       |     |

|   | _    | _        |            |                                                       | 109 |

|   |      | 4.2.2    | A Simplified Solver and the Effects of Non-Isotropic Thermal  |       |

|---|------|----------|---------------------------------------------------------------|-------|

|   |      |          | Conductivity                                                  | . 111 |

|   |      | 4.2.3    | A Thermal Solver with Individual IC Layers Represented        | . 117 |

|   | 4.3  | Exper    | imental Design                                                |       |

|   |      | 4.3.1    | Heaters                                                       | . 120 |

|   |      | 4.3.2    | The Temperature Sensor Array                                  | . 121 |

|   |      |          | 4.3.2.1 Temperature Dependence of the Diode Current           |       |

|   |      |          | 4.3.2.2 Diode Array for Distributed Temperature Sensing.      |       |

|   |      | 4.3.3    | Ring Oscillators as Temperature Sensors and Heat Sources .    |       |

|   |      | 4.3.4    | The Metal Layers                                              |       |

|   | 4.4  | Measu    | rements of Temperature Distribution in Integrated Circuits .  |       |

|   |      | 4.4.1    | Experimental Setup                                            |       |

|   |      | 4.4.2    | Parasitic Effects                                             |       |

|   |      | 4.4.3    | Measurement Results                                           |       |

|   | 4.5  |          | ations: Controlled Heating and Cooling on ICs                 |       |

|   | 1.0  | 4.5.1    | Simulator Validation                                          |       |

|   |      | 4.5.2    |                                                               |       |

|   |      |          | Effects in SOI Technologies                                   |       |

|   | 4.6  |          | nary                                                          |       |

|   | 1.0  | Summ     | ion y                                                         | . 111 |

| 5 | Phys | sical As | spects of VLSI Systems: Reactive Structure Design and Parasit | ic    |

|   |      |          | Load Effects in Integrated Circuits                           | 149   |

|   | 5.1  |          | luction, Motivation and Background                            |       |

|   | 5.2  |          | s of On-Chip Inductors and Transformers                       |       |

|   |      | 5.2.1    | The Concept of Inductance                                     |       |

|   |      | 5.2.2    | Physical Design                                               |       |

|   |      | 5.2.3    | On-chip Inductor Behavior and Design Guidelines               |       |

|   | 5.3  |          | imental Design and Measurement Results                        |       |

|   | 0.0  | 5.3.1    | <u> </u>                                                      |       |

|   |      | 0.0      | 5.3.1.1 De-Embedding                                          |       |

|   |      | 5.3.2    | Inductor Measurements                                         |       |

|   |      | 5.3.3    |                                                               |       |

|   | 5.4  |          | ole LC Tanks: Photoelectric Effect                            |       |

|   | 0.1  | 5.4.1    | Experimental Results                                          |       |

|   |      | 5.4.2    | Interpretation and Modeling                                   |       |

|   | 5.5  |          | uding Remarks on On-Chip Inductors                            |       |

|   | 5.6  |          | dy of Performance Improvement by Capacitive Load Reduction    |       |

|   | 0.0  |          | BD Integration                                                | 175   |

|   |      | 5.6.1    | System Design                                                 |       |

|   |      | 5.0.1    | 5.6.1.1 Measuring Bonding Pad Effects Using Ring Oscillator   |       |

|   |      |          | 5.6.1.2 Internal and External Ring Oscillators                |       |

|   |      | 5.6.2    | Measurement Results                                           |       |

|   | 5.7  |          | nary                                                          |       |

|   | 0.1  | vuiii.   | 1001 7                                                        | . IU. |

| 6   | Lool   | king to the Future: Improving Electrical Engineering Education        | 184 |

|-----|--------|-----------------------------------------------------------------------|-----|

|     | 6.1    | Introduction, Motivation and Background                               | 184 |

|     | 6.2    | An Experiential Introduction to Electrical and Computer Engineer-     |     |

|     |        | ing: A Summer Course for High-School Students                         | 185 |

|     |        | 6.2.1 Introduction and Program Goals                                  | 185 |

|     |        | 6.2.2 The Syllabus and the Textbook                                   | 188 |

|     |        | 6.2.2.1 The Textbook                                                  | 189 |

|     |        | 6.2.3 Implementation                                                  | 191 |

|     |        | 6.2.4 Program Outcomes                                                | 192 |

|     |        | 6.2.5 Conclusion                                                      | 196 |

|     | 6.3    | Aiding the Mentors: A Short Course for High-School Maths Teachers     | 196 |

|     |        | 6.3.1 Introduction and Motivation                                     | 196 |

|     |        | 6.3.2 Implementation                                                  | 197 |

|     |        | 6.3.3 Conclusion                                                      | 200 |

|     | 6.4    | Multi-Track Capstone Design: A Senior-Year Course                     | 202 |

|     |        | 6.4.1 Introduction, Motivation and Course Goals                       | 202 |

|     |        | 6.4.2 Implementation                                                  | 204 |

|     |        | 6.4.3 Outcomes                                                        | 205 |

|     | 6.5    | Summary                                                               | 207 |

| 7   | Sum    | mary and Future Research                                              | 209 |

|     | 7.1    | Three-Dimensional Integration                                         | 209 |

|     | 7.2    | Interconnect Network Modeling                                         |     |

|     | 7.3    | Thermal Modeling                                                      |     |

|     | 7.4    | Reactive Structures and Load Effects in ICs                           |     |

|     | 7.5    | Electrical and Computer Engineering Education                         | 215 |

| A   | Tem    | perature Dependence of Diffusion Constants and Diffusion Lengths      | 217 |

| В   | Tem    | perature Dependency of MOSFET Current in Saturation                   | 219 |

| С   | Exai   | mple Lab Template Excerpts from "An Experiental Introduction to Elec- |     |

|     |        | and Computer Engineering"                                             | 222 |

| Bil | oliogr | raphy                                                                 | 224 |

# List of Figures

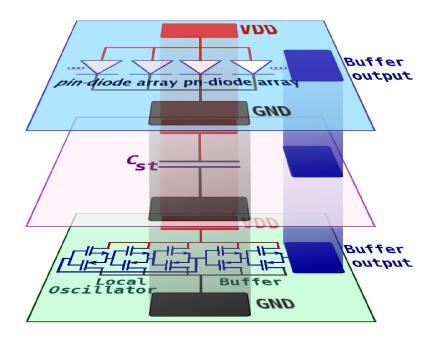

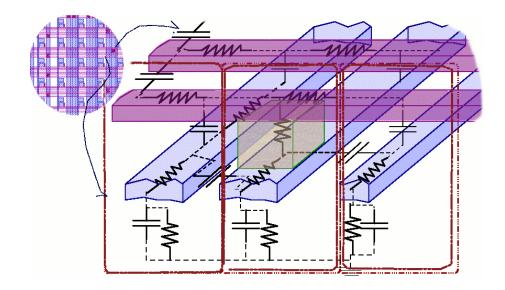

| 2.1 | Three tiers in a conceptual 3-D system design: The sensor (top), storage (middle) and functional electronics (bottom) levels. The components in our specific design are also shown here.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

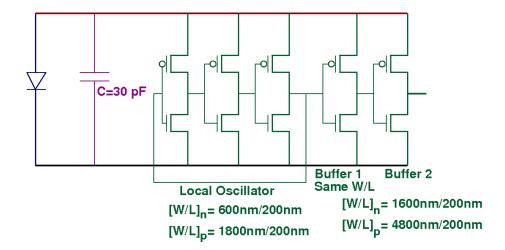

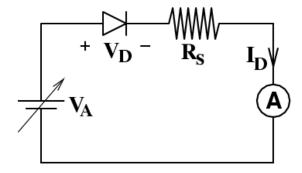

| 2.2 | The particular circuit being fabricated in our 3-D design. The photodiode symbolizes a diode array comprised of many diodes in parallel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

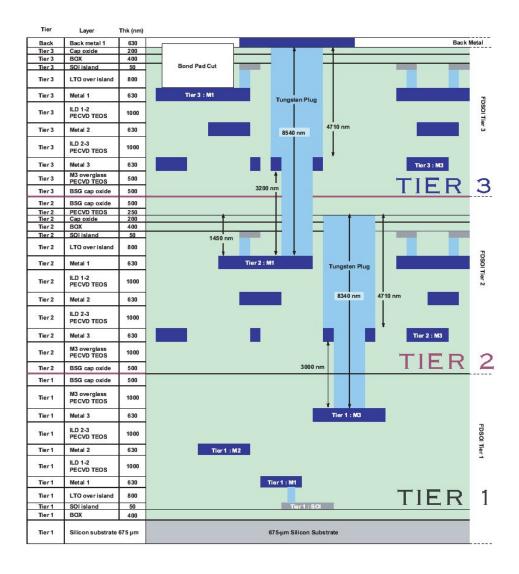

| 2.3 | The full integration structure for the 3DL1 process. In our design, the photodiodes will be built in the active regions of the top tier, Tier 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 21 |

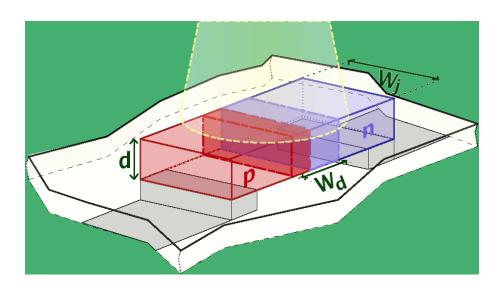

| 2.4 | The schematic representation of a pn-junction diode fabricated in this SOI process and of the photosensitive area to be taken into account. Since the diode tier is integrated into the 3DIC upside-down with respect to its fabrication orientation, the metal connections to the anode and cathode of the diode are shown as going "downwards". In this case, the effective photosensitive area is $A = W_d W_j$ , and the light passes through the active silicon depth $d$ for a single pass. In this picture, the following are not shown for clarity: The oxide layers surrounding the active silicon layer which houses the diode, and the polysilicon layer covering the junction, which is between the metal layers and the active layer in the process                                                                                                                                                                                                                                                                                                                             | 24 |

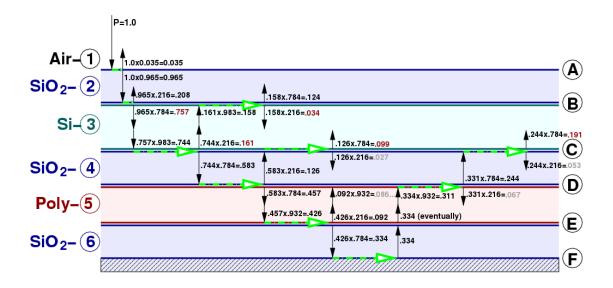

| 2.5 | The multiple reflections in our multi-layer thin film system. The layer thicknesses are not shown to scale. The transmission layers are numbered 1 through 6 and interfaces named A through F. Below the $SiO_2$ layer 6 a metal layer is shown, with $100\%$ reflection assumed at that interface. Every time an incident ray hits an interface, a green arrow points at it splitting into transmitted and reflected components. With the incident power level set at 1.0, the fractional numbers show the percentage reflected or transmitted at each interface. The numbers shown in red are thus power levels entering and re-entering the active silicon layer. When the power level in a particular ray trace falls below 0.1 (i.e. $10\%$ ), that number is given in gray and that particular ray is not traced any further. Note that through multiple reflections layer number 6, eventually all of the power entering layer 6 from layer 5, $33.4\%$ of the incident power, will be reflected back into layer 5; all the back and forth of that process is not shown in the figure | 27 |

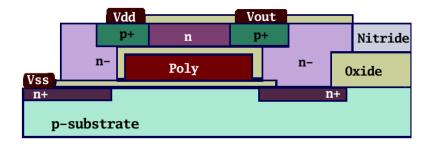

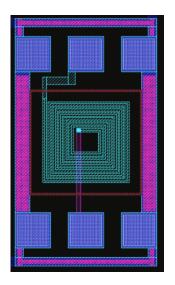

| 2.6 | Implants for the pin-type diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30 |

| 2.7 | Implants plus poly for the pin-type diode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 30 |

| 2.8  | The full layout for the pin-type diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 30 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

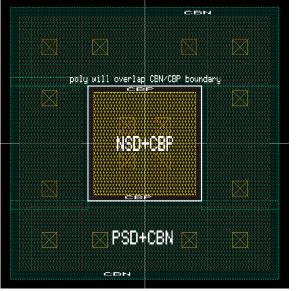

| 2.9  | Implants for the CBN/CBP diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33 |

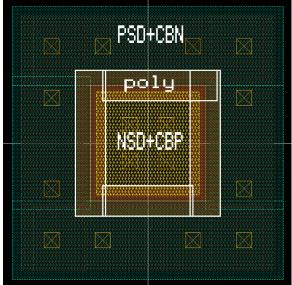

| 2.10 | Implants plus poly for the CBN/CBP diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33 |

| 2.11 | The full layout for the CBN/CBP diode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33 |

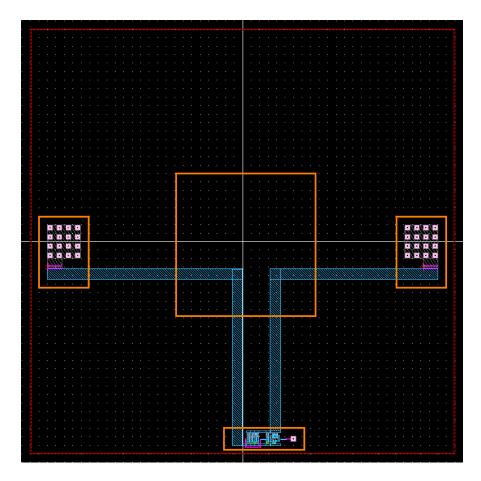

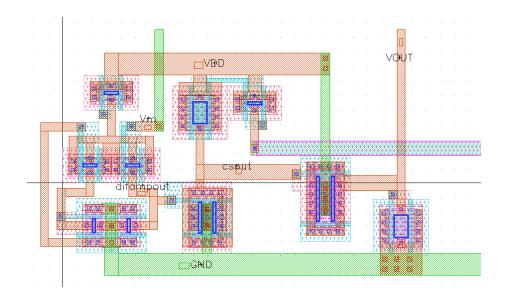

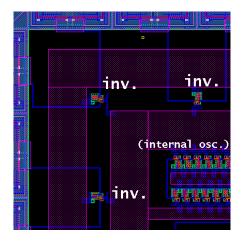

| 2.12 | Local oscillator (Tier 1—bottom tier) layout. To the left and right are the 3-D vias coming from the higher tiers, for GND and VDD rails respectively                                                                                                                                                                                                                                                                                                                                                                                                                  | 34 |

| 2.13 | A zoom of the local oscillator, output buffers and the 3D via carrying the output signal up                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34 |

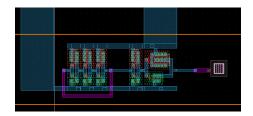

| 2.14 | The capacitor tier (Tier 2—middle tier) layout. The capacitor top plate is a poly square, 67.9 $\mu$ m on one side. The bottom plate is produced using the CAPN n-type implant. The expected capacitance of this structure is 30 pF and the Cadence-extracted capacitance is 29 pF                                                                                                                                                                                                                                                                                     | 35 |

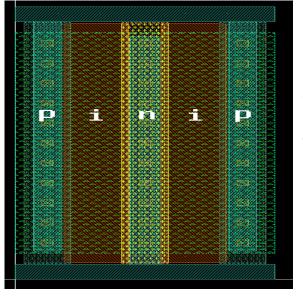

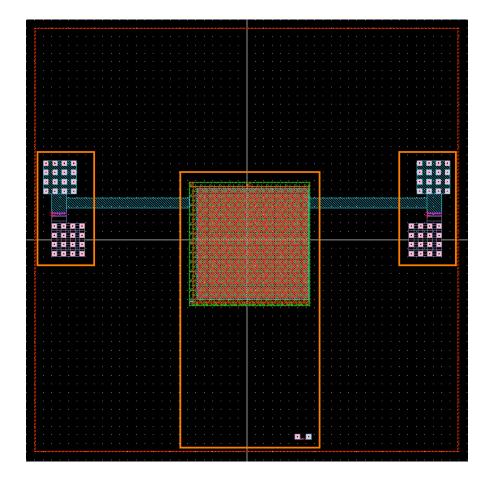

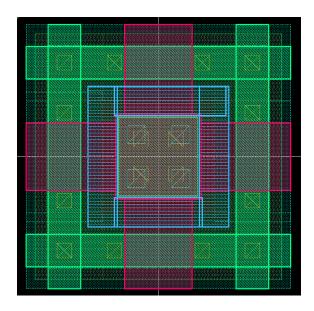

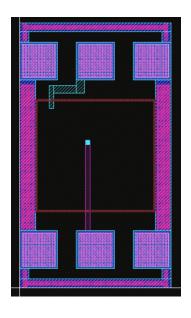

| 2.15 | The diode tier (Tier 3—top tier) layout. The bondpads have overglass cuts to allow access to the Metal 1 layer of the tier with probes or bondwires. Most of the tier is covered by the array of 2062 annular CBN/CBP diodes, and there are also 52 lateral "pin" diodes near the top of the layout. All features are identified in the chip microphotograph, Figure 2.16. The layout is a square 250 $\mu \rm m$ to a side.                                                                                                                                           | 36 |

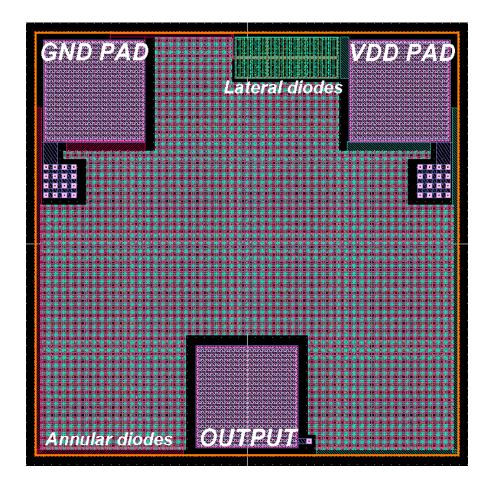

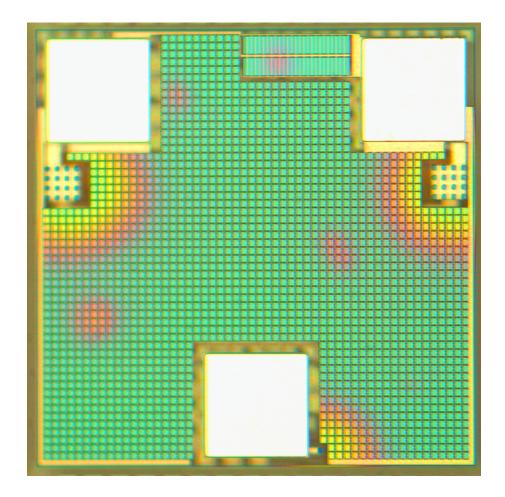

| 2.16 | The fabricated 3DIC microphotograph. The top tier is visible. Top right: VDD pad. Top left: GND pad. Bottom middle: The oscillator output pad. The pin-diode array is next to the VDD pad. The rest of the tier is covered by the annular pn-diode array. The intertier (3-D) via arrays to the lower tiers from the VDD and GND pads are below the pads; the intertier via from the lower tier to the output pad is to its right side. Lower tiers are somewhat visible, though out of focus, at the bonding pad edges, where there are no top tier features defined. | 37 |

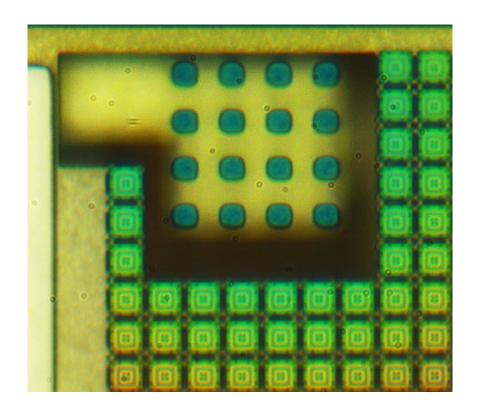

| 2.17 | A close-up of the intertier via landing next to the GND pad and the corner of the surrounding annular pn-diode array. The four dark squares at the center of the each diode are the stacked contacts and vias from the n-active region to metal-1 and metal-2. The eight squares on the sides of each diode are contacts from the p-active region to metal-1. The polysilicon square covering the junction for silicide protection is also visible in each diode                                                                                                       | 38 |

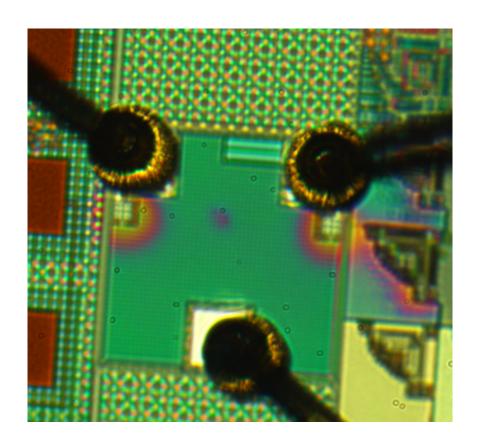

| 2.18 | A close-up of the bonded die. Surrounding our design are test structures from the process.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 39 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

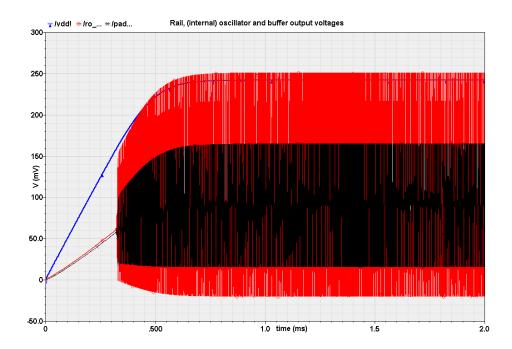

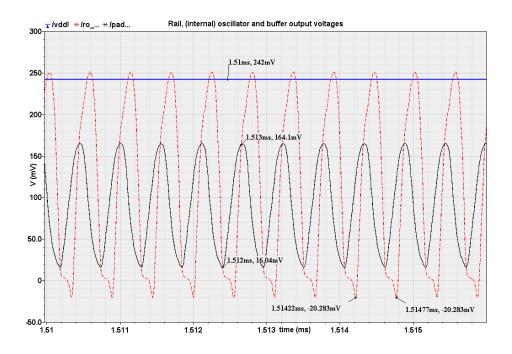

| 2.19 | System operation with $i_p = 15$ nA. The voltage scale is between - 50 mV and 300 mV, and the blue line rising faster in the beginning is the rail voltage, which reaches a steady state of 242 mV in this simulation. The lighter solid line is the ring oscillator output feeding the buffer and the thick solid line is the buffer output to a 15 fF load (bonding pad only)                                                                                                                                                     | 41 |

| 2.20 | Zoom in on the full oscillation region of the simulation in Figure 2.19. The oscillation frequency in this case is $\sim 1.82$ MHz                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |

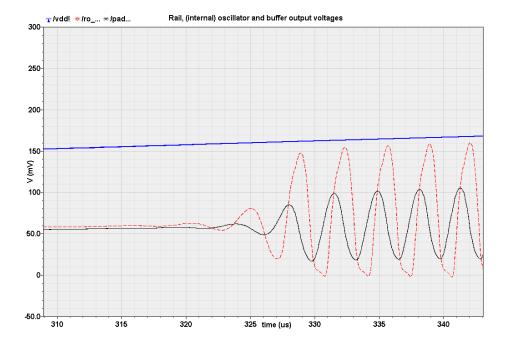

| 2.21 | Zoom in to Figure 2.19 around the region where oscillation is beginning. $$                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42 |

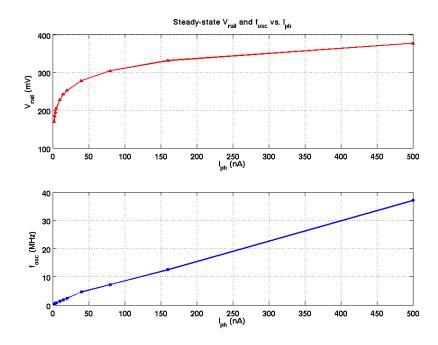

| 2.22 | Simulated steady-state rail voltages (top) and oscillation frequencies (bottom) vs. photocurrent                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43 |

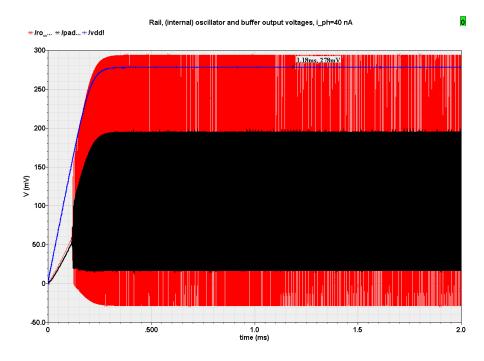

| 2.23 | System operation with $i_p=40$ nA and storage capacitor 30 pF                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 43 |

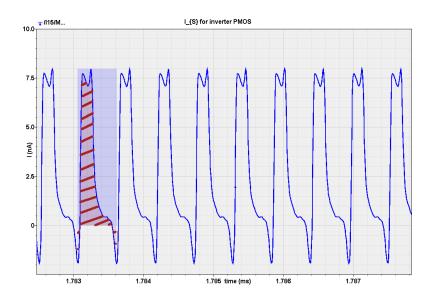

| 2.24 | The PMOS source current of the fourth inverter (first buffer stage) during full oscillation. The ratio of the cross-hatched area to the highlighted area gives $\Phi_4$ , which is interpreted as the effective duty cycle                                                                                                                                                                                                                                                                                                          | 47 |

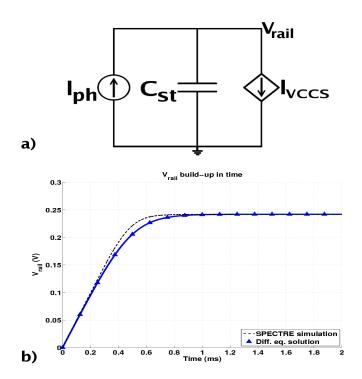

| 2.25 | a) Simplified equivalent circuit to demonstrate the system operation. b) The rail voltage of the circuit builds up in time to reach a steady state as the current drawn by the inverters from the storage capacitor, rising with increasing rail voltage, reaches an equilibrium with the supplied photocurrent. The solid line with the triangle markers display the solution to the differential equation Eqn. 2.19, which governs this process. The dashed line reproduces the Spectre simulation of this process from Fig. 2.19 | 48 |

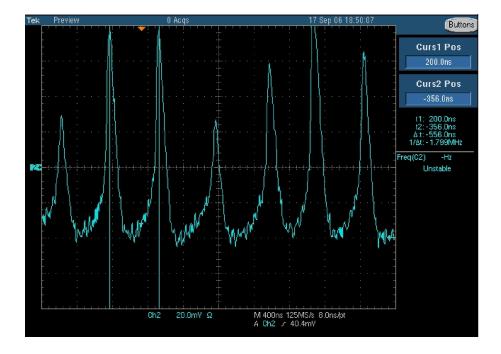

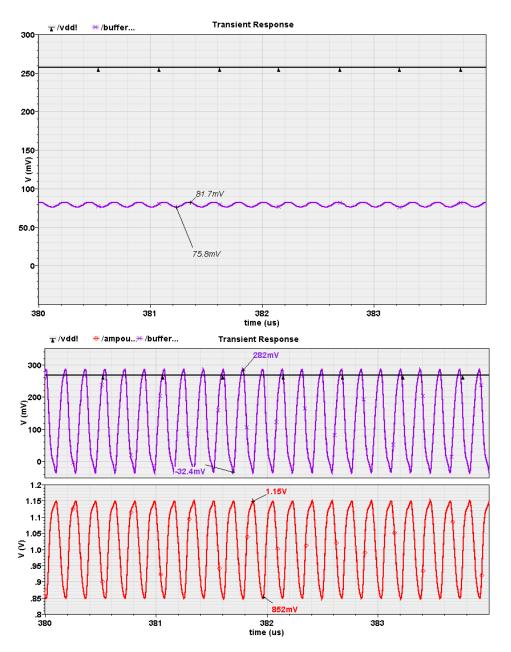

| 2.26 | Amplifier output with 3DIC under red laser pointer light. The maximum signal amplitude is 130 mV, and dominant frequency is 1.8 MHz. The bottom signal level is at $\sim 39$ mV                                                                                                                                                                                                                                                                                                                                                     | 50 |

| 2.27 | An at-a-glance floorplan of the 3DM2 chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 53 |

| 2.28 | The no-silicide version of the CBN/CBP annular diode. The dimensions are the same as the diode in Figure 2.11                                                                                                                                                                                                                                                                                                                                                                                                                       | 55 |

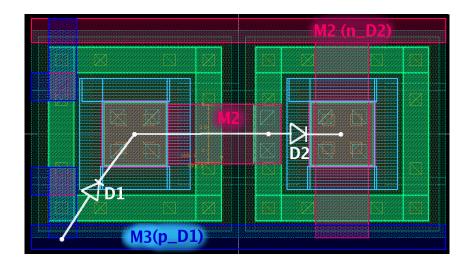

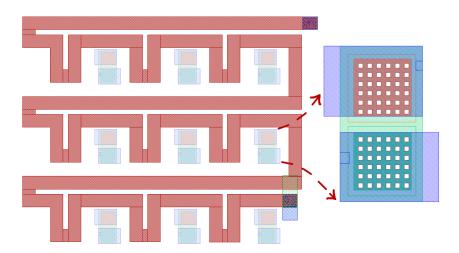

| 2.29 | The layout for one branch of the two-serial-diodes-per-branch photo-<br>diode array. The overlay shows how the diodes are connected by the<br>metal-2 bridge in the center                                                                                                                                                                                                                                                                                                                                                          | 56 |

| 2.30 | The layout for a quartet of branches for the two-serial-diodes-per-<br>branch photodiode array. The layout was constructed by creating a<br>mosaic out of these quartets                                                                                                                                                                                                                                                                                                           | 56 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.31 | The externally-powered amplifier used in the third quarter of the 3DM2 chip                                                                                                                                                                                                                                                                                                                                                                                                        | 57 |

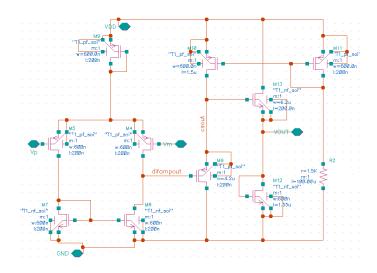

| 2.32 | Top: The self-powered oscillator and buffer driving a 1 pF off-chip load. Bottom, first graph: The output of the self-powered oscillator and buffer driving the externally-powered built-in amplifier. Bottom, second graph: The output of the externally-powered built-in amplifier, with the above input, driving a 1pF off-chip load                                                                                                                                            | 58 |

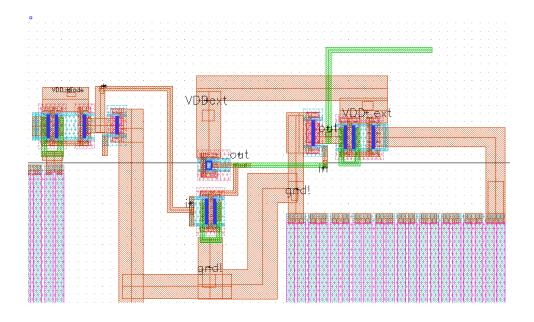

| 2.33 | Layout of the externally-powered amplifier used in the third quarter of the 3DM2 chip                                                                                                                                                                                                                                                                                                                                                                                              | 59 |

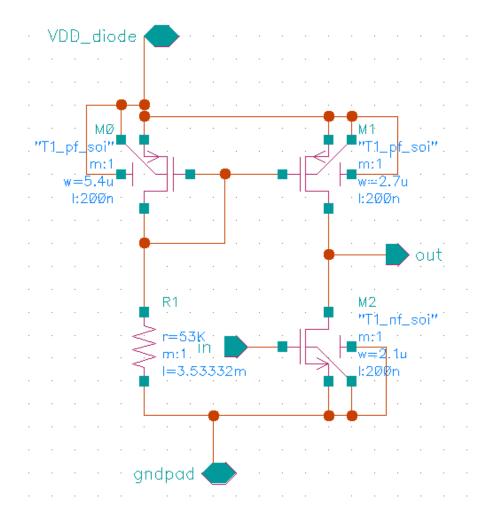

| 2.34 | Schematic of the self-powered amplifier implemented in the fourth quarter of the 3DM2 chip. The amplifier is a simple common-source amplifier, biased by a current mirror which is fed by the photodiode arrays                                                                                                                                                                                                                                                                    | 60 |

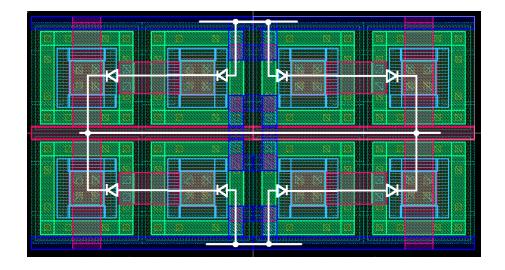

| 2.35 | Top: The full layout for the self-powered amplifier, and the externally-powered level shifter and output amplifier to drive off-chip load. Full resistor layouts are once more cropped out for visual clarity. Left: a schematic representation of the components in the above layout                                                                                                                                                                                              | 61 |

| 2.36 | A 3-D inverter formed by fabricating a PMOS over an NMOS using epitaxial lateral overgrowth (ELO) techniques (adapted from [2]). The n layer which forms the channel of the PMOS is grown using ELO. The poly gate is common to both transistors                                                                                                                                                                                                                                   | 63 |

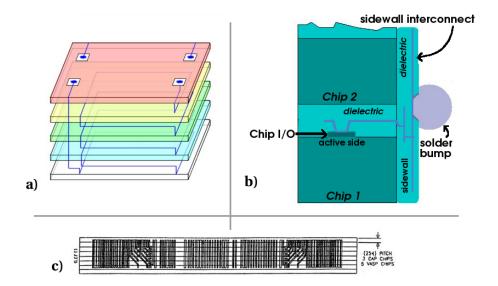

| 2.37 | a) A schematic representation of a stack of integrated circuits connected to each other through interconnects extended to the edges and routed on the sidewall. b) A cross-section of a stack of two chips connected vertically through a T-connection formed on the sidewall, with outside connections enabled by a solder bump, adapted from [64]. c) The schematic representation of the sidewall connections for a stack of VLSI associative string processor chips, from [62] | 65 |

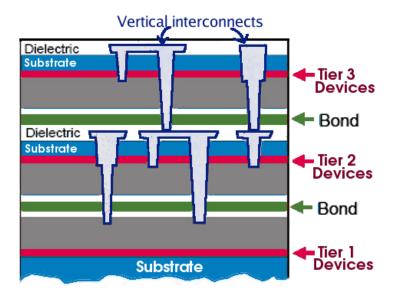

| 2.38 | upper tiers are thinned, but not removed entirely, and the process<br>in question is a bulk process. The bottom tier has the active side<br>facing up, while the higher tiers have the active devices facing down.                                                                                                                                                                                                                                                                 |    |

|      | (Adapted from [66].)                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67 |

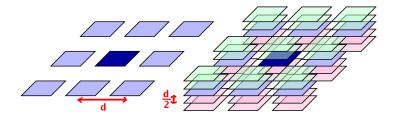

| 2.39 | Using the same maximum interconnect linear length, a central unit in a three-dimensional configuration can access many more neighboring units, depending on the relative sizes of the central unit vs. layer-to-layer distance in a stack                                                                                           | 70 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

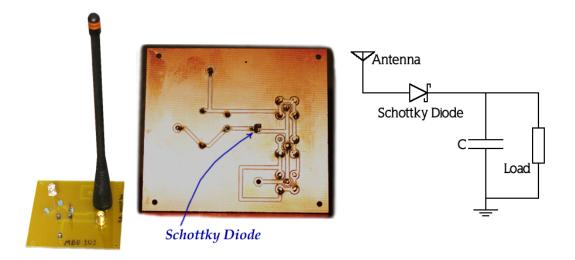

| 2.40 | Photos of the rectifying antenna system: Left, the full board with an LED load; middle: close-up of the back side of the board with the Schottky diode. Right: Schematic of the circuit.                                                                                                                                            | 79 |

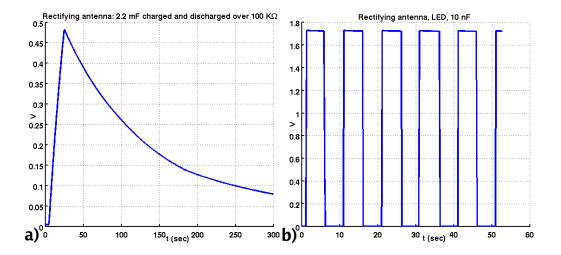

| 2.41 | a) The rectifying antenna of Fig. 2.40 charging a 2.2 mF capacitor over twenty seconds, with $\sim 5 \text{mW}$ of RF power provided at $\sim \! \! 467$ MHz. b) The voltage drop across an LED load being suppled by the rectifying antenna as the RF power is turned on and off                                                   | 79 |

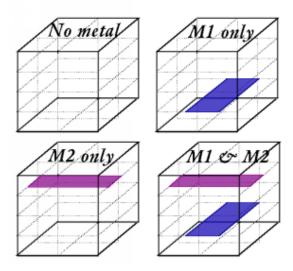

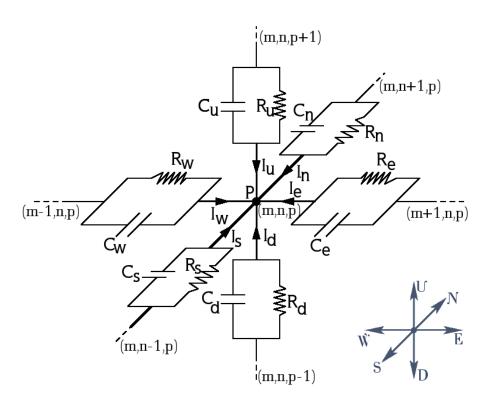

| 3.1  | Unit cell examples for a two-metal process                                                                                                                                                                                                                                                                                          | 84 |

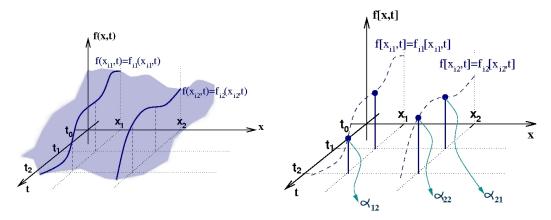

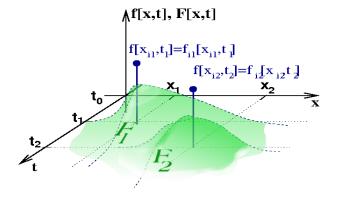

| 3.2  | Left: A continuous time-and-space dependent function. Right: A discretized time-and-space dependent function, which can be written as the sum of its samples using the coefficients $\alpha_{ij}$                                                                                                                                   | 86 |

| 3.3  | Time-dependent responses over all space to two individual impulse-<br>type inputs applied at different x-points at different times $t_j$                                                                                                                                                                                            | 86 |

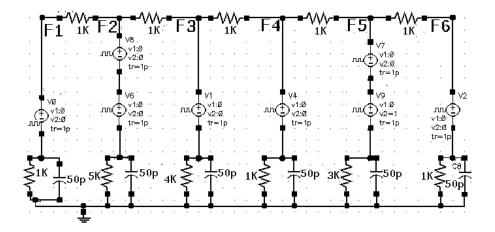

| 3.4  | A linear network with six nodes defined                                                                                                                                                                                                                                                                                             | 88 |

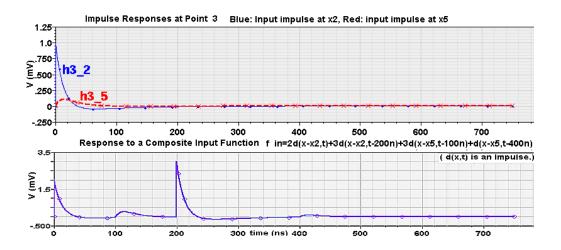

| 3.5  | Top: Simulated impulse responses at node $x_3$ to impulses at $x_2$ and $x_5$ . Bottom: Simulated output at node $x_3$ to the input of Eqn. 3.7.                                                                                                                                                                                    | 89 |

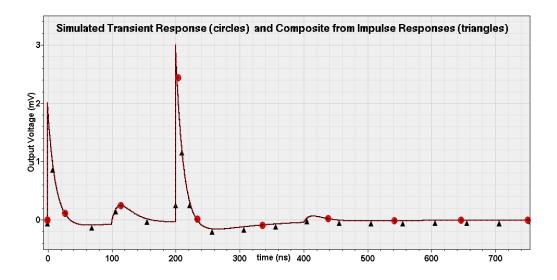

| 3.6  | Response at node $x_3$ calculated using Eqn. 3.8 (black triangles) together with the simulated output (red circles), exact agreement                                                                                                                                                                                                | 89 |

| 3.7  | Two-metal network; a simplified equivalent RC network shown. Possible unit cells partitioned with dashed outlines. Note that where two metal lines on different layers overlap with a via, the connection between the mesh points on the overlap is resistive, whereas at locations without a via the same connection is capacitive | 92 |

| 3.8  | The element values that need to be defined per mesh point by the mesh creator code                                                                                                                                                                                                                                                  | 93 |

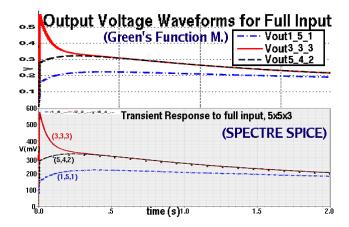

| 3.9  | A 5x5x3 mesh full response simulation. Top: Our solver combines impulse responses at three points using the input data. Bottom: SPECTRE performs full mesh solution at each timestep for the same input pattern. The solutions match                                                                                                | 98 |

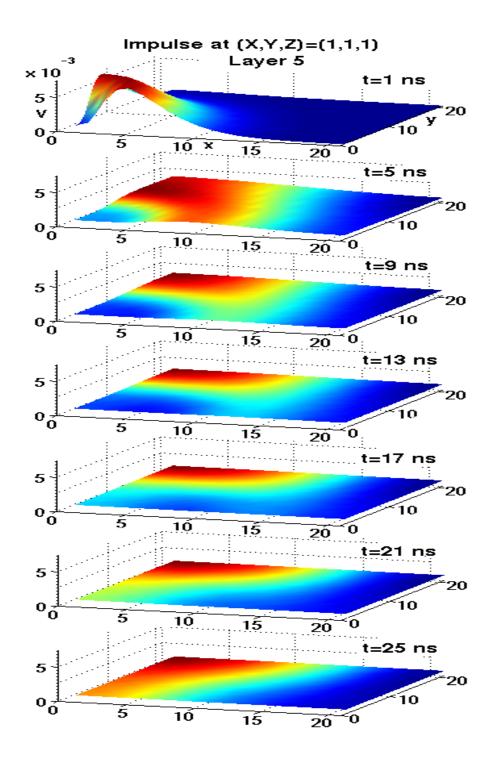

| 3.10 | The time evolution of the Green's Function of a $21x21x5$ system on the topmost leaver (layer 5). The unit impulse was injected at $t=0$ into point $(1,1,1)$ : The lower left corner of the lowest level, layer 1. The uneven spread is due to the lower resistivity of the network in the N-S direction    | . 102 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

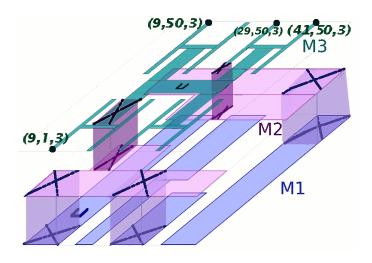

| 3.11 | 3-metal interconnect network. Vias: $\mathbf{X}$ . Inputs: $\sqcup$ . Outputs: $\bullet$                                                                                                                                                                                                                     | . 103 |

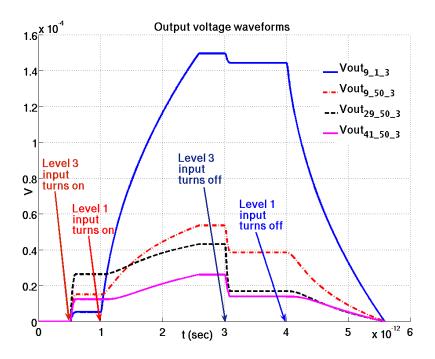

| 3.12 | Responses of the network in Fig. 3.11 to a combined input signal injected at points (5,15,1) and (25,25,3). Distance as well as the effect of inter-level coupling and presence of paths to ground affect the responses                                                                                      | . 103 |

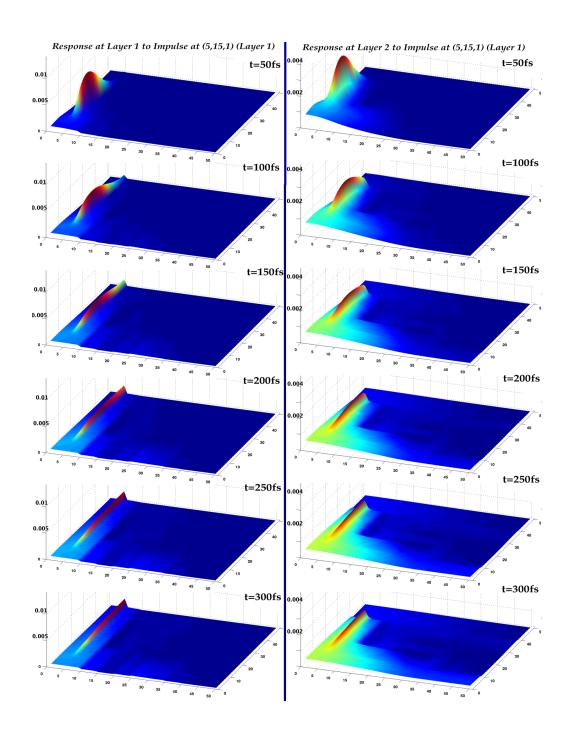

| 3.13 | Responses of the network in Fig. 3.11 over time to an impulse injected at point (5,15,1). Left: Response at Level 1 (Metal 1 network) over 300 femtoseconds. Right: Response at Level 2 (Metal 2 network) over 300 femtoseconds                                                                              | . 104 |

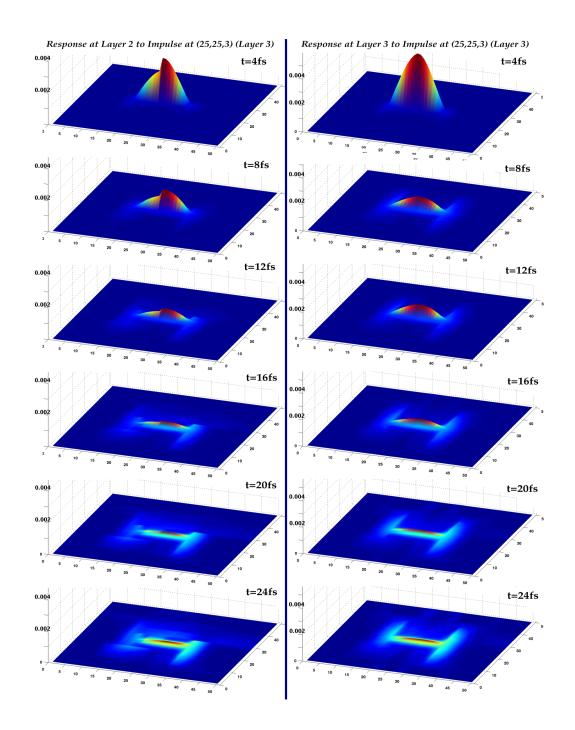

| 3.14 | Responses of the network in Fig. 3.11 over time to an impulse injected at point (25,25,3). Left: Response at Level 2 (Metal 2 network) over 24 femtoseconds. Right: Response at Level 3 (Metal 3 network) over 24 femtoseconds                                                                               | . 105 |

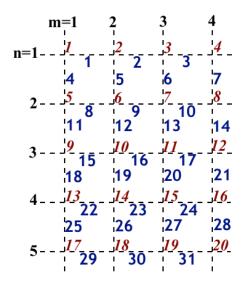

| 4.1  | An example mesh for a 2-D thermal network. The temperature is measured at nodes, numbered with the red (italic) numbers. The thermal conductivity is the property of the material on the branches, numbered with the blue (sans serif) numbers, between the nodes                                            | . 112 |

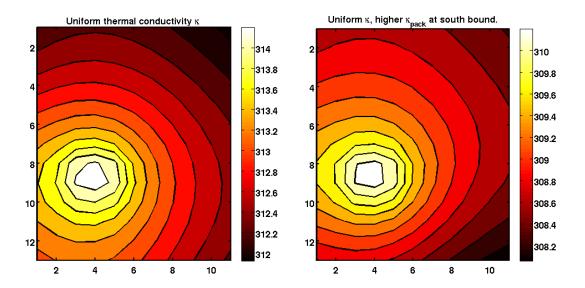

| 4.2  | Left: Resulting temperature distribution with a uniform $\kappa$ distribution. Right: Resulting temperature distribution with the same uniform $\kappa$ distribution, with the southern boundary three times as thermally conductive to ambient than the other boundaries                                    | . 114 |

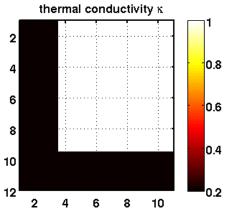

| 4.3  | A non-uniform thermal conductivity distribution. The light-colored areas are five times more thermally conductive than the dark areas.                                                                                                                                                                       | . 115 |

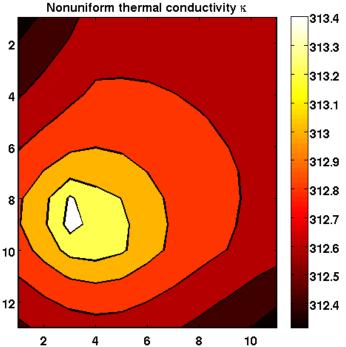

| 4.4  | Resulting temperature distribution with the nonuniform $\kappa$ distribution given in Fig. 4.3                                                                                                                                                                                                               | . 115 |

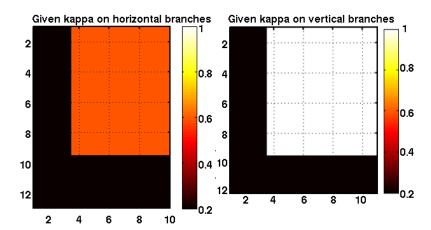

| 4.5  | A directionally non-uniform thermal conductivity distribution. The left-side and right-side shows the $\kappa$ distribution of the E-W branches and N-S branches respectively. The gray (orange) areas are three times, the light-colored areas are five times more thermally conductive than the dark areas | . 116 |

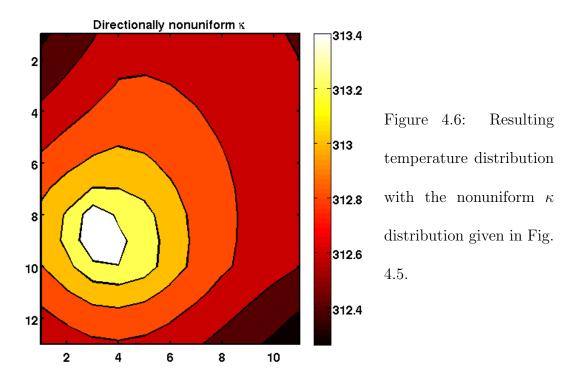

| 4.6  | Resulting temperature distribution with the nonuniform $\kappa$ distribution given in Fig. 4.5                                                                                                                                                                                                                                      | . 116 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

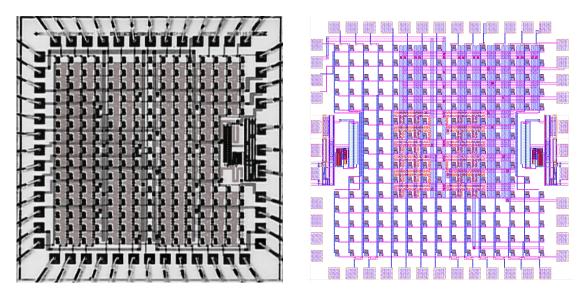

| 4.7  | Left: The A-type heater/temperature array sensor chip, microphotograph. Right: The B-type heater/temperature array sensor chip, layout                                                                                                                                                                                              | . 119 |

| 4.8  | An example polysilicon microheater resistor. The poly layout shape is designed to surround temperature-sensor diodes, which are shown faintly within the microheater layout, with one example layout to the right                                                                                                                   | . 120 |

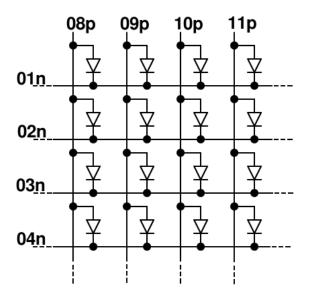

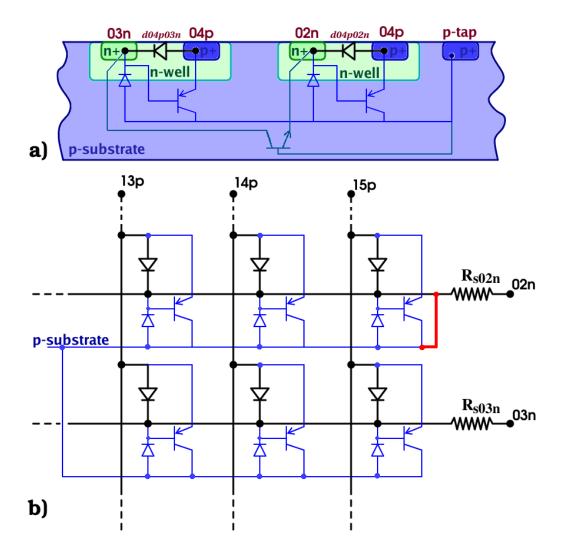

| 4.9  | Schematic representation of five columns and five rows of the diode array. For reference purposes, for instance, the diode on the top left corner of this schematic would have the label ${\bf d08p01n}.$                                                                                                                           | . 125 |

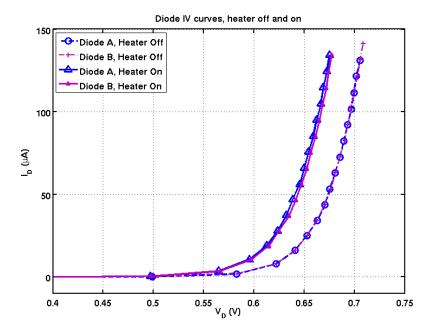

| 4.10 | IV curves of two diodes on the Type A and Type B chips. The dashed and dot-dashed lines with circle and square markers are measurements taken at room temperature. The solid lines with triangle markers are measurements taken with the heater over these diodes turned on                                                         | . 126 |

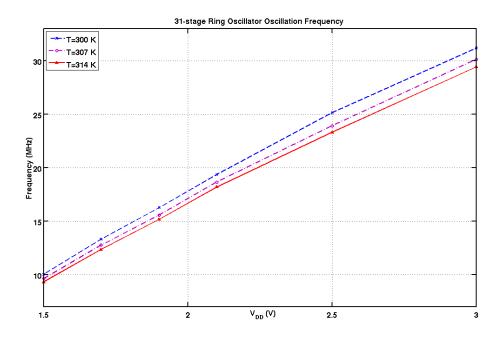

| 4.11 | SPECTRE simulation results for 31-stage minimum-size ring oscillator oscillation frequency vs. rail voltage for T=300 K, 307 K and 314 K, using the AMI 1.5 $\mu$ m technology                                                                                                                                                      | . 129 |

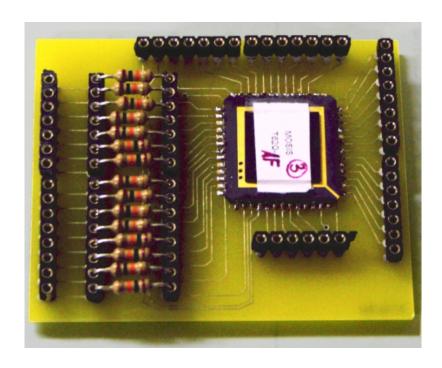

| 4.12 | A Type-B measurement chip mounted on the experimental PCB                                                                                                                                                                                                                                                                           | . 132 |

| 4.13 | The circuit for diode IV curve measurement                                                                                                                                                                                                                                                                                          | . 133 |

| 4.14 | a) The formation of parasitic BJTs in the diode array. b) The simplified equivalent circuit of a small (3x2) diode array, with the parasitic BJT and n-well/substrate diodes shown. The red (thick) wire indicates the shorting of the n-side of the diodes of the row under measurement, Row 2 in this example, to the p-substrate | . 134 |

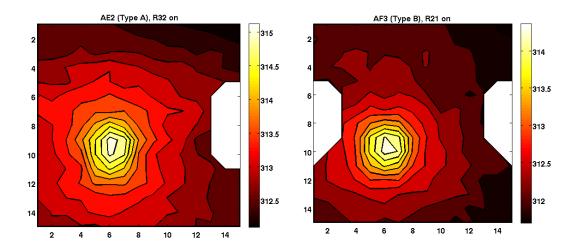

| 4.15 | Measurement results from the Type-A chip with the uniform metal network                                                                                                                                                                                                                                                             | . 135 |

| 4.16 | Measurement results from the Type-B chip with the asymmetric metal network                                                                                                                                                                                                                                                          | . 135 |

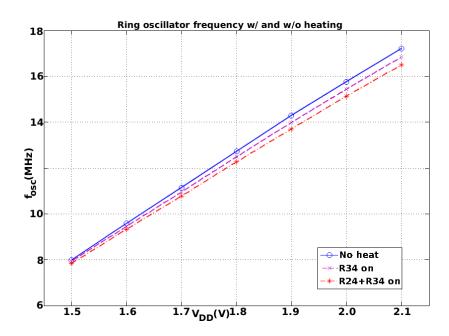

| 4.17 | Measured ring oscillator frequency vs. rail voltage from chip Type A, when one (R24) or two (R24+R34) of the heaters next to the oscillator are operating                                                                                                                                                                           | . 136 |

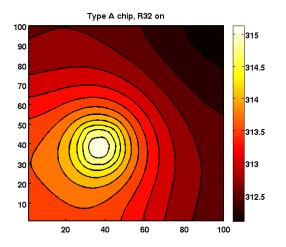

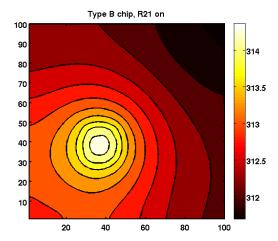

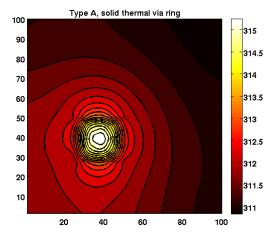

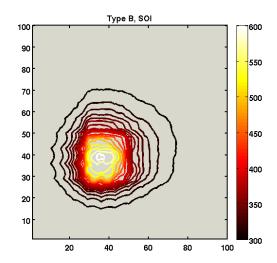

| <ul> <li>4.19 Simulation results for the Type-B chip (asymmetric metal network), displaying the temperature distribution at the substrate level, matching Fig. 4.16</li></ul>                          | 4.18 | Simulation results for the Type-A chip (uniform metal network), displaying the temperature distribution at the substrate level, matching Fig. 4.15                                                     | . 139 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

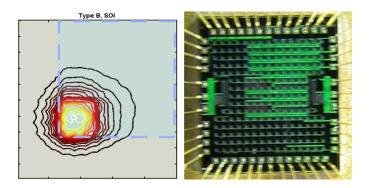

| frame consisting of metal poles from the topmost layer all the way down to the substrate placed around the operating heater                                                                            | 4.19 | displaying the temperature distribution at the substrate level, match-                                                                                                                                 | . 139 |

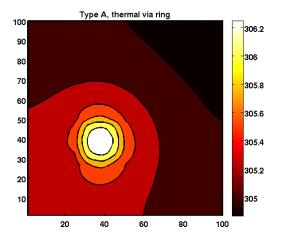

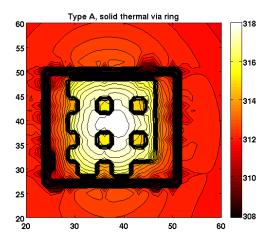

| via frame placed around the heater, operating at 0.46 W to obtain a comparable temperature range as the original measurement                                                                           | 4.20 | frame consisting of metal poles from the topmost layer all the way                                                                                                                                     | . 141 |

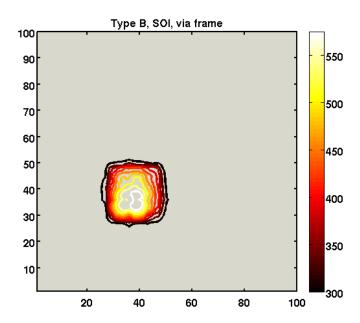

| an unbroken vertical thermal via frame from the topmost layer all the way down to the substrate placed around the operating heater                                                                     | 4.21 | via frame placed around the heater, operating at 0.46 W to obtain a                                                                                                                                    | . 141 |

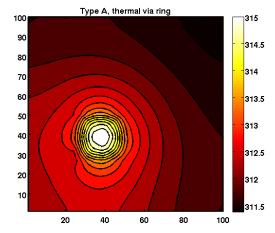

| with the same frame as Fig. 4.22. Note that the axis of this figure are zoomed in from the full-chip scale                                                                                             | 4.22 | an unbroken vertical thermal via frame from the topmost layer all the                                                                                                                                  | . 142 |

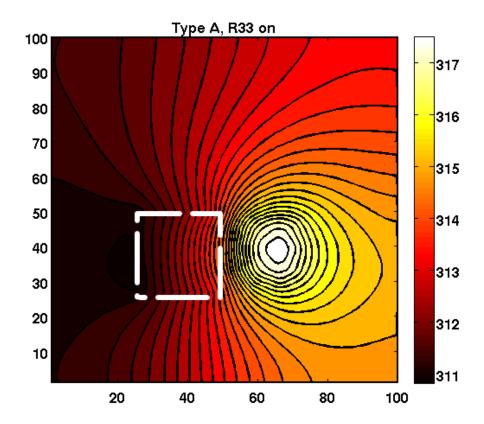

| east of the via frame is operating. The via frame, consisting of poles, is marked with a dashed white outline                                                                                          | 4.23 | with the same frame as Fig. 4.22. Note that the axis of this figure                                                                                                                                    | . 142 |

| of the Type-A chip (uniform metal network), with the same heater operating as the results in Fig. 4.18                                                                                                 | 4.24 | east of the via frame is operating. The via frame, consisting of poles,                                                                                                                                | . 143 |

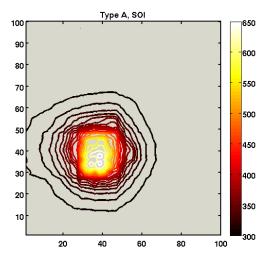

| the Type-B chip (asymmetric metal network), with the same heater operating as the results in Fig. 4.19                                                                                                 | 4.25 | of the Type-A chip (uniform metal network), with the same heater                                                                                                                                       | . 145 |

| metal interconnects in Chip Type B, also visible in the chip photograph. It is clear from the contour lines that the thermal gradients change at the boundaries of this region                         | 4.26 | the Type-B chip (asymmetric metal network), with the same heater                                                                                                                                       | . 145 |

| frame consisting of poles connecting the substrate to the ambient. The peak substrate temperature for the area under the substrate falls to 572.59 K and the areas outside the via frame experience no | 4.27 | metal interconnects in Chip Type B, also visible in the chip photograph. It is clear from the contour lines that the thermal gradients                                                                 | . 145 |

|                                                                                                                                                                                                        | 4.28 | frame consisting of poles connecting the substrate to the ambient. The peak substrate temperature for the area under the substrate falls to 572.59 K and the areas outside the via frame experience no | 146   |

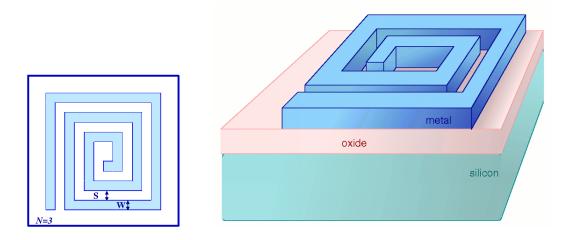

| 5.1  | Top and side views of typical square spiral on-chip inductors                                                                                                                  | 151 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

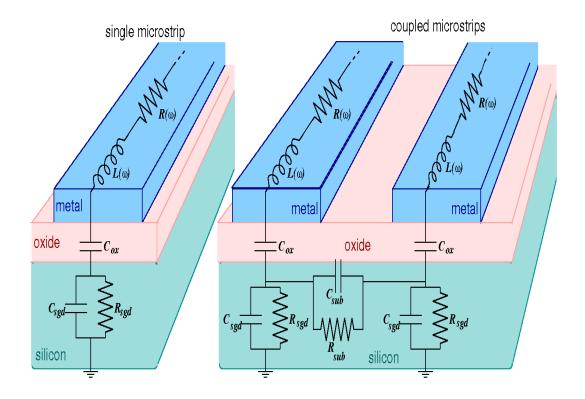

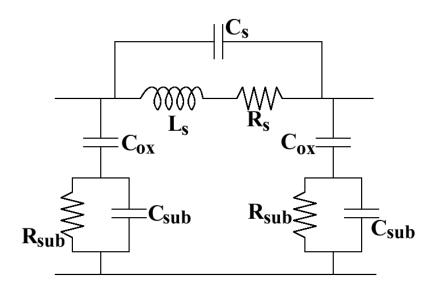

| 5.2  | Lumped-element models for a single microstrip and coupled microstrips on a lossy substrate, which can represent the metal-oxide-semiconductor system of on-chip inductors.     | 154 |

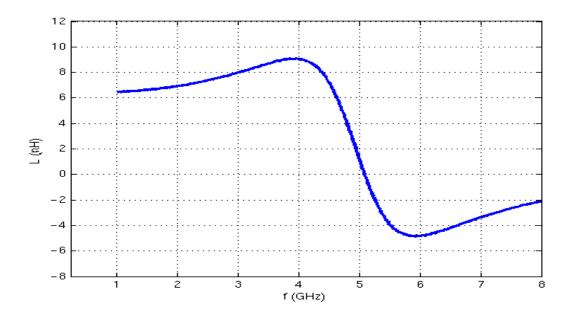

| 5.3  | The measured inductance of a typical on-chip spiral inductor vs. frequency, as defined by Eqn. 5.2                                                                             | 155 |

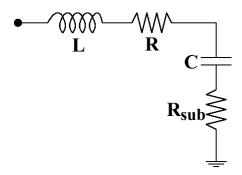

| 5.4  | A very basic lumped circuit model which gives the same sort of impedance response with the same three regions of an on-chip inductor response                                  | 156 |

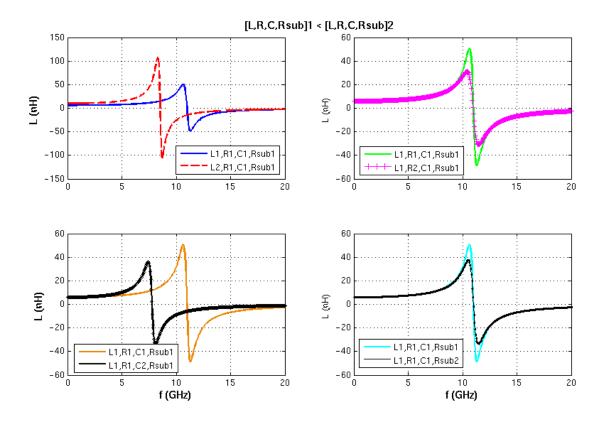

| 5.5  | Changes in the elements of the simple lumped circuit of Fig. 5.4 reflected by changes in its inductance curve                                                                  | 156 |

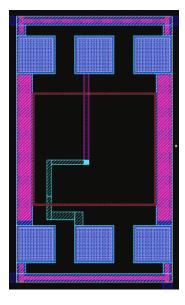

| 5.6  | An on-chip inductor within a probe-pad structure designed for two-port S-parameter measurements                                                                                | 158 |

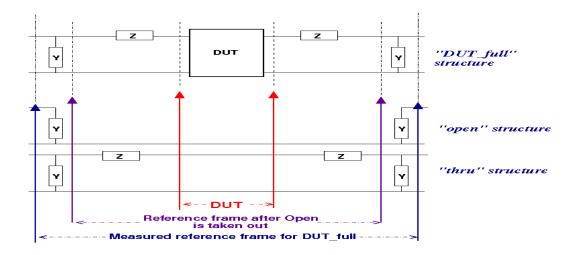

| 5.7  | Open and thru de-embedding structures for on-chip measurements                                                                                                                 | 159 |

| 5.8  | De-embedding.                                                                                                                                                                  | 160 |

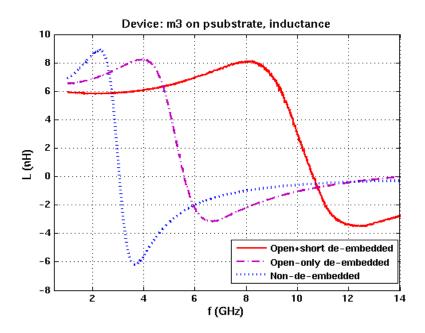

| 5.9  | Results of the de-embedding process                                                                                                                                            | 161 |

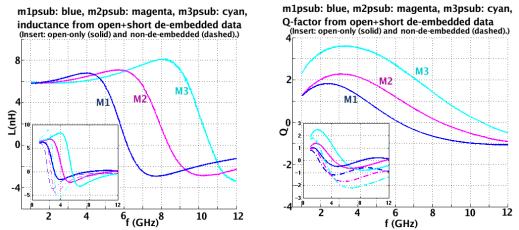

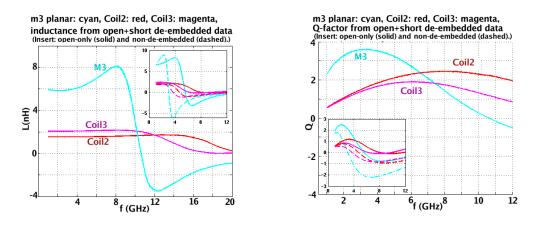

| 5.10 | Inductance and quality factor plots for inductors built on p-substrate using different metal layers. (M3 ("m3psub"): Metal 3, M2 ("m2psub"): Metal 2, M1 ("m1psub"): Metal 1.) | 162 |

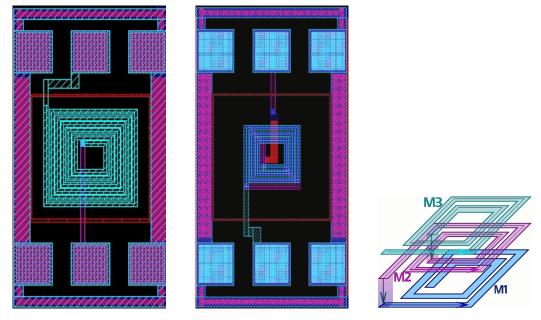

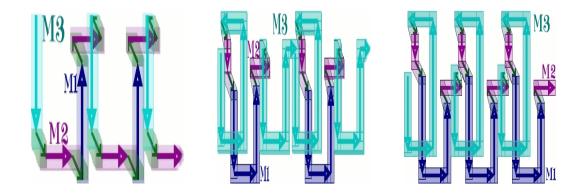

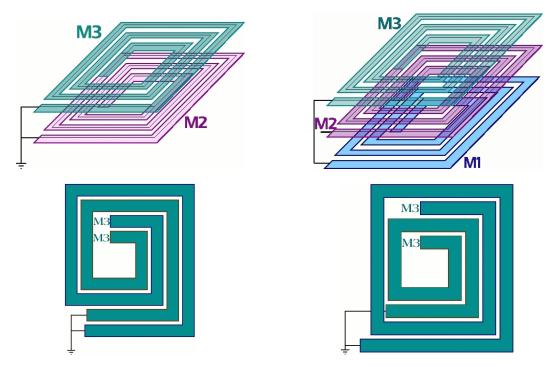

| 5.11 | Layouts for planar and stacked inductors; schematic representation of the latter                                                                                               | 162 |

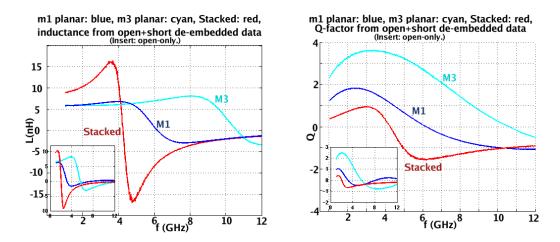

| 5.12 | Inductances and quality factors of planar and stacked inductors. (M3, M1: Planar Metal 3 and Metal 1.)                                                                         | 163 |

| 5.13 | Schematic representations of the "Coil1," "coil2" and "coil3"                                                                                                                  | 164 |

| 5.14 | Layouts of the coil inductor variants coil2 and coil3                                                                                                                          | 164 |

| 5.15 | Inductances and quality factors for planar and coiled inductors. (M3: Planar Metal 3.)                                                                                         | 164 |

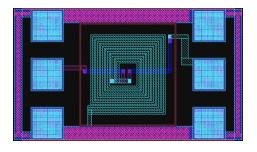

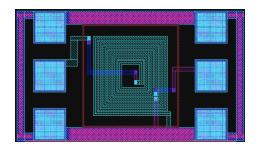

| 5.16 | Different transformers: M2:M3 (metal 2 to metal 3), M2:M1M3 (metal 2 to metal 1+metal 3), interwound, spiral-within-spiral                                                     | 165 |

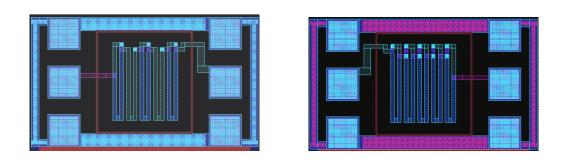

| 5.17 | Layouts for the M2:M3 and spiral-within-spiral transformers                                                                                                                    | 166 |

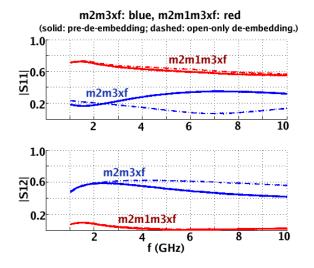

| 5.18 | Reflection and transmission coefficients, for the M2:M3 ("m2m3xf," metal 2 to metal 3, blue) and M2:M1M3 ("m2m1m3xf," metal 2 to metal 1+ metal 3, red) transformers                                                                                                                                                                                                          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

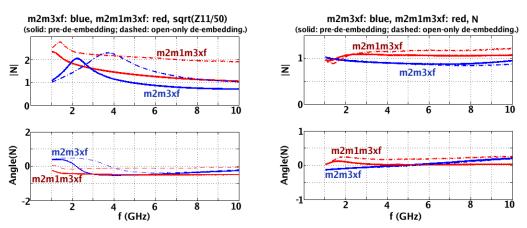

| 5.19 | "Turn ratio" (left) and voltage gain (right) for the M2:M3 ("m2m3xf," metal 2 to metal 3, blue) and M2:M1M3 ("m2m1m3xf," metal 2 to metal 1+ metal 3, red) transformers                                                                                                                                                                                                       |

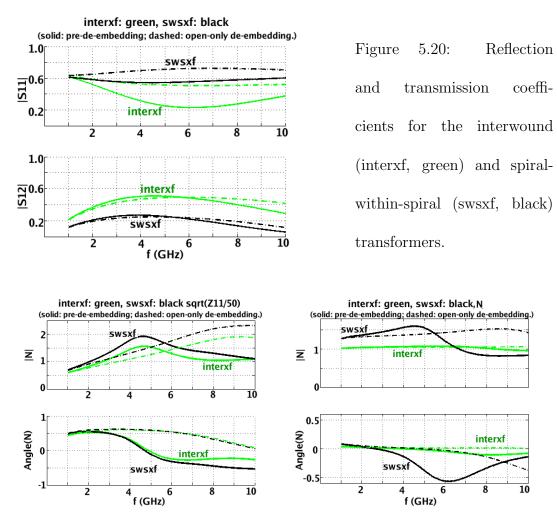

| 5.20 | Reflection and transmission coefficients for the interwound (interxf, green) and spiral-within-spiral (swsxf, black) transformers 168                                                                                                                                                                                                                                         |

| 5.21 | "Turn ratio" (left) and voltage gain (right) for the interwound (interxf, green) and spiral-within-spiral (swsxf, black) transformers 168                                                                                                                                                                                                                                     |

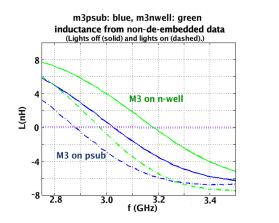

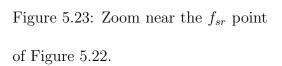

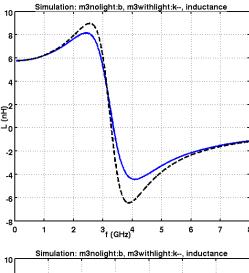

| 5.22 | The measured inductances of two metal-3 on-chip spiral inductors, one on p-substrate and the other on an n-well. Solid lines: External light off. Dashed lines: Light on. This is data prior to de-embedding. 170                                                                                                                                                             |

| 5.23 | Zoom near the $f_{sr}$ point of Figure 5.22                                                                                                                                                                                                                                                                                                                                   |

| 5.24 | Zoom near the peak impedance point of Figure 5.22 170                                                                                                                                                                                                                                                                                                                         |

| 5.25 | A more advanced lumped circuit model for on-chip inductors [131] 171                                                                                                                                                                                                                                                                                                          |

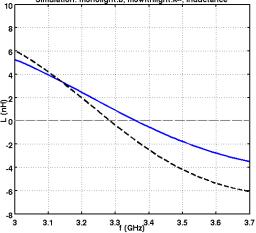

| 5.26 | Spectre s-parameter simulation results for the lumped-circuit inductor model of Fig. 5.25 with the element values in the text. Solid line: "Light off". Dashed line: "Light on," with the substrate resistance reduced                                                                                                                                                        |

| 5.27 | Zoom near the $f_{sr}$ points of Figure 5.26                                                                                                                                                                                                                                                                                                                                  |

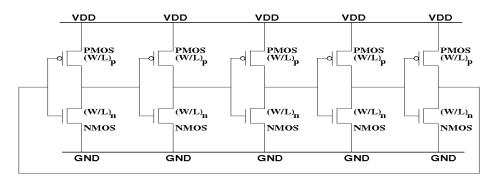

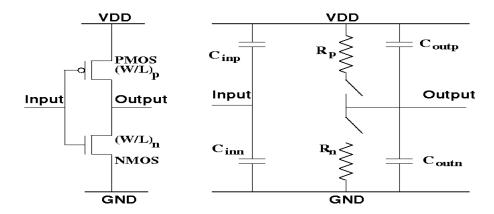

| 5.28 | A five-stage ring oscillator                                                                                                                                                                                                                                                                                                                                                  |

| 5.29 | The CMOS inverter and its digital model. The input and output capacitances are proportional to the transistors' gate oxide capacitances: $C_{in} = 1.5C_{ox}$ and $C_{out} = C_{ox}$ approximately. The effective switching resistances are the average resistances of the relevant MOS-FETs between the off and the on stages of the full swing: $R_{n,p} = V_{DD}/I_{Dn,p}$ |

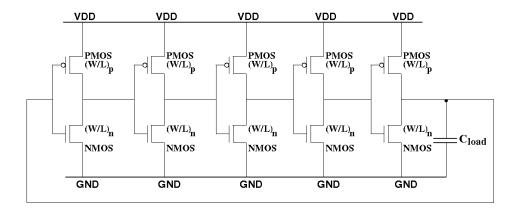

| 5.30 | A five-stage ring oscillator with a capacitive load between two of the stages                                                                                                                                                                                                                                                                                                 |

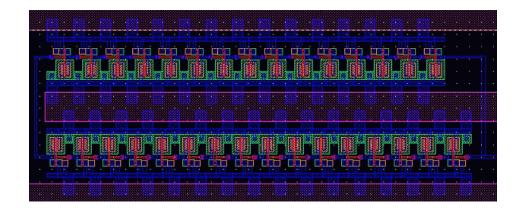

| 5.31 | The 31-stage ring oscillator comprised of minimum-size transistors in the 0.6 $\mu$ m technology chip. The output is taken from between the stages on the lower and upper right hand corners and goes through an additional inverter, which serves as a buffer (not shown) 179                                                                                                |

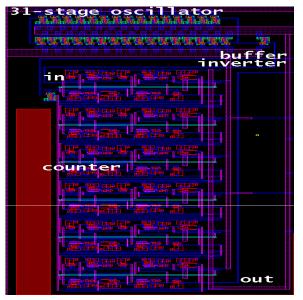

| 5.32 | The layout for the 31-stage ring oscillator and 6-bit counter/divide-by-64 frequency divider                                                                                                                                                                                                                                           | 179 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.33 | Three stages of the external ring oscillator. The bonding pad connections are visible on the top and left edges of the figure                                                                                                                                                                                                          | 180 |

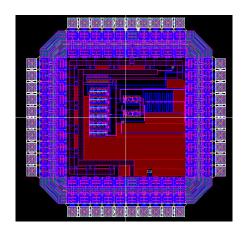

| 5.34 | The full chip layout for the C5N chip                                                                                                                                                                                                                                                                                                  | 180 |

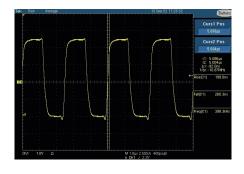

| 5.35 | The output waveform of the 11-stage external ring oscillator                                                                                                                                                                                                                                                                           | 181 |

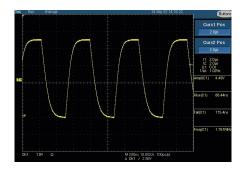

| 5.36 | The output waveform of the divide-by-64 counter obtaining its input from the 31-stage internal ring oscillator                                                                                                                                                                                                                         | 181 |

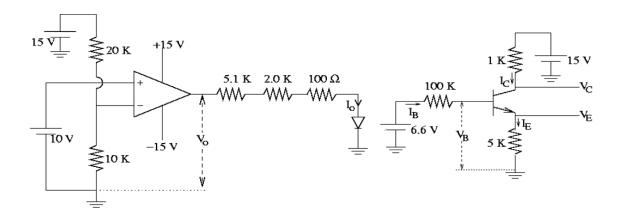

| 6.1  | Example exam questions. These were the associated question statements: (Left circuit) For this op-amp circuit, what are $I_o$ and $V_o$ ? Is the LED on, why or why not? (Right circuit) For the BJT circuit $\beta$ =100 and $V_{BE}$ =0.7. Draw the DC equivalent circuit. Calculate $I_B$ , $I_E$ , $I_C$ , $V_B$ , $V_E$ and $V_C$ | 195 |

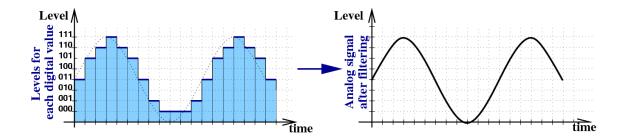

| 6.2  | Example digital-to-analog conversion question. The sequence: <b>011 101 110 111 110 101 011 001 000 000 000 001 011 101 110 111 110 101 011</b>                                                                                                                                                                                        | 200 |