# ACCOMPLISHMENT OF CIRCUIT PARTITIONING USING VHDL AND CLUSTERING PERTAINING TO VLSI DESIGN

<sup>1</sup>Prof. K.A. Sumitra Devi, <sup>2</sup> Vijayalakshmi.M.N, <sup>3</sup> Dr.R.Vasantha <sup>4</sup>Dr.Annamma Abraham

<sup>1</sup> HOD, Department of MCA, R.V.College of Engineering, Bangalore-59

<sup>2</sup> Sr.Lecturer, Department of MCA, R.V.College of Engineering, Bangalore-59

<sup>3</sup> Prof, Department of ISE, R.V.College of Engineering, Bangalore-59

<sup>4</sup> Asst.Prof, Department of MCA, R.V.College of Engineering, Bangalore-59

*Abstract*— The relevance of VLSI in performance computing, telecommunications, and consumer electronics has been expanding progressively, and at a very hasty pace. In order to build complex digital logic circuits it is often essential to sub-divide multi – million transistors design into manageable pieces. Circuit partitioning is a general approach used to solve problems that are too large and complex to be handled at once. In partitioning, the problem is divided into small and manageable parts recursively, until the required complexity level is reached. In the area of VLSI, circuit complexity is rapidly multiplying, together with the reducing chip sizes; the integrated chips being produced today are highly sophisticated. There are many diverse problems that occur during the development phase of an IC that can be solved by using circuit partitioning which aims at obtaining the sub circuits with minimum interconnections between them. This paper aims at circuit partitioning using clustering technique by applying two clustering algorithms NNA(Nearest Neighbour) PAM(Partitioning around mediods). These two algorithms were tested on a BCD to Seven Segment Code Converter circuit consisting of eight nodes and were implemented on VHDL. The tested results show that PAM yield better subcircuits than NNA.

Keywords: Circuit Partitioning, VLSI, NNA, PAM

### I. INTRODUCTION

Advances in semiconductor technology and in the integration level of integrated circuits have enhanced many features, increased the performance; improved reliability of electronic equipment, and at the same time reduced the cost, power consumption and system size. As size and complexity of digital system has increased, more computer aided design tools are introduced into hardware design processes. VLSI design automation has attracted a great deal of interest. A recent survey [1] lists almost 200 papers on the subject. Circuit partitioning in VLSI design is key role in physical design. The objective of circuit partitioning is to divide the circuit into number of subciruits with minimum interconnections between them.

In past two decade, partitioning problems has been studied by researchers and various heuristic algorithms have been developed [2]-[4]. The circuit partitioning is also achieved by using some of the clustering algorithm [6]. In this paper to achieve circuit partitioning, with minimum interconnections is obtained by applications of two clustering algorithms PAM and NNA. These two clustering algorithms are applied to BCD to Seven segment circuit consisting of eight nodes. Results show that PAM gives better clusters with

minimum interconnections. Both the clustering algorithms are run on VHDL code and is tested.

#### II. IMPLEMENTATION

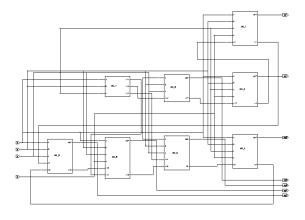

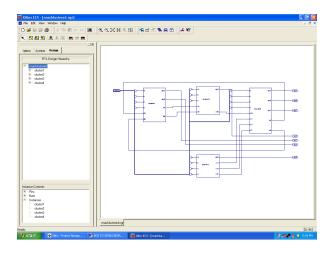

The implementation consists of three stages consisting of data extraction, partitioning and result. In data extraction, a VLSI circuit of BCD to 8 segment converter is considered. The circuit considered is shown below

Fig. 1

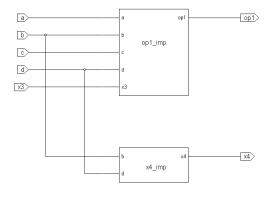

In the above circuit each rectangular box is considered as a node. The circuit consists of 8 nodes with interconnection between them. The sub circuits within one the node is shown in fig 2. The input to this circuit is a BCD(Binary coded Decimal) code and output is seven segment code.

Fig 2

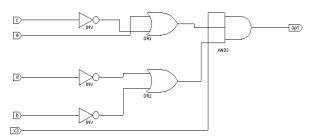

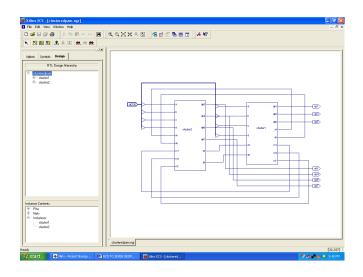

Figure 3 shows the internal view of op1\_mp which consists some of the basic gates like AND OR and inverter gates. Similarly each node consists of all the basic gates

Fig. 3

The out put is the seven segment display which is depicted in fig 4. The input to the circuit and the corresponding output obtained is shown in table 1.

Fig. 4

From the table 1 it is clear that whenever the input of '0', in the seven segment display except 'g' all other values are '1'. Since the input is BCD the input values are taken from '0' to '9' only.

Table 1: Input and Output for the BCD to Seven segment Circuit

| Input | Input | Input | Input | а | ь | С | đ | е | f | g |

|-------|-------|-------|-------|---|---|---|---|---|---|---|

| 1     | 2     | 3     | 4     |   |   |   |   |   |   |   |

| 0     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0     | 0     | 0     | 1     | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0     | 0     | 1     | 0     | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0     | 0     | 1     | 1     | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0     | 1     | 0     | 0     | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0     | 1     | 0     | 1     | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0     | 1     | 1     | 0     | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0     | 1     | 1     | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1     | 0     | 0     | 0     | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1     | 0     | 0     | 1     | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

## III. SUMMARY OF CLUSTGERING ALGORITHM

Clustering is referred as unsupervised learning segmentation. The clusters are formed by finding the similarities between data according to characteristics found in the data. It can be thought of as partitioning or segmenting the data into groups that might or might not be disjointed. In this paper we are using Nearest Neighbor Algorithm and PAM (Partitioning around mediods).

#### A. Nearest Neighbor Algorithm

This is serial algorithm in which the items are iteratively merged into the existing clusters that are closest. In this algorithm a threshold, t is used to determine if items will be added to existing clusters or if a new cluster is created The complexity of the algorithm depends on the number of items. For each loop each item must be compared to each item already in a cluster. The time complexity if O(n2)

#### **B.PAM** Algorithm

This algorithm[9] represent a cluster by a mediod. Using this algorithm handles outliers well. Quality of clusters is measured by the sum of all distances from a non-mediod object to the medoid for the cluster it is in. We use  $C_{jih}$  to be the cost change for an item  $t_j$  associated with swapping medoid  $t_i$  with non-medoid  $t_h$ . The total complexity per iteration is n(n-k)2. The cost is the change to the sum of all distances from items to their cluster medoids. The total impact to quality by a medoid change  $TC_{ih}$  is given by

$$TC_{ih} = \sum_{j=1}^{n} C_{jih}$$

#### IV. RESULTS AND CONCLUSION

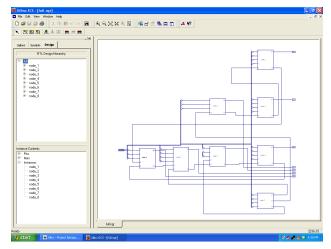

In data extraction, the circuit which is a BCD to seven segment code converter consisting of 8 nodes is considered. The circuit is represented by an adjacency matrix where the values represent the distances between the nodes. The adjacency matrix is fed into algorithm which gives the subcircuits with lowest amount of interconnections between them. The partition is tested on the circuit. The table below gives the performance of PAM and Nearest Neighbour algorithm. The algorithm is implemented on Xilinx 6.1 using project Navigator using VHDL.

#### V. CONCLUSION

In this paper the Circuit Partitioning which plays a critical role in physical design of an integrated circuit with minimum interconnections is obtained by implemented using two clustering algorithm PAM and NNA. Experimental results shows that NNA gives four clusters where are PAM gives two clusters for the same input. The circuit also shows the minimum interconnections between them.

Table2:Performance of PAM and NNA

| Input                      | No. of Clusters |                      |  |  |  |

|----------------------------|-----------------|----------------------|--|--|--|

|                            | PAM             | Nearest<br>Neighbour |  |  |  |

| BCD to<br>seven<br>segment | 2               | 4                    |  |  |  |

Screen shot showing the BCD to Seven segment Display

Screen shot depicting the circuit after application of NNA Algorithm consisting of 4 clusters

Screen shot depicting the circuit after application of PAM Algorithm consisting of 2 clusters

#### VI. REFERENCES

[1] Jianhua Li and Laleh Behjat,"A Connectivity Based Clustering Algorithm with Applications to VLSI Circuit Partitioning",IEEE Transactions on Circuits and Systems-II.Express Briefs, Vol. 53,No.5,May 2006.

- [2] C.J. Alpert and A.B. Kahng,"Recent directions in netlist partitioning:A.Survey,"VLSI J. Intefr., vol 19, pp. 1-81,1995

- [3] S. Dutt and W.Deng,"Probability-based approaches to vlsi circuit partitioning,"IEEE Trans.Comput-Aided Des. Integr.Circuits,vol, 19.pp-534-549,2000.

- [4] C.M.Fiduccia and R.M.Mattheyses,"Alinear time heuristic for improving network partitions",in Proc. ACM/IEEE DAC,1982,pp. 175-181.

- [5] Jan Madsen, Jesper Grode, and Peter V. Knudsen. Hardware/Software Partitioning using the LYCOS System, chapter 9. Hardware/Software Codesign: principles and Practice. Kluwer Academic Publishers, Netherlands, 1997.

- [6].Martin Ester,Hans-Peter Kriegel,Jorg Sander,Xiaowei Xu,Proceedings of 2nd International Conference on Knowledge Discovery and Data Mining (KDD-96)

- [7] L.W.Hagen,D.J. Huang, and A.B.Kahng,"On implementation choices for iterative improvement partitioning methods,"in Proc.Eur.DAC,1995,pp. 144-149.

- [8] "Comparative study of evolutionary model and clustering methods in circuit partitioning pertaining to VLSI design ", Prof. K.A.Sumithra Devi, Banashree N P, Dr. Annamma Abraham has been published in Enfomatika, International Journal of Applied Mathematics and Computer Sciences, Quarterly Volume 4 number 2 April 2007 ISSN 1305-5313, pp. 544 547

- [9] "Data Mining Introductory and Advanced Topics" ,Margaret H.Dunham,Pearson Education,Inc 2003