# Chapter 2

# Design and Fabrication of VLSI Devices

Jason Cong

1

# **Design and Fabrication of VLSI Devices**

#### **Objectives:**

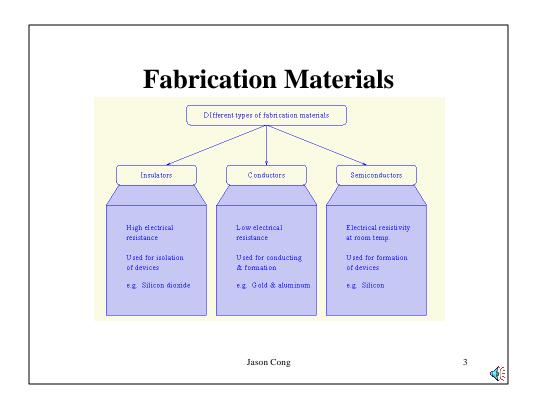

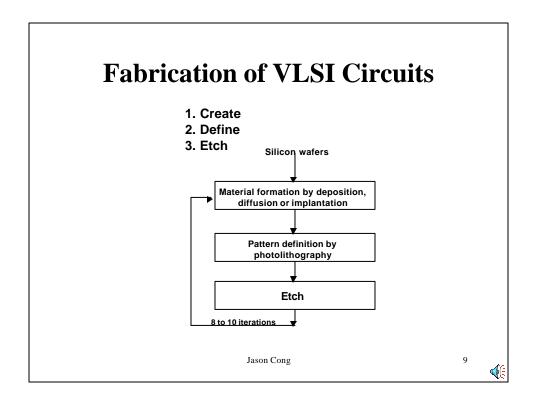

- To study the materials used in fabrication of VLSI devices.

- To study the structure of devices and process involved in fabricating different types of VLSI circuits

Jason Cong

2

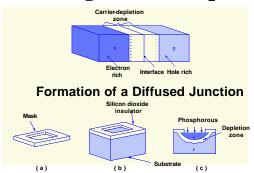

## The Three Regions in a n-p Junction

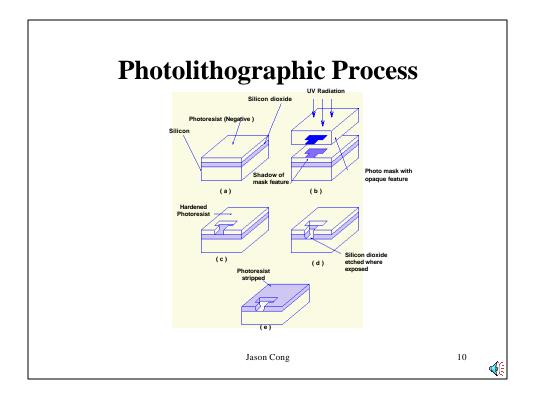

A *mask* is a specification of geometric shapes that need to be created on a certain layer. Masks are used to create a specific patterns of each material in a sequential manner and create a complex pattern of several layers

Jason Cong

3

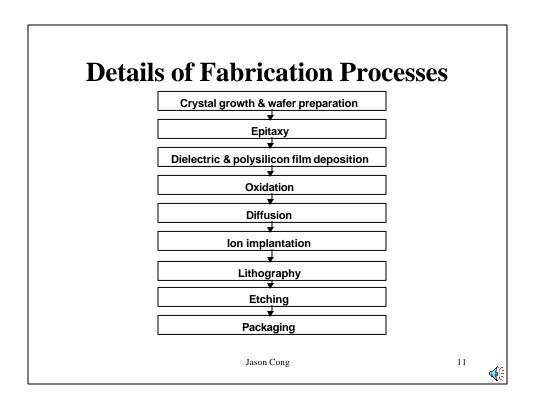

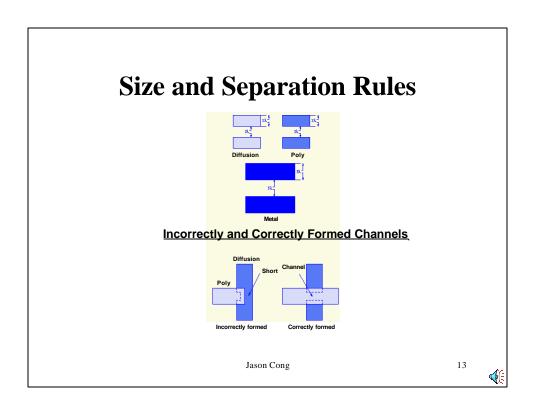

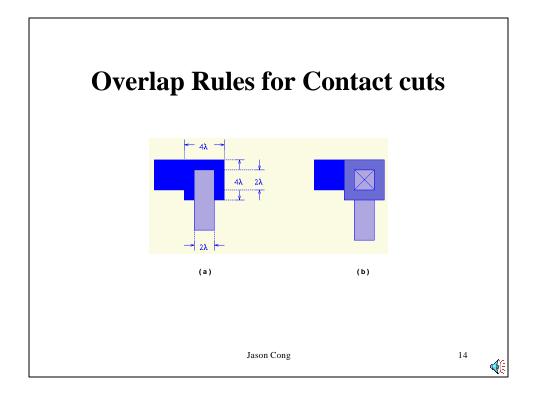

## **Basic Design Rules** 1. Size Rules

- 2. Separation Rules

- 3. Overlap Rules

#### **Basic nMOS Design Rules**

**Diffusion Region Width 2**l **Polysilicon Region Width 2**l **Diffusion-Diffusion Spacing 3**l **Poly-Poly Spacing 2**l **Polysilicon Gate Extension 2**l **Contact Extension** -1 **Metal Width 3**l

Jason Cong

12

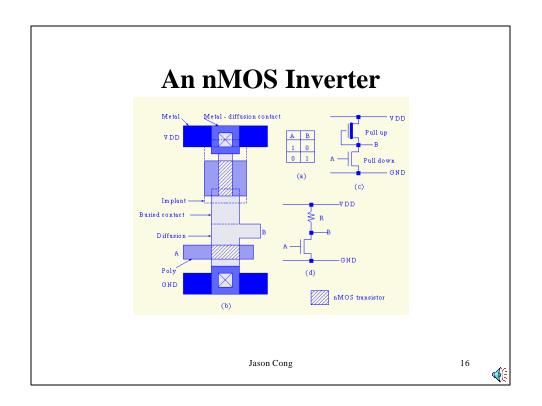

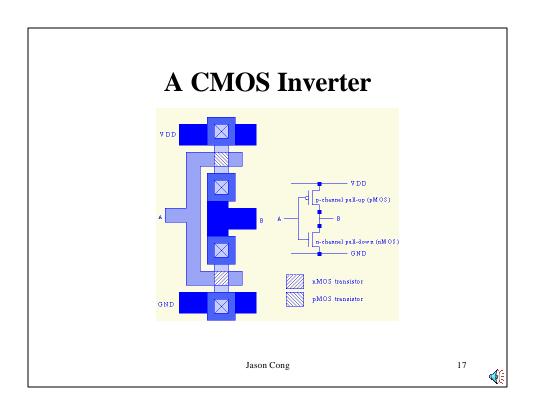

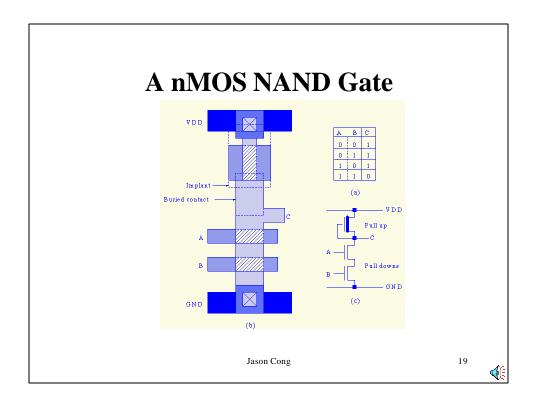

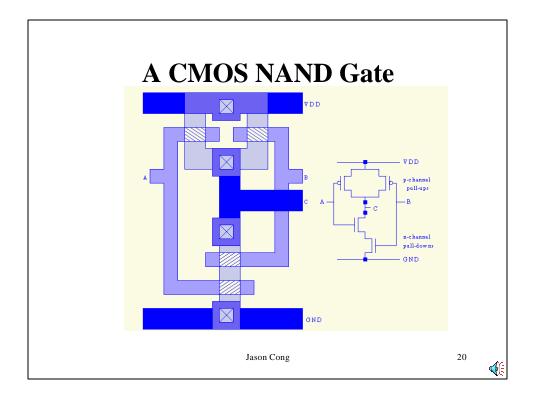

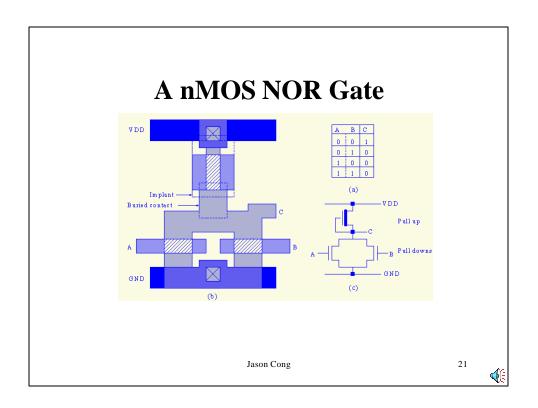

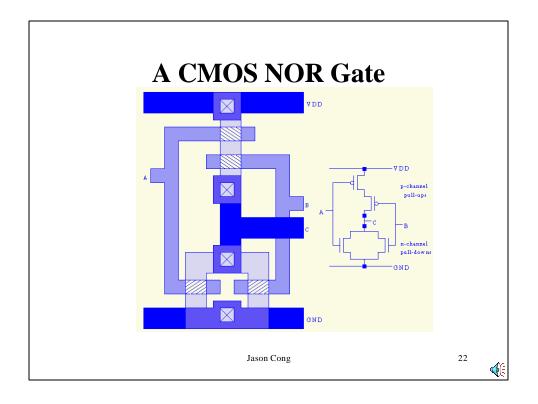

## **Layout of Basic Devices**

- nMOS Inverter

- **☼ CMOS Inverter**

- nMOS NAND Gate

- **SOLUTION** CMOS NAND Gate

- on nMOS NOR Gate

- **SOLUTION** CMOS NOR Gate

Complicated devices are constructed by using basic devices

Jason Cong

15

## Comparison of CMOS and MOS Characteristics

| CMOS                                                            | MOS                                                                                  |

|-----------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Zero static power dissipation                                   | Power is dissipated in the circuit with output of gate at "0"                        |

| Power dissipated during logic transition                        | Power dissipated during logic transition                                             |

| Requires 2N devices for N inputs for complementary static gates | Requires (N+1) devices for N inputs                                                  |

| CMOS encourages regular layout styles                           | Depletion, load and different<br>driver transistors create<br>irregularity in layout |

Jason Cong

**4**

18

## **Additional Fabrication Factors**

- 9 Scaling

- Parasitic Effects

- Yield Statistics and Fabrication Costs

- Delay Computation

- Solution Noise and Crosstalk

- **9** Power Dissipation

Jason Cong

23

# **Scaling and Parasitic Effects**

The process of shrinking the layout, in which every dimension is multiplied by a factor is called *scaling*

| Parameter                                 | Full scaling | CV scaling |

|-------------------------------------------|--------------|------------|

| Dimensions: width, length, oxid thickness | 1/s          | 1/s        |

| Voltage: power, threshold                 | 1/s          | 1          |

| Gate capacitance                          | 1/s          | 1/s        |

| Current                                   | 1/s          | S          |

| Propagation delay                         | 1/s          | 1/s²       |

Parasitic effects includes the stray capacitance, the capacitance between the signal paths and ground, and the inherent capacitance of the MOS transistor

Jason Cong

24

## **Integrated Circuit Costs**

Die cost = Wafer cost

Dies per Wafer \* Die yield

Dies per wafer =  $\frac{p * (Wafer\_diam / 2)^2}{Die Area}$  -  $\frac{p * Wafer\_diam}{\ddot{0} 2 * Die Area}$  - Test dies » Wafer Area Die Area

Die Yield = Wafer yield

{ 1+ Defects\_per\_unit\_area \* Die\_Area a

Die Cost is going roughly with (die area)<sup>3</sup> or (die area)<sup>4</sup>

Jason Cong

25

#### Die Yield

#### **Raw Dice Per Wafer**

| wafer diameter | d          | ie area ( | mm²) |     |     |     |

|----------------|------------|-----------|------|-----|-----|-----|

|                | <u>100</u> | 144       | 196  | 256 | 324 | 400 |

| 6"/15cm        | 139        | 90        | 62   | 44  | 32  | 23  |

| 8"/20cm        | 265        | 177       | 124  | 90  | 68  | 52  |

| 10"/25cm       | 431        | 290       | 206  | 153 | 116 | 90  |

| die yield      | 23%        | 19%       | 16%  | 12% | 11% | 10% |

typical CMOS process: α =2, wafer yield=90%, defect density=2/cm2, 4 test sites/wafer

#### **Good Dice Per Wafer (Before Testing!)**

| 6"/15cm  | 31 | 16 | 9  | 5  | 3  | 2 |

|----------|----|----|----|----|----|---|

| 8"/20cm  | 59 | 32 | 19 | 11 | 7  | 5 |

| 10"/25cm | 96 | 53 | 32 | 20 | 13 | 9 |

typical cost of an 8", 4 metal layers, 0.5um CMOS wafer: ~\$2000

Jason Cong

26

## **Real World Examples**

| Chip       | Metal  | Line  | Wafer  | Defect  | Area   | Dies/ | Yield | Die Cost |

|------------|--------|-------|--------|---------|--------|-------|-------|----------|

|            | layers | width | cost   | $/cm^2$ | $mm^2$ | wafer |       |          |

| 386DX      | 2      | 0.90  | \$900  | 1.0     | 43     | 360   | 71%   | \$4      |

| 486DX2     | 3      | 0.80  | \$1200 | 1.0     | 81     | 181   | 54%   | \$12     |

| PowerPC 60 | 01 4   | 0.80  | \$1700 | 1.3     | 121    | 115   | 28%   | \$53     |

| HP PA 710  | 0 3    | 0.80  | \$1300 | 1.0     | 196    | 66    | 27%   | \$73     |

| DEC Alpha  | 3      | 0.70  | \$1500 | 1.2     | 234    | 53    | 19%   | \$149    |

| SuperSPAR  | .C 3   | 0.70  | \$1700 | 1.6     | 256    | 48    | 13%   | \$272    |

| Pentium    | 3      | 0.80  | \$1500 | 1.5     | 296    | 40    | 9%    | \$417    |

From "Estimating IC Manufacturing Costs," by Linley Gwennap, Microprocessor Report, August 2, 1993, p. 15

Jason Cong

27

### **Other Costs**

IC cost = Die cost + Testing cost + Packaging cost

Final test yield

Packaging Cost: depends on pins, heat dissipation

| Chip        | Die<br>cost | Package<br>pins type cost |     |      | Test &<br>Assembly | Total |

|-------------|-------------|---------------------------|-----|------|--------------------|-------|

| 386DX       | \$4         | 132                       | QFP | \$1  | \$4                | \$9   |

| 486DX2      | \$12        | 168                       | PGA | \$11 | \$12               | \$35  |

| PowerPC 601 | <b>\$53</b> | 304                       | QFP | \$3  | \$21               | \$77  |

| HP PA 7100  | \$73        | 504                       | PGA | \$35 | \$16               | \$124 |

| DEC Alpha   | \$149       | 431                       | PGA | \$30 | \$23               | \$202 |

| SuperSPARC  | \$272       | 293                       | PGA | \$20 | \$34               | \$326 |

| Pentium     | \$417       | 273                       | PGA | \$19 | \$37               | \$473 |

Jason Cong

28

## **RC Parasitic Parameters**

$$R = \frac{rl_c}{h_c W_c}$$

$\pmb{R} = \frac{r \pmb{l}_c}{\pmb{h}_c \, W_c}$  r=resistivity,  $w_c$ ,  $\pmb{h}_c$ , and  $\pmb{l}_c$  are width, thickness and length of the conductor.

R=resistance of a uniform slab of conducting material.

$$C = \underbrace{\mathring{\text{e}}}_{\ddot{\text{e}}}^{1.15}(\frac{W_c}{t_o}) + 2.80(\frac{h_c}{t_o})^{0.222} + \underbrace{\mathring{\text{e}}}_{\ddot{\text{e}}}^{\dot{\text{e}}}0.06(\frac{W_c}{t_o}) + 1.66(\frac{h_c}{t_o}) - 0.14(\frac{h_c}{t_o})^{0.222} \underbrace{\mathring{\text{u}}}_{\ddot{\text{u}}}(\frac{t_o}{W_{cc}})^{1.34} \underbrace{\mathring{\text{u}}}_{\ddot{\text{u}}}^{\dot{\text{u}}} e_s \, e_0 \, l_c$$

C=capacitance of the conductor,  $w_{ic}$ = spacing of chip interconnections,

$t_0$ = thickness of the oxide,  $e_s$ = permittivity of free space,  $e_{\theta}$ = dielectric constant of the insulator

Jason Cong

29

## **Noise Crosstalk**

Noise principally stems from capacitive and inductive coupling.

One of the forms of noise is crosstalk, which is a result of mutual capacitance and inductance between neighboring lines

Jason Cong

30

## **Power Dissipation**

- Temperature must be as uniform as possible over the entire chip surface.

- Heat generated must be efficiently removed from the chip surface

- A CMOS gate uses 0.003nW/MHz/gate in 'off' state and 0.8 mW/MHz/gate during its operation.

- A ECL system uses 25 mW/gate irrespective of state and operating frequency

Jason Cong

31

## **Summary**

- The three types of materials are insulators, conductors and semiconductors

- A VLSI chip consists of several layers of different materials on a silicon wafer.

- Seach layer is defined by a mask

- © VLSI fabrication process patterns each layer using a mask

- © Complex VLSI circuits can be developed using basic VLSI devices

- © Design rules must be followed to allow proper fabrication

- Several factors such as scaling, parasitic effects, yield statistics and fabrication costs, delay computation, noise and crosstalk and power dissipation play a key role in fabrication of VLSI chips

Jason Cong

32