# CMPEN 411 VLSI Digital Circuits Spring 2012

**Lecture 13: Designing for Low Power**

[Adapted from Rabaey's *Digital Integrated Circuits*, Second Edition, ©2003 J. Rabaey, A. Chandrakasan, B. Nikolic]

#### **Review: Designing Fast CMOS Gates**

- Transistor sizing

- Progressive transistor sizing

- fet closest to the output is smallest of series fets

- Transistor ordering

- put latest arriving signal closest to the output

- Logic structure reordering

- replace large fan-in gates with smaller fan-in gate network

- Logical effort

- Buffer (inverter) insertion

- separate large fan-in from large C<sub>1</sub> with buffers

- uses buffers so that the path delay is minimized

#### **Why Power Matters**

- Packaging costs

- Power supply rail design

- Chip and system cooling costs

- Noise immunity and system reliability

- Battery life (in portable systems)

- Environmental concerns

- Office equipment accounted for 5% of total US commercial energy usage in 1993

- Energy Star compliant systems

#### Why worry about power? - Power Dissipation

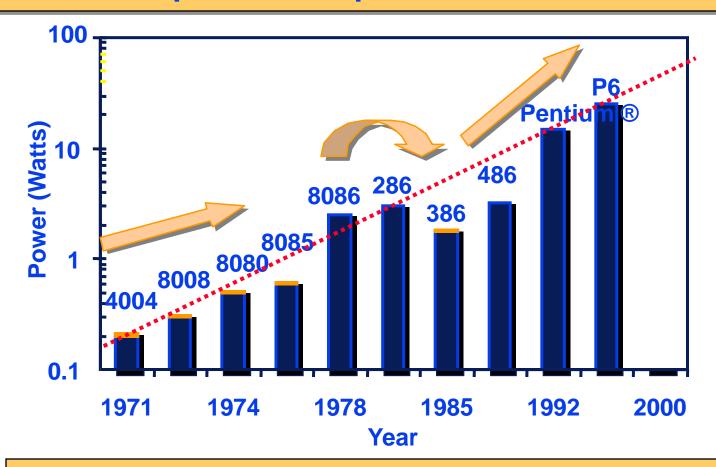

#### Lead microprocessors power continues to increase

Power delivery and dissipation will be prohibitive

Source: Borkar, De Intel®

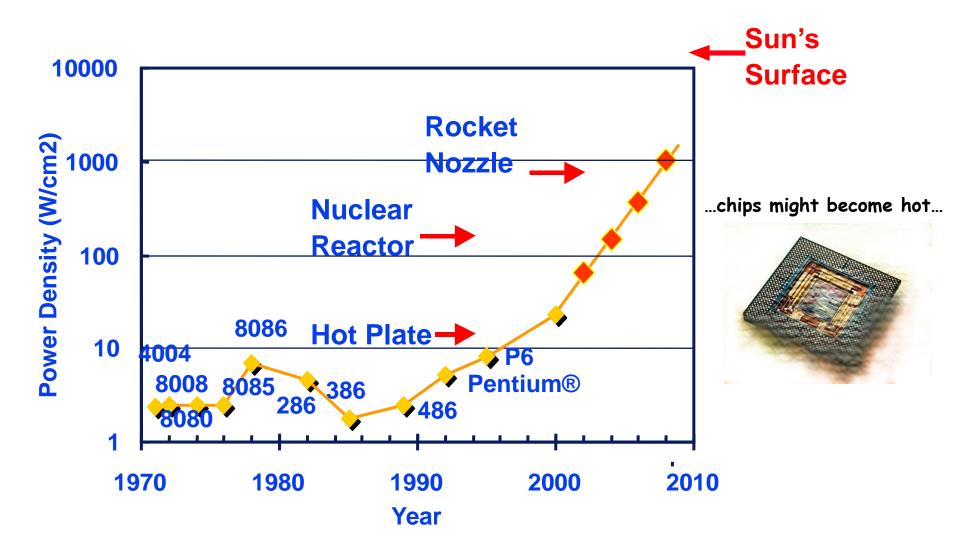

#### Why worry about power? - Chip Power Density

Source: Borkar, De Intel®

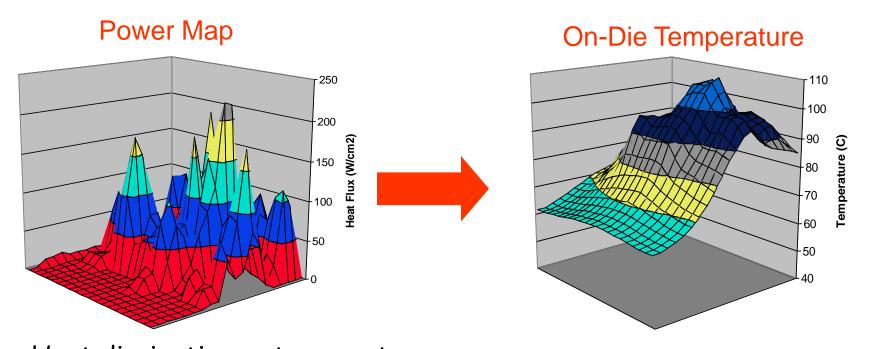

#### **Chip Power Density Distribution => Heat**

- Heat dissipation => temperature,

higher power density => higher temperature

- Power density is not uniformly distributed across the chip

Intel Pentium 4: (0.18 um) 64 W @ 217 mm²

Intel Pentium 4: (90 nm) 103W @ 112 mm<sup>2</sup>

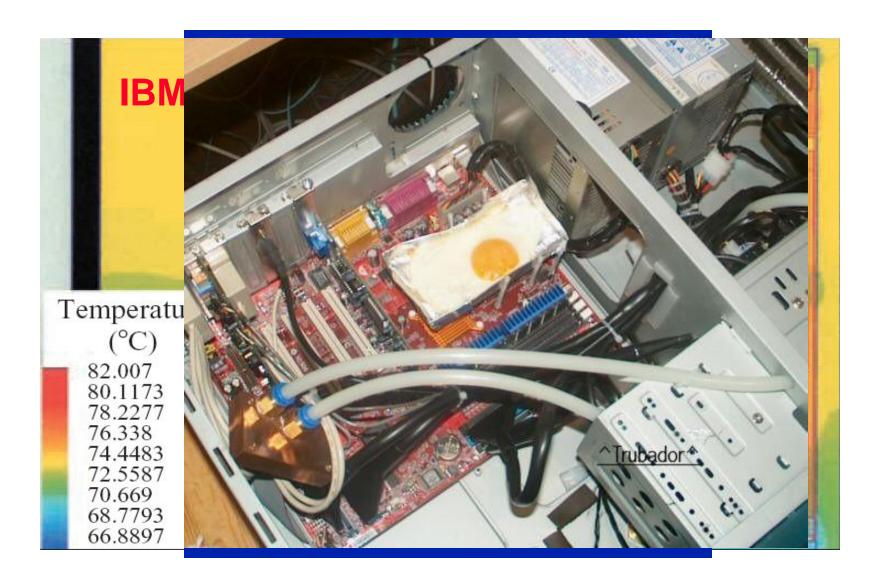

# Examples

# Apple Power G5

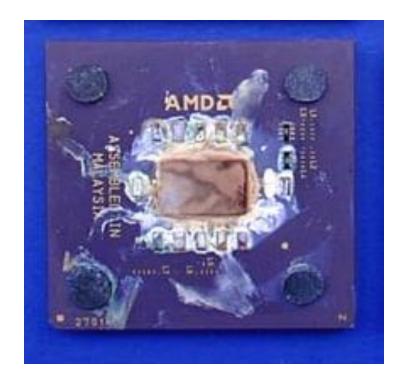

# What happens when the CPU cooler is removed?

www.tomshardware.de www.tomshardware.com

#### Power and temperature are BAD

#### and can be EVIL

**Source: Tom's Hardware Guide** http://www6.tomshardware.com/cpu/01q3/010917/heatvideo-01.html

#### **Power and Energy Figures of Merit**

- Power consumption in Watts

- determines battery life in hours

- Peak power

- determines power ground wiring designs

- sets packaging limits

- impacts signal noise margin and reliability analysis

- □ Energy efficiency in Joules

- rate at which power is consumed over time

- Energy = power \* delay

- Joules = Watts \* seconds

- lower energy number means less power to perform a computation at the same frequency

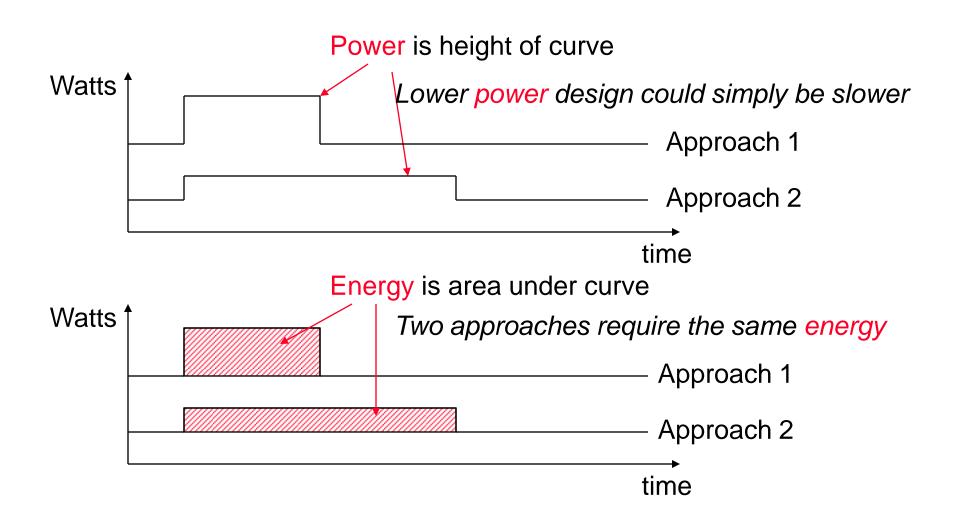

#### **Power versus Energy**

#### PDP and EDP

- □ Power-delay product (PDP) =  $P_{av} * t_p = (C_L V_{DD}^2)/2$

- PDP is the average energy consumed per switching event (Watts \* sec = Joule)

- lower power design could simply be a slower design

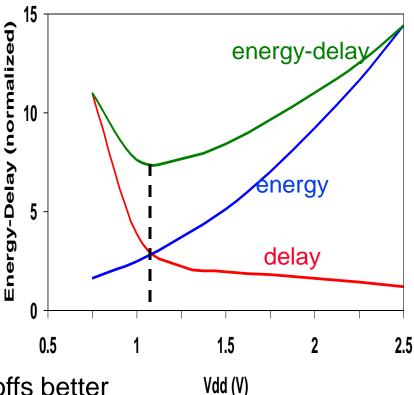

- □ Energy-delay product (EDP) = PDP \* t<sub>p</sub> = P<sub>av</sub> \* t<sub>p</sub><sup>2</sup>

- EDP is the average energy consumed multiplied by the computation time required

- takes into account that one can trade increased delay for lower energy/operation (e.g., via supply voltage scaling that increases delay, but decreases energy consumption)

allows one to understand tradeoffs better

#### **Understanding Tradeoffs**

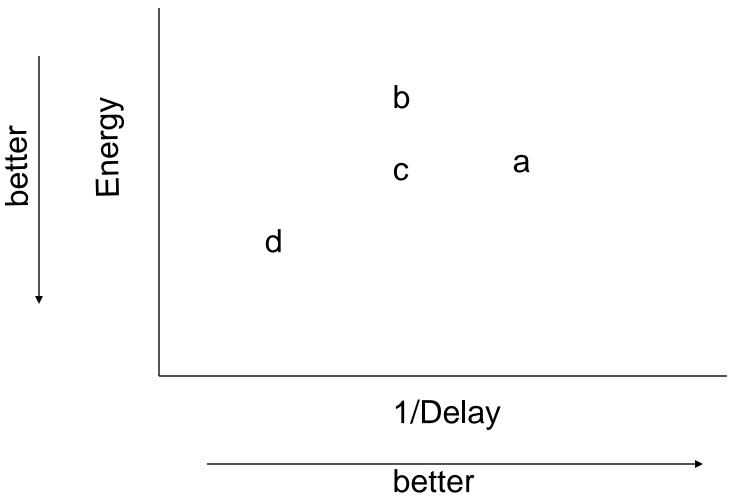

■ Which design is the "best" (fastest, coolest, both) ?

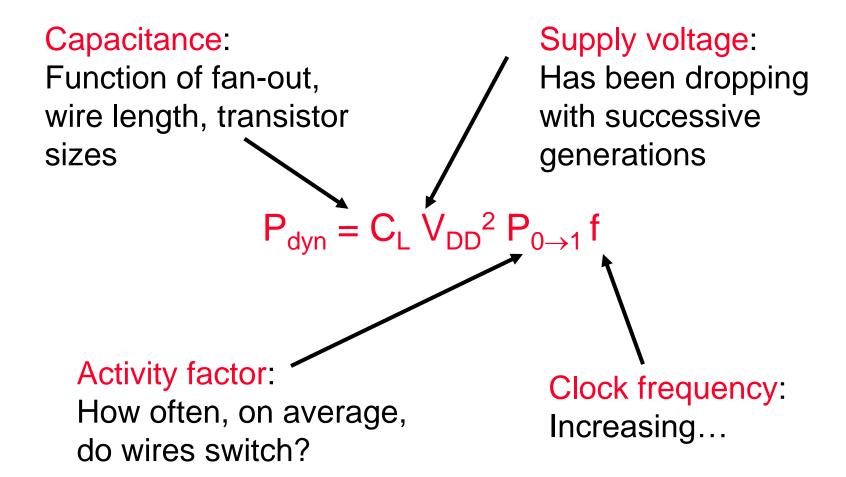

#### **CMOS Power Equations**

$$P = C_L V_{DD}^2 f + t_{sc} V_{DD} I_{peak} f + V_{DD} I_{leak}$$

Dynamic power

Short-circuit power

Leakage power

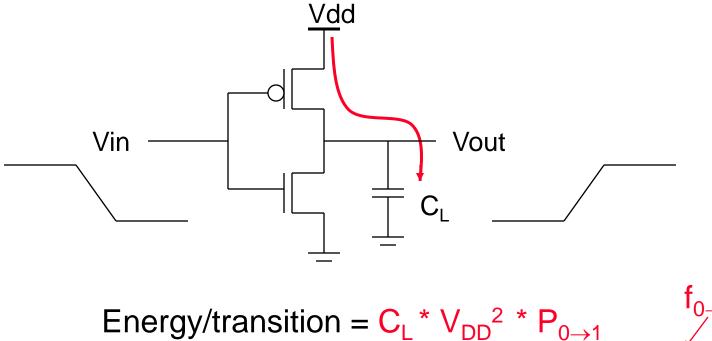

#### **Dynamic Power Consumption**

$$P_{dyn}$$

= Energy/transition \* f =  $C_L$  \*  $V_{DD}^2$  \*  $P_{0\rightarrow 1}$  \* f

$$P_{dyn} = C_{EFF} * V_{DD}^2 * f$$

where  $C_{EFF} = P_{0\rightarrow 1} C_L$

Not a function of transistor sizes!

Data dependent - a function of switching activity!

#### **Lowering Dynamic Power**

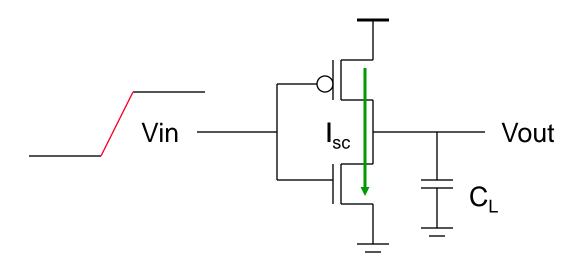

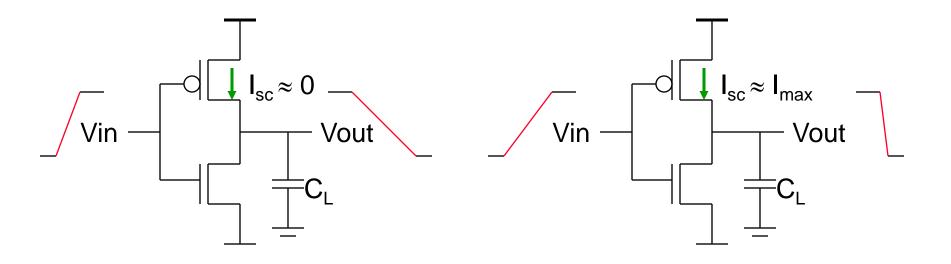

#### **Short Circuit Power Consumption**

Finite slope of the input signal causes a direct current path between  $V_{DD}$  and GND for a short period of time during switching when both the NMOS and PMOS transistors are conducting.

#### **Short Circuit Currents Determinates**

$$P_{sc} = t_{sc} V_{DD} I_{peak} f_{0\rightarrow 1}$$

- Duration and slope of the input signal, t<sub>sc</sub>

- I<sub>peak</sub> determined by

- the saturation current of the P and N transistors which depend on their sizes, process technology, temperature, etc.

- strong function of the ratio between input and output slopes

- a function of C<sub>1</sub>

### Impact of C<sub>L</sub> on P<sub>sc</sub>

Large capacitive load

**Small** capacitive load

Output fall time significantly larger than input rise time.

Output fall time substantially smaller than the input rise time.

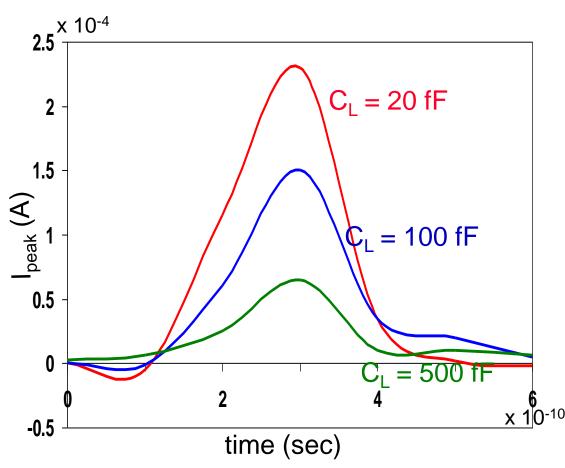

# I<sub>peak</sub> as a Function of C<sub>I</sub>

When load capacitance is small, I<sub>peak</sub> is large.

Short circuit dissipation is minimized by matching the rise/fall times of the input and output signals - slope engineering.

500 psec input slope

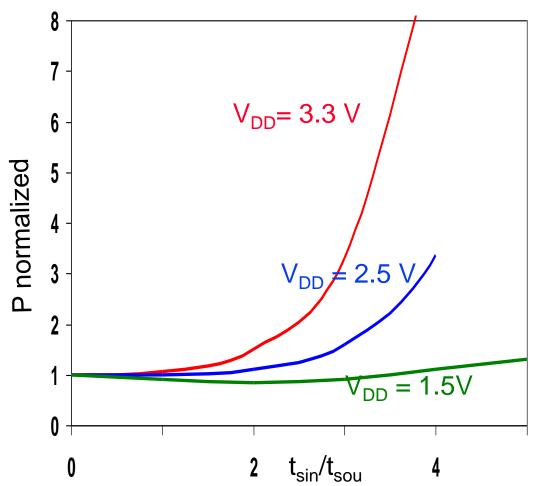

#### P<sub>sc</sub> as a Function of Rise/Fall Times

When load capacitance is small ( $t_{sin}/t_{sout} > 2$  for  $V_{DD} > 2V$ ) the power is dominated by  $P_{sc}$

If  $V_{DD} < V_{Tn} + |V_{Tp}|$  then  $P_{sc}$  is eliminated since both devices are never on at the same time.

$W/L_p = 1.125 \mu m/0.25 \mu m$   $W/L_n = 0.375 \mu m/0.25 \mu m$  $C_L = 30 \text{ fF}$

normalized wrt zero input rise-time dissipation

Sp12 CMPEN 411 L13 S.23

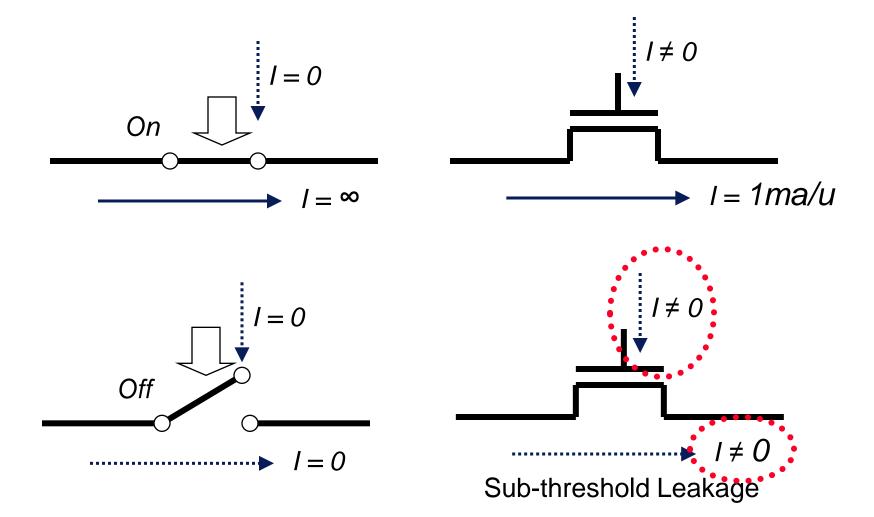

#### **Is Transistor a Good Switch?**

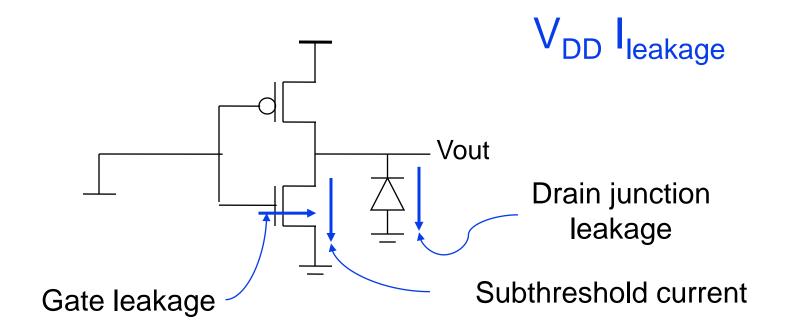

#### **Leakage (Static) Power Consumption**

Sub-threshold current is the dominant factor.

#### Leakage as a Function of V<sub>T</sub>

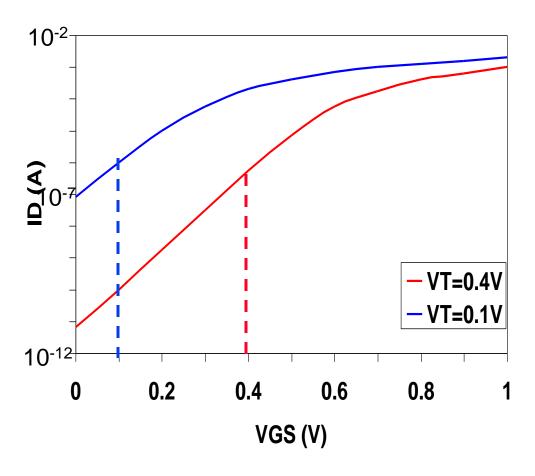

Continued scaling of supply voltage and the subsequent scaling of threshold voltage will make subthreshold conduction a dominate component of power dissipation.

□ An 90mV/decade V<sub>T</sub> roll-off - so each 270mV increase in V<sub>T</sub> gives 3 orders of magnitude reduction in leakage (but adversely affects performance)

#### TSMC Processes Leakage and V<sub>T</sub>

|                                       | CL018<br>G | CL018<br>LP | CL018<br>ULP | CL018<br>HS | CL015<br>HS | CL013<br>HS |

|---------------------------------------|------------|-------------|--------------|-------------|-------------|-------------|

| $V_{dd}$                              | 1.8 V      | 1.8 V       | 1.8 V        | 2 V         | 1.5 V       | 1.2 V       |

| T <sub>ox</sub> (effective)           | 42 Å       | 42 Å        | 42 Å         | 42 Å        | 29 Å        | 24 Å        |

| L <sub>gate</sub>                     | 0.16 μm    | 0.16 μm     | 0.18 μm      | 0.13 μm     | 0.11 μm     | 0.08 μm     |

| I <sub>DSat</sub> (n/p)<br>(μΑ/μm)    | 600/260    | 500/180     | 320/130      | 780/360     | 860/370     | 920/400     |

| I <sub>off</sub> (leakage)<br>(ρΑ/μm) | 20         | 1.60        | 0.15         | 300         | 1,800       | 13,000      |

| V <sub>Tn</sub>                       | 0.42 V     | 0.63 V      | 0.73 V       | 0.40 V      | 0.29 V      | 0.25 V      |

| FET Perf.<br>(GHz)                    | 30         | 22          | 14           | 43          | 52          | 80          |

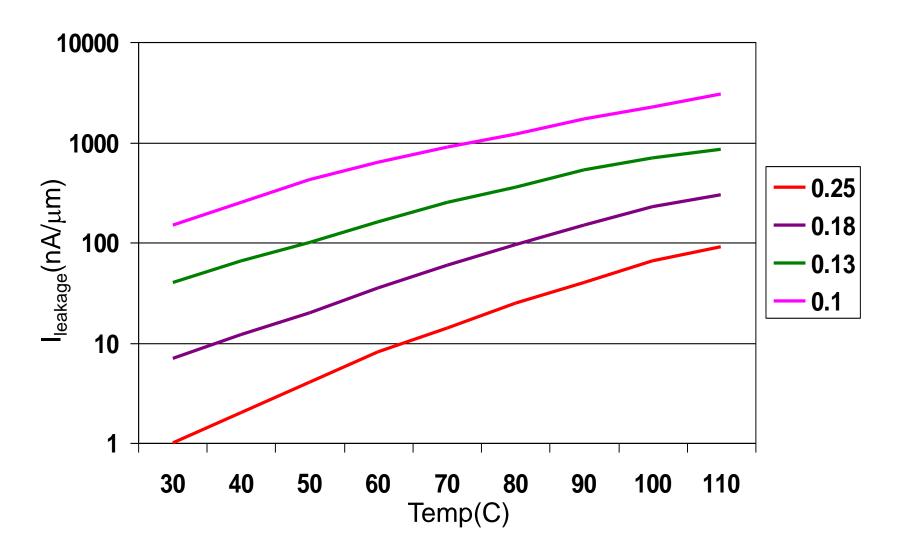

#### **Exponential Increase in Leakage Currents**

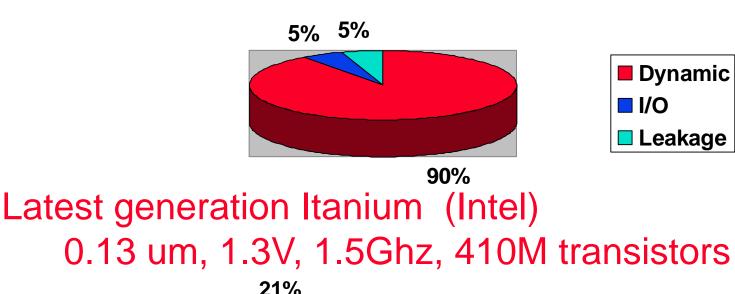

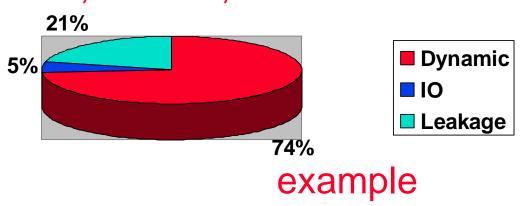

#### **Itanium example**

Itanium 2 (Intel) 0.18 um, 1.5V, 1Ghz, 221M transistors

#### **Next Lecture**

|                      | Consta<br>Throughput                                                        |                                                                                | Variable<br>Throughput/Latency |                                                   |  |

|----------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------|--|

| Energy               | Design Time                                                                 | Non-active Modules                                                             |                                | Run Time                                          |  |

| Active<br>(Dynamic)  | Logic design<br>Reduced V <sub>dd</sub><br>TSizing<br>Multi-V <sub>dd</sub> | Clock (                                                                        | Gating                         | DFS, DVS<br>(Dynamic Freq,<br>Voltage<br>Scaling) |  |

| Leakage<br>(Standby) | Multi-V <sub>T</sub><br>Stack effect<br>Pin ordering                        | Sleep Transistors  Multi-V <sub>dd</sub> Variable V <sub>T</sub> Input control |                                | Variable V <sub>T</sub>                           |  |