# Design more features before the next re-spin with Altera PLDs

# Altera in portable entertainment

The MAX® II device helps us stay competitive in the extremely pricesensitive consumer electronics market. We have been able to implement digital signal processing more economically than with alternative solutions and reduce costs at the manufacturing level.

> Mike Chai Senior Vice President of R&D LeapFrog

Your customers demand light-weight mobility and more functionality than ever before. Not only do you have to design all the latest features into your products, but you have to do it in an ever-smaller board space, use less power, and integrate into a wide array of other technologies to stay ahead of the curve. Whether you're designing for media players, edutainment toys, handheld games, GPS navigators, or another portable device, Altera delivers flexible programmable solutions that will get you to market faster and reduce your total cost of development.

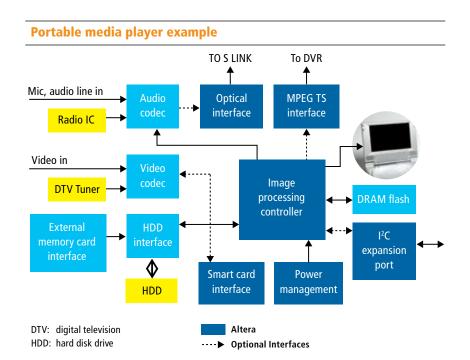

# Altera in portable media players

A new generation of portable media players is here. Altera® solutions make it easy for you to deliver all the functionality this new generation demands. Your customers will be able to listen to music, watch videos, and view pictures, functionality that's integrated into one product that they can carry in the palm of their hand. Envision the future with wireless media sharing, image and video capture, and gaming capabilities. Because Altera is at the forefront of portable media player design, we'll be able to help you deliver these kind of features and more, only faster.

In a typical portable media player system, the central functional block is the image processing controller. The basic functions required for the image processing controller can be implemented either in an ASIC, ASSP, or DSP device. A companion Altera programmable logic device (PLD) can also be incorporated into the basic design for feature enhancements. Because PLDs are reprogrammable, this companion device allows you to differentiate products and get them to market faster than designers who use ASICs, ASSPs, or DSP devices alone.

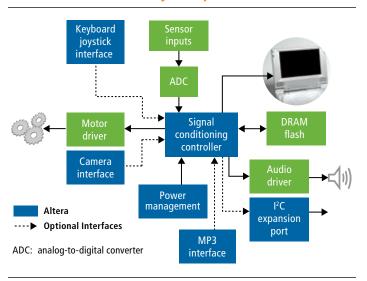

# Altera in edutainment toys

Educating children while keeping them entertained is the objective of portable edutainment toys. In a typical portable edutainment toy system, the central functional block is the signal conditioning controller. The signal conditioning controller positions the motor, based on inputs from an external sensor. It processes and loads images to the display panel, handles audio processing functions, such as audio tone synthesis, and manages external audio sources. These three functions are unique to an edutainment toy system specification, and a PLD gives you maximum design flexibility, low risk, and fastest time to market in your designs. Similar to the portable media player application, PLDs are ideal for interface bridging, I/O expansion, power management, voltage-level shifting, DSP configuration, and clock generation functions.

# Portable edutainment toy example

#### Portable entertainment features and benefits

| Fortable entertainment reatures and benefits                             |                  |                          |                                                                                                                                                                                 |                                                                                      |

|--------------------------------------------------------------------------|------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Functions                                                                | MAX IIZ<br>CPLDs | Cyclone®<br>Series FPGAs | Features                                                                                                                                                                        | Benefits                                                                             |

| Power management                                                         | ~                |                          | Industry's lowest dynamic and standby power consumption                                                                                                                         | Adapts to application for optimal power management                                   |

| Video and image processing                                               |                  | ~                        | Abundant memory and multipliers for video processing applications                                                                                                               | Image processing, quality enhancement                                                |

| Signal conditioning controller                                           | ~                | ~                        | MAX IIZ CPLDs are lower cost than digital signal processors; Cyclone series FPGAs have configurable soft processor for custom-fit solutions                                     | Cost and board space reduction                                                       |

| LCD timing controller                                                    |                  | ~                        | Built-in LVDS, reduced swing differential signaling (RSDS), mini-LVDS, point-to-point differential signaling (PPDS) display column driver interfaces                            | Cost and board space reduction                                                       |

| Interface bridging                                                       | ~                | ~                        | Configurable I/O buffers with built-in interfaces for common I/O standards and external memory interfaces                                                                       | No extra components needed for interface bridging                                    |

| General purpose I/O (GPIO)<br>pin/I <sup>2</sup> C/system port expansion | ~                |                          | Adding more I/Os or system user I/F                                                                                                                                             | Flexibility and expandability<br>at minimal cost, highest I/O<br>per mm <sup>2</sup> |

| Data format conversion                                                   |                  | ~                        | High bandwidth memory for fast data format conversion                                                                                                                           | Fast performance, less timing delay                                                  |

| ASSP-function complement                                                 | V                | V                        | Add features to complement ASSP: smart card, game stick I/F                                                                                                                     | Expandability, time to market                                                        |

| Security                                                                 | ~                |                          | Store encryption key in user flash memory (UFM)                                                                                                                                 | Personal content protection                                                          |

| Voltage level shifter                                                    | V                |                          | On-chip voltage regulator                                                                                                                                                       | No need for additional voltage regulator                                             |

| Clock generation                                                         | ~                | ~                        | MAX IIZ UFM interface clock-sync and power-up sequencing; Cyclone series phase-locked loops (PLLs) can generate multiple independent clocks from a single low-cost clock source | Internal clock generation, no<br>need for additional clock                           |

# Visit us at www.altera.com/consumer for more information.

### Altera Corporation

101 Innovation Drive San Jose, CA 95134

www.altera.com

## Altera European Headquarters

Holmers Farm Way High Wycombe Buckinghamshire HP12 4XF United Kingdom Telephone: (44) 1494 602000

### Altera Japan Ltd.

Shinjuku i-Land Tower 32F 6-5-1, Nishi-Shinjuku Shinjuku-ku, Tokyo 163-1332 Japan Telephone: (81) 3 3340 9480

www.altera.co.jp

#### Altera International Ltd.

2102 Tower 6 The Gateway, Harbour City 9 Canton Road Tsimshatsui Kowloon Hong Kong Telephone: (852) 2945 7000 www.altera.com.cn

Copyright © 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected mera numerous U.S. and foreign patents and pending applications, mask work rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. December 2007; PDF.

88-0103-2.0