### DOUGLAS SELF

# AUDIO POWER AMPLIFIER DESIGN HANDBOOK

# Audio Power Amplifier Design Handbook

This book is dedicated to Julie, without whom it would not have happened.

# Audio Power Amplifier Design Handbook

Fifth Edition

Douglas Self

AMSTERDAM • BOSTON • HEIDELBERG • LONDON • NEW YORK • OXFORD PARIS • SAN DIEGO • SAN FRANCISCO • SINGAPORE • SYDNEY • TOKYO

Focal Press is an imprint of Elsevier

Focal Press is an imprint of Elsevier 30 Corporate Drive, Suite 400, Burlington, MA 01803, USA Linacre House, Jordan Hill, Oxford OX2 8DP, UK

First published 2009

Copyright © 2009, Douglas Self. Published by Elsevier Ltd. All rights reserved

The right of Douglas Self to be identified as the author of this work has been asserted in accordance with the Copyright, Designs and Patents Act 1988

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone (+44) (0) 1865 843830; fax (+44) (0) 1865 853333; email: permissions@elsevier.com. Alternatively visit the Science and Technology Books website at www.elsevierdirect.com/rights for further information

Notice

No responsibility is assumed by the publisher for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions or ideas contained in the material herein

#### British Library Cataloguing-in-Publication Data

Self, Douglas.

Audio power amplifier design handbook. – 5th ed. 1. Audio amplifiers—Design. 2. Power amplifiers—Design. I. Title 621.3'81535—dc22

#### Library of Congress Control Number: 2009920721

ISBN: 978-0-240-52162-6

For information on all Focal Press publications visit our website at www.focalpress.com

Printed and bound in the United States of America

$09\ 10\ 11\ 12 \quad 13\ 12\ 11\ 10\ 9\ 8\ 7\ 6\ 5\ 4\ 3\ 2\ 1$

### Working together to grow libraries in developing countries www.elsevier.com | www.bookaid.org | www.sabre.org

ELSEVIER BOOK AID Sabre Foundation

### **Contents**

| Acknowledgements                              | xviii |

|-----------------------------------------------|-------|

| Preface to fifth edition                      | xix   |

| Abbreviations                                 | xxi   |

| Chapter 1 Introduction and general survey     | 1     |

| The economic importance of power amplifiers   | 1     |

| Assumptions                                   | 1     |

| Origins and aims                              | 1     |

| The study of amplifier design                 |       |

| Misinformation in audio                       |       |

| Science and subjectivism                      | 6     |

| The subjectivist position                     | 6     |

| A short history of subjectivism               | 7     |

| The limits of hearing                         | 8     |

| Articles of faith: the tenets of subjectivism |       |

| The length of the audio chain                 |       |

| The implications                              |       |

| The reasons why                               |       |

| The implications                            | 16 |

|---------------------------------------------|----|

| The reasons why                             | 16 |

| The outlook                                 |    |

| Technical errors                            |    |

| The performance requirements for amplifiers |    |

| Safety                                      | 19 |

| Reliability                                 | 19 |

| Power output                                | 19 |

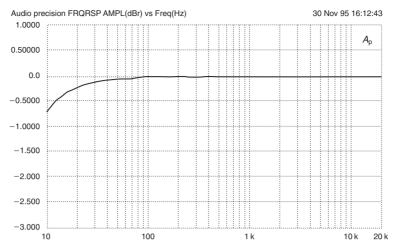

| Frequency response                          |    |

| Noise                                       | 20 |

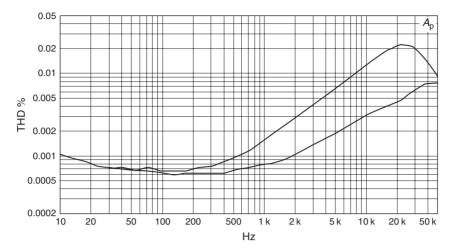

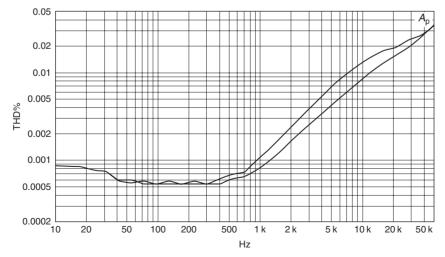

| Distortion                                  | 21 |

| Damping factor                              | 21 |

| Absolute phase                              | 23 |

| Amplifier formats                           | 24 |

|                                             |    |

| Chapter 2 Power amplifier architecture and negative feedback |    |

|--------------------------------------------------------------|----|

| Amplifier architectures                                      |    |

| The three-stage amplifier architecture                       |    |

| The two-stage amplifier architecture                         |    |

| The four-stage amplifier architecture                        |    |

| Power amplifier classes                                      |    |

| Class-A                                                      |    |

| Class-AB                                                     |    |

| Class-B                                                      |    |

| Class-C                                                      |    |

| Class-D                                                      |    |

| Class-E                                                      |    |

| Class-F                                                      |    |

| Class-G                                                      |    |

| Class-H                                                      |    |

| Class-S                                                      | 35 |

| Variations on Class-B                                        | 35 |

| Error-correcting amplifiers                                  | 35 |

| Non-switching amplifiers                                     |    |

| Current-drive amplifiers                                     |    |

| The Blomley principle                                        |    |

| Geometric mean Class-AB                                      |    |

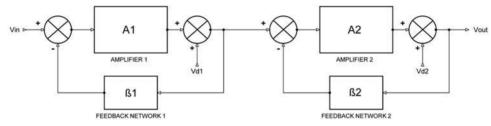

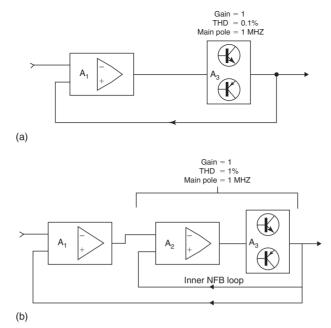

| Nested differentiating feedback loops                        |    |

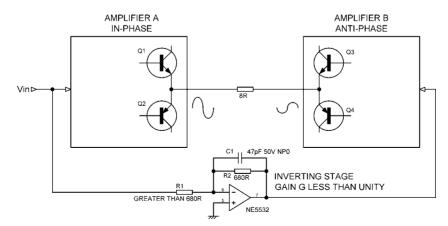

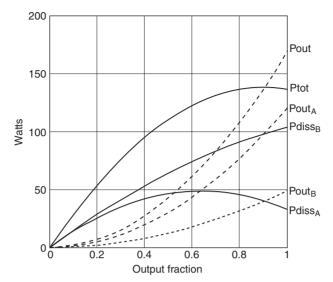

| Amplifier bridging                                           |    |

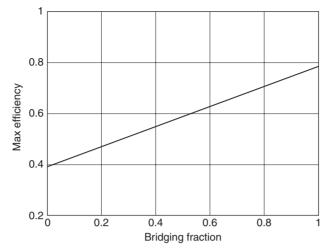

| Fractional bridging                                          |    |

| AC- and DC-coupled amplifiers                                | 41 |

| The advantages of AC-coupling                                | 41 |

| The advantages of DC-coupling                                | 42 |

| Negative feedback in power amplifiers                        | 44 |

| Some common misconceptions about negative feedback           | 48 |

| Amplifier stability and NFB                                  | 50 |

| Maximizing the NFB                                           |    |

| Overall feedback versus local feedback                       |    |

| Maximizing linearity before feedback                         | 60 |

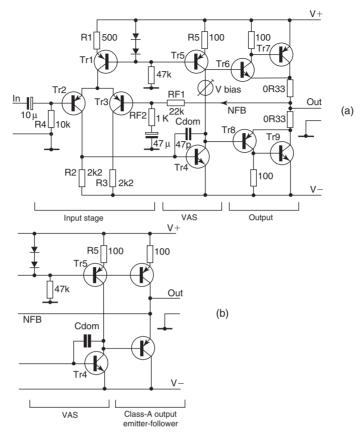

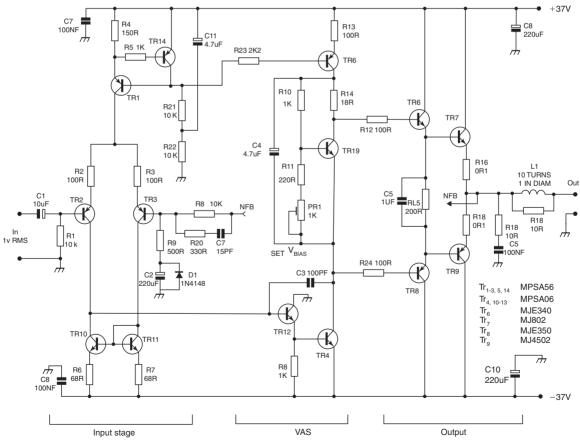

| Chapter 3 The general principles of power amplifiers |  |

|------------------------------------------------------|--|

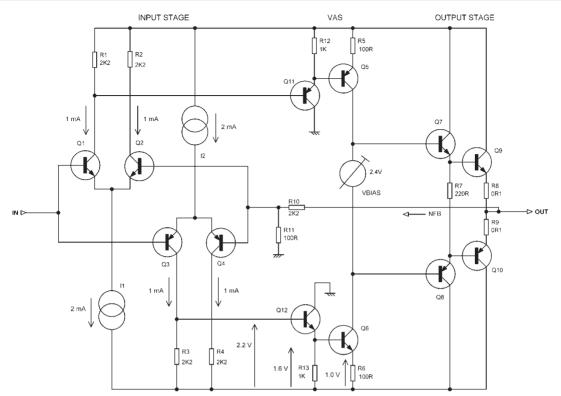

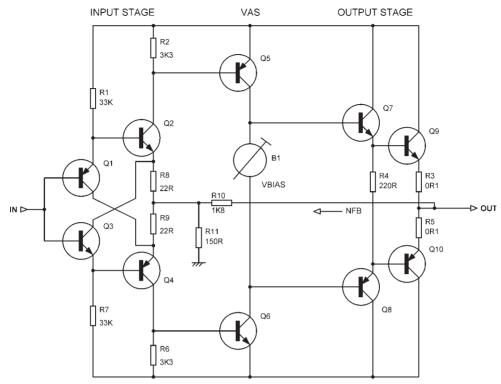

| How a generic amplifier works                        |  |

| The advantages of the conventional                   |  |

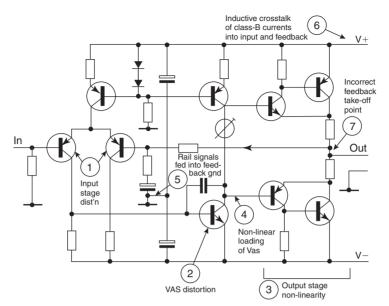

| The distortion mechanisms                            |  |

| Distortion 1: Input stage distortion                 |  |

| Distortion 2: VAS distortion                         |  |

| Distortion 3: Output stage distortion        | 66 |

|----------------------------------------------|----|

| Distortion 4: VAS-loading distortion         | 67 |

| Distortion 5: Rail-decoupling distortion     | 67 |

| Distortion 6: Induction distortion           | 67 |

| Distortion 7: NFB take-off distortion        | 67 |

| Distortion 8: Capacitor distortion           | 67 |

| Distortion 9: Magnetic distortion            |    |

| Distortion 10: Input current distortion      |    |

| Distortion 11: Premature overload protection |    |

| Nonexistent or negligible distortions        | 69 |

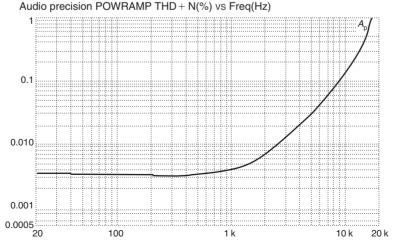

| The performance of a standard amplifier      |    |

| Open-loop linearity and how to determine it  |    |

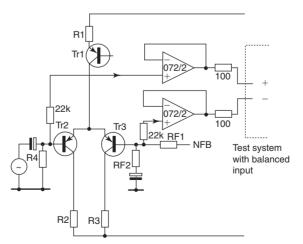

| Direct open-loop gain measurement            | 71 |

| Using model amplifiers                       | 72 |

| The concept of the Blameless amplifier       |    |

|                                              |    |

| Chapter 4 The input stage                      | 75  |

|------------------------------------------------|-----|

| The role of the input stage                    | 75  |

| Distortion from the input stage                | 75  |

| BJTs versus FETs for the input stage           | 77  |

| Advantages of the FET input stage              | 77  |

| Disadvantages of FET input stage               | 78  |

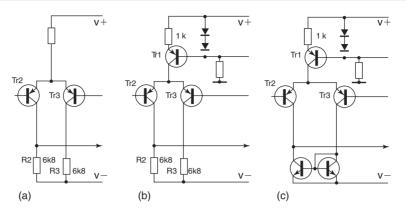

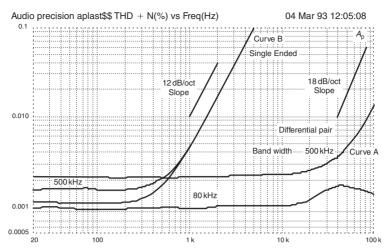

| Singleton input stage versus differential pair | 78  |

| The input stage distortion in isolation        | 79  |

| Input stage balance                            | 80  |

| The joy of current-mirrors                     | 82  |

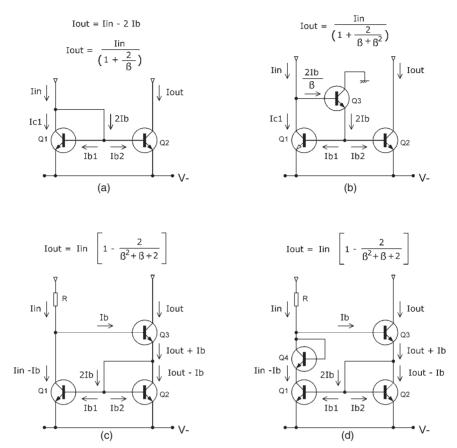

| Better current-mirrors                         |     |

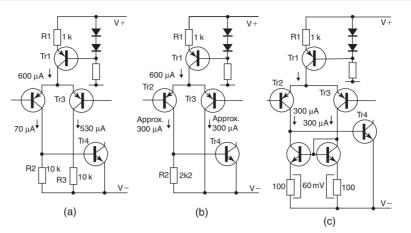

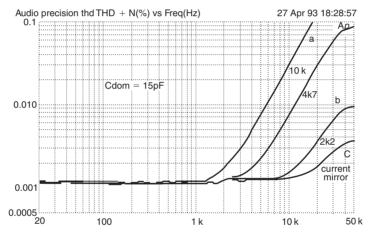

| Improving input stage linearity                | 85  |

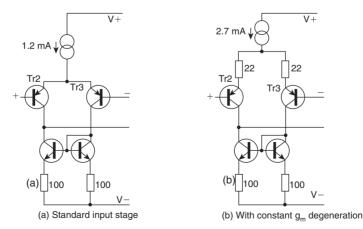

| Further improving input linearity              |     |

| Increasing the output capability               | 90  |

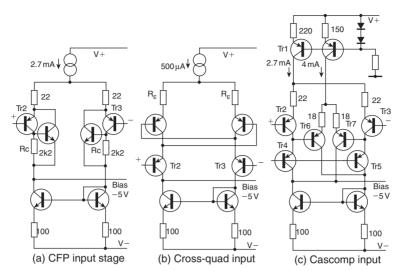

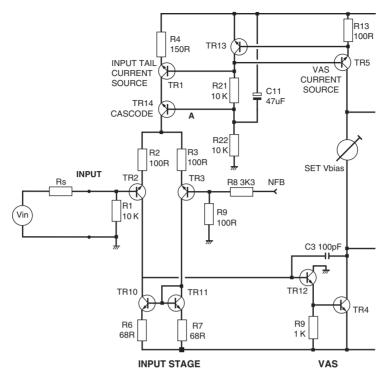

| Input stage cascode configurations             | 91  |

| Double input stages                            | 92  |

| Input stage common-mode distortion             | 92  |

| Input current distortion                       | 96  |

| Input stage noise and how to reduce it         | 104 |

| Noise sources in power amplifiers              | 107 |

| Noise in bipolar transistors                   | 108 |

| Reducing input transistor noise                | 112 |

| Offset and match: the DC precision issue       | 114 |

| The input stage and the slew rate              | 115 |

| Input stage conclusions                        | 116 |

| Chapter 5 The voltage-amplifier stage       |  |

|---------------------------------------------|--|

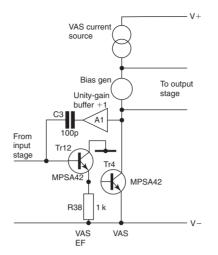

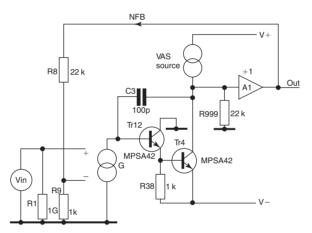

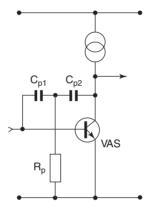

| Measuring VAS distortion in isolation       |  |

| VAS operation                               |  |

| VAS distortion                              |  |

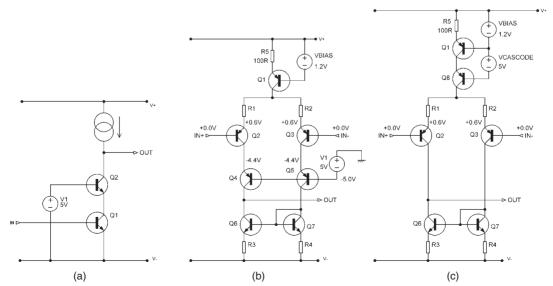

| Linearizing the VAS: active-load techniques |  |

| VAS enhancements                            |  |

| Some more VAS variations                    |  |

| VAS operating conditions                    |  |

| The importance of voltage drive             |  |

| The push–pull VAS                           |  |

| The high-current capability VAS             |  |

| Single input stages                         |  |

| Double input stages                         |  |

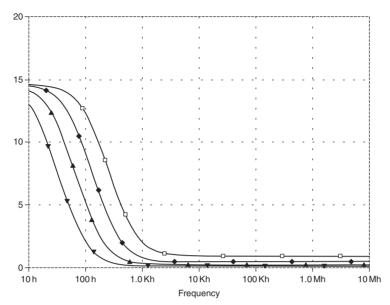

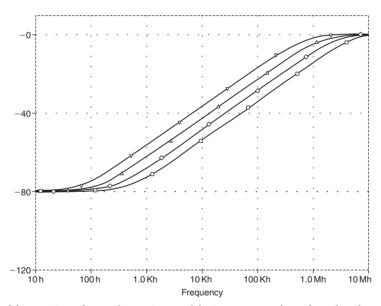

| Manipulating open-loop bandwidth            |  |

| Conclusions                                 |  |

| Chapter 6 The output stage                    |  |

|-----------------------------------------------|--|

| Classes and devices                           |  |

| The distortions of the output                 |  |

| Harmonic generation by crossover distortion   |  |

| Comparing output stages                       |  |

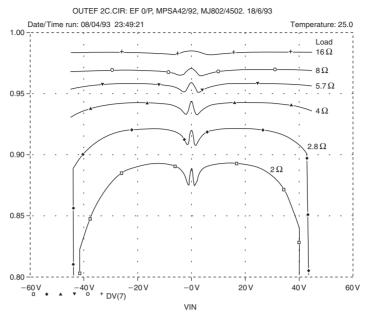

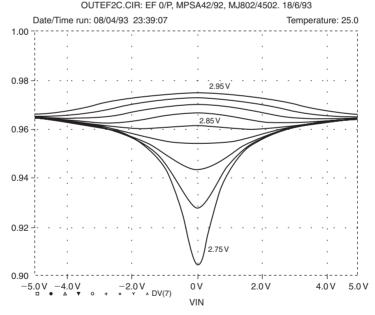

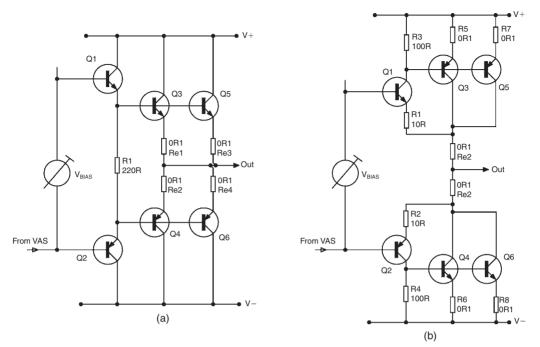

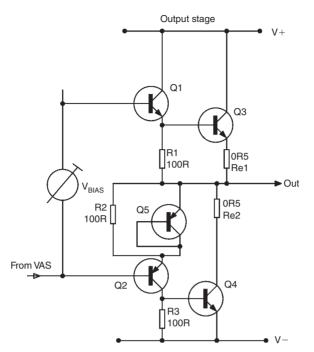

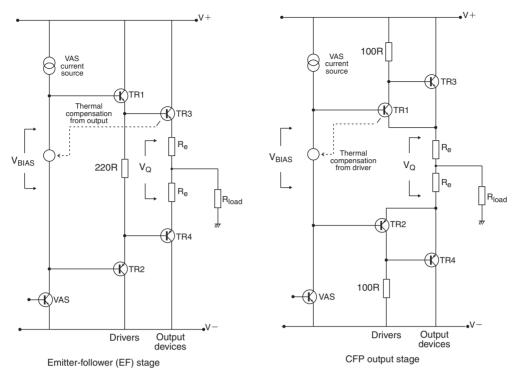

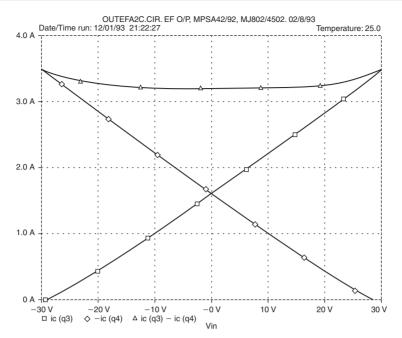

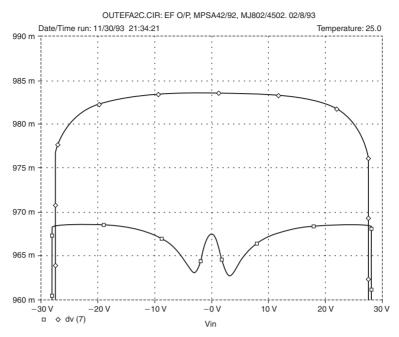

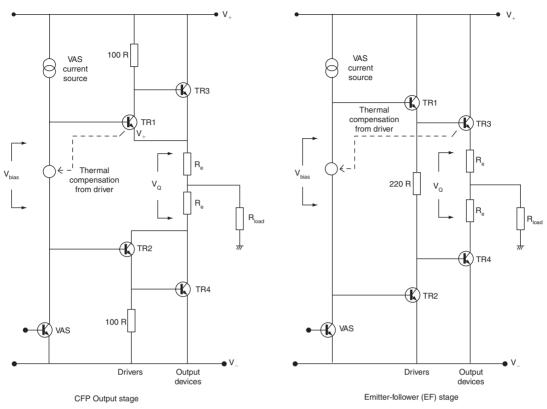

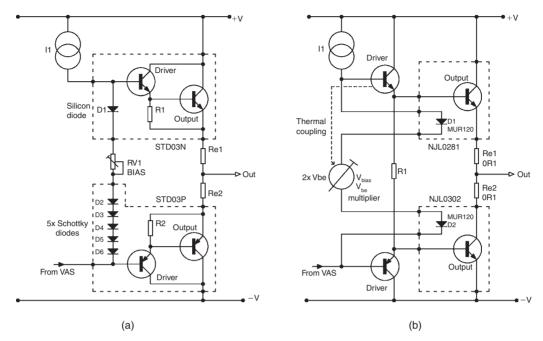

| The emitter-follower (EF) output              |  |

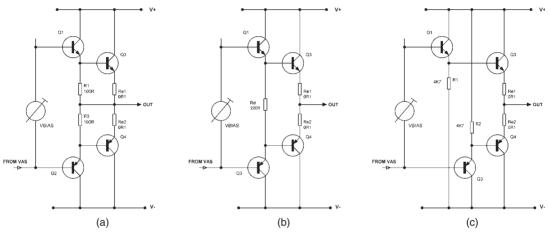

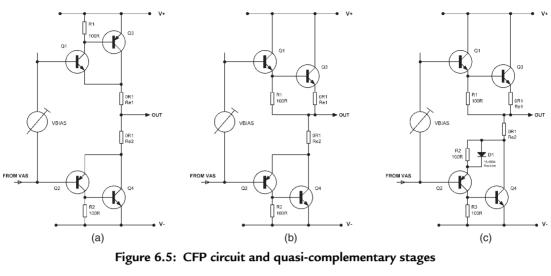

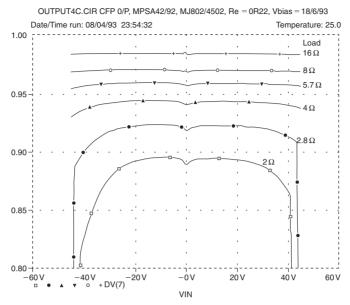

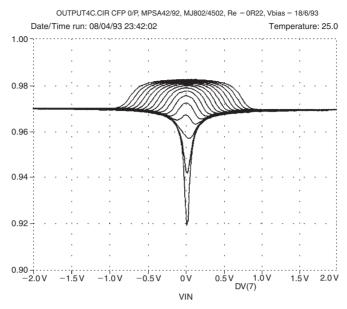

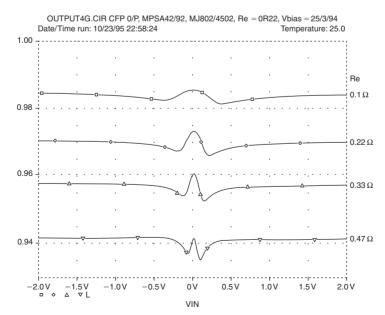

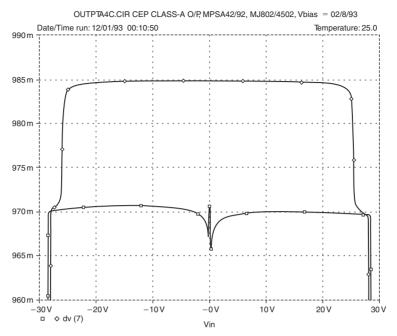

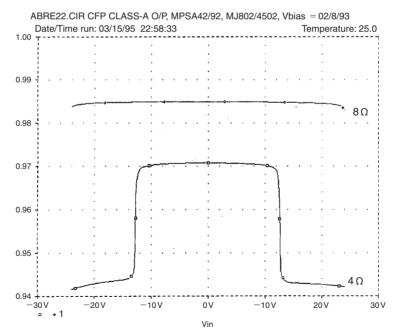

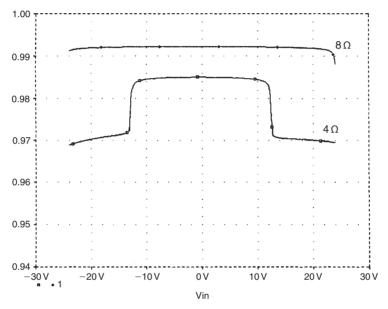

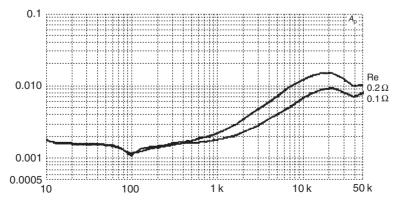

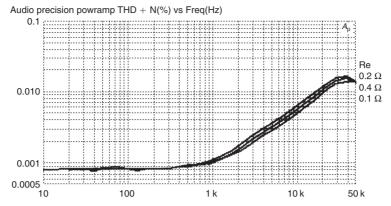

| The complementary feedback pair (CFP) output  |  |

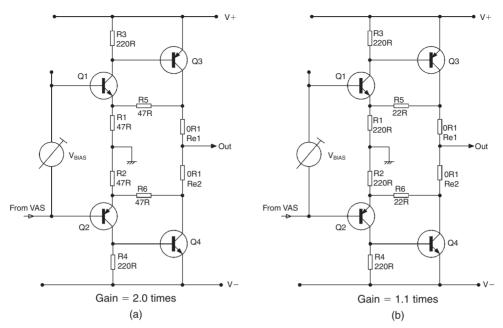

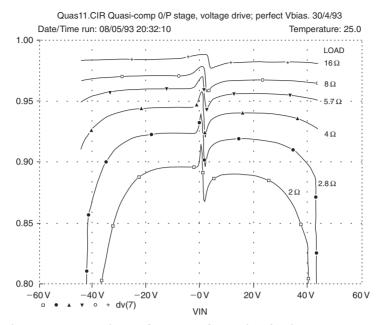

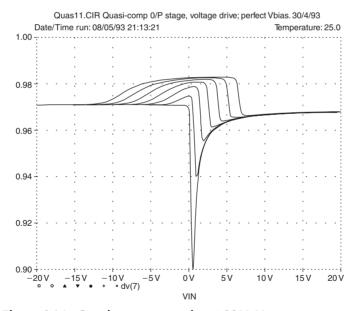

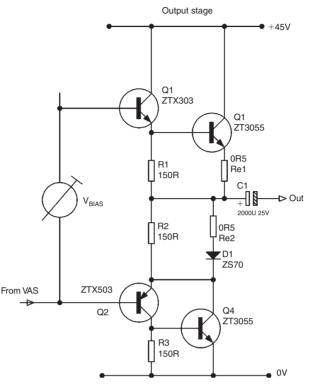

| Output stages with gain                       |  |

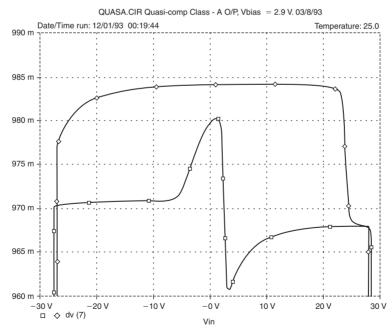

| Quasi-complementary outputs                   |  |

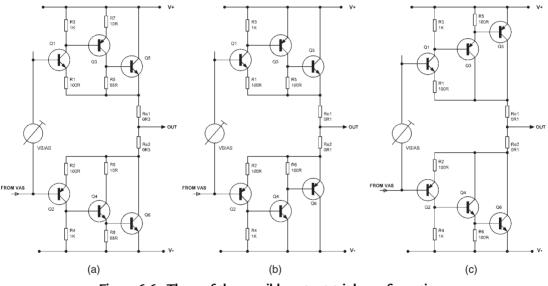

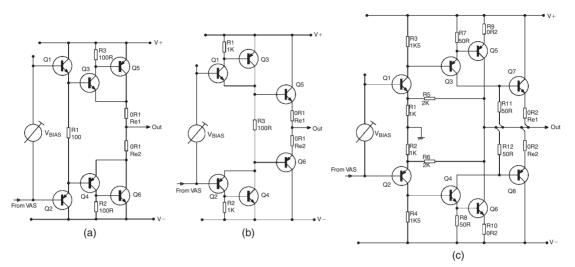

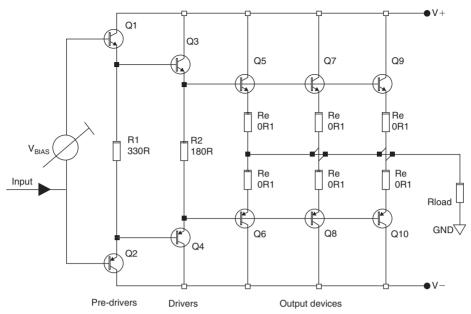

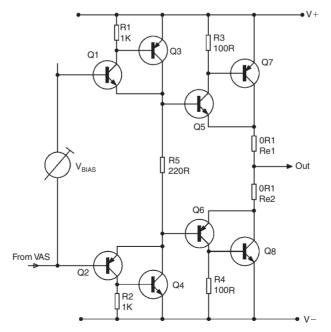

| Triple-based output configurations            |  |

| Triple-EF output stages                       |  |

| Quadruple output stages                       |  |

| Output stage distortions and their mechanisms |  |

| Large-signal distortion (Distortion 3a)       |  |

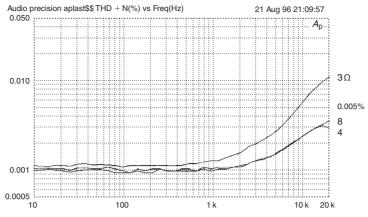

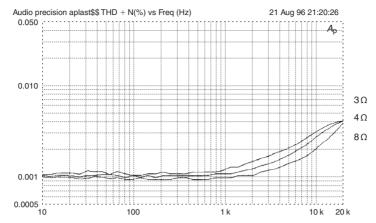

| The Load-Invariant concept                    |  |

| The LSN mechanism                             |  |

| Doubled output devices                        |  |

| Better output devices                         |  |

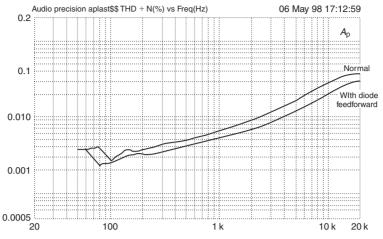

| Feedforward diodes                            |  |

| Trouble with triples                          |  |

| Loads below $4\Omega$                         |  |

| Better 8 $\Omega$ performance                 |  |

| A practical Load-Invariant design             |  |

| More on multiple output devices               |  |

| Load invariance: summary                      |  |

| Crossover distortion (Distortion 3b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Output stage quiescent conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

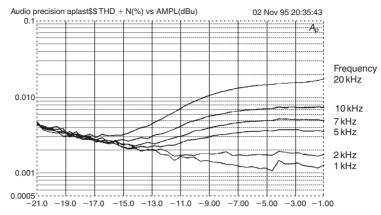

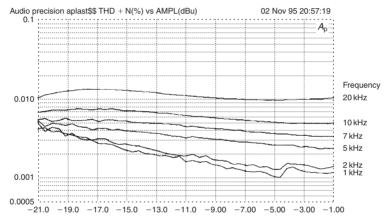

| An experiment on crossover distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                            |

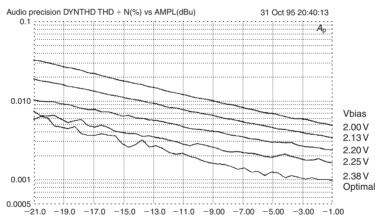

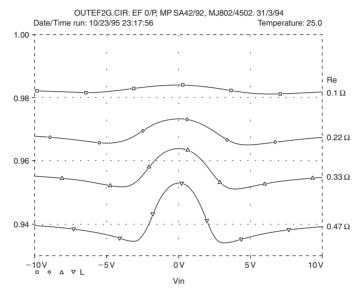

| $V_{\rm q}$ as the critical quiescent parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

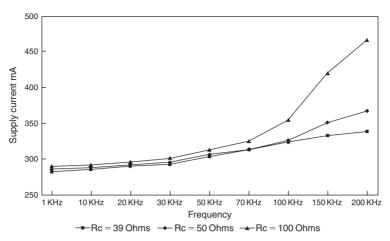

| Switching distortion (Distortion 3c)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

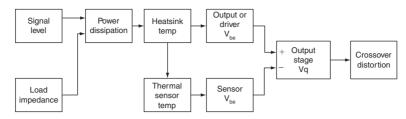

| Thermal distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| Thermal distortion in a power amp IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| Selecting an output stage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                            |

| Closing the loop: distortion in complete amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                            |

| Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

| Chapter 7 More distortion mechanisms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| Distortion 4: VAS-loading distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                            |

| Distortion 5: Rail-decoupling distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

| Distortion 6: Induction distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| Distortion 7: NFB take-off point distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                            |

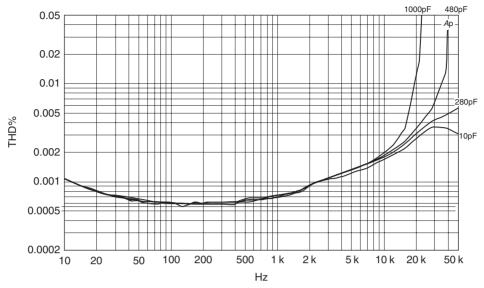

| Distortion 8: Capacitor distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| Distortion 9: Magnetic distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

| Distortion 10: Input current distortion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

| Distortion 11: Premature overload protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                            |

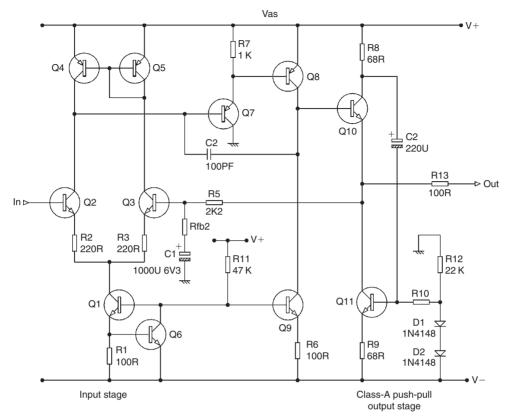

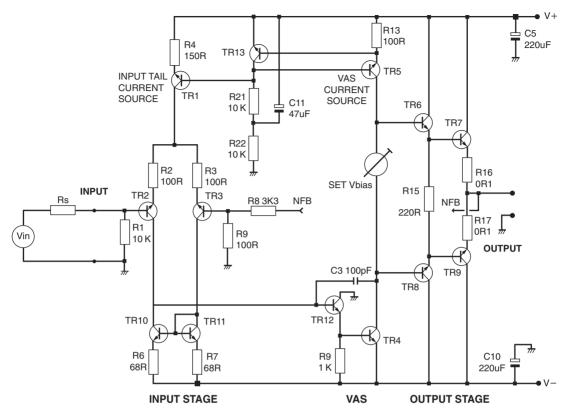

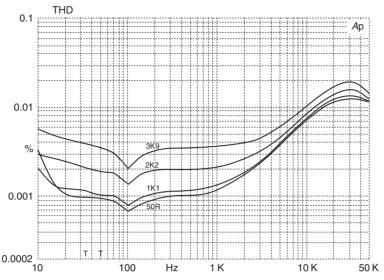

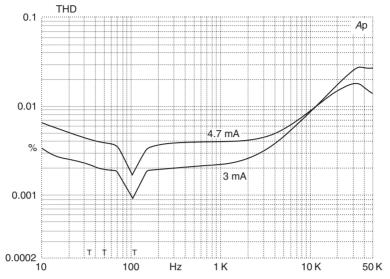

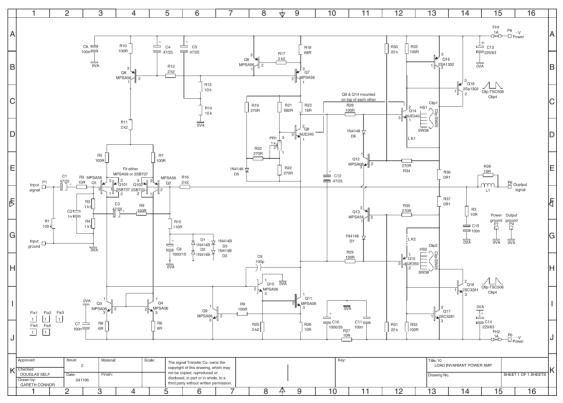

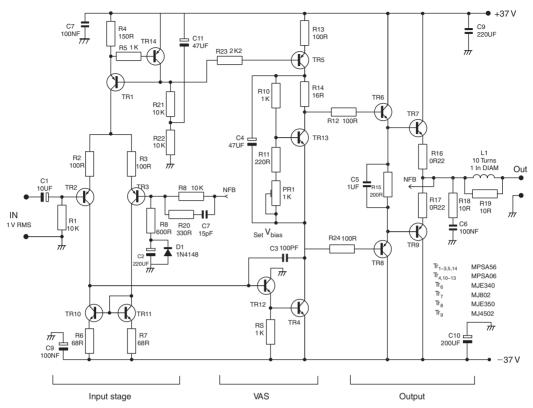

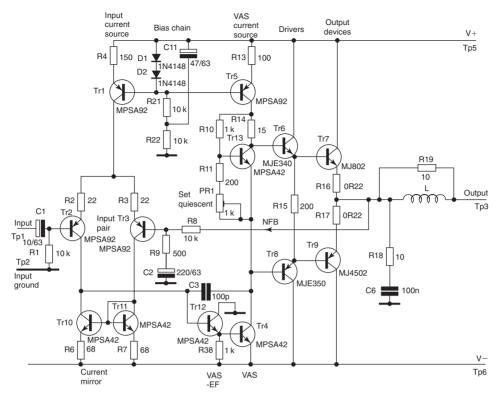

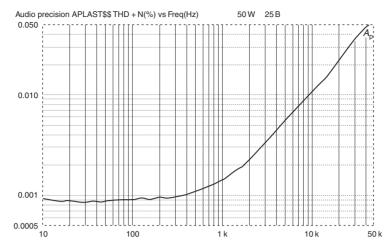

| Design example – a 50W Class-B amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

| Chapter 8 Compensation, slew rate, and stability                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                            |

| <b>Chapter 8 Compensation, slew rate, and stability</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                            |

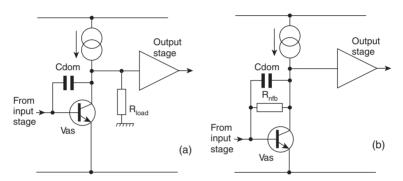

| Frequency compensation in general                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                            |

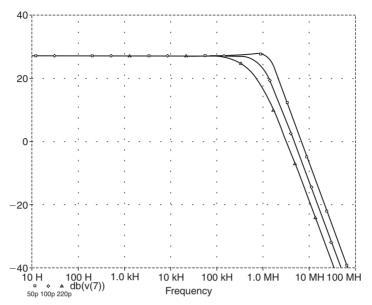

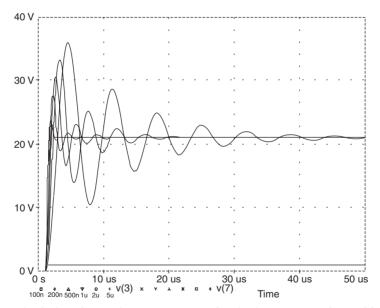

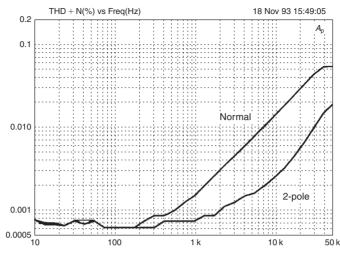

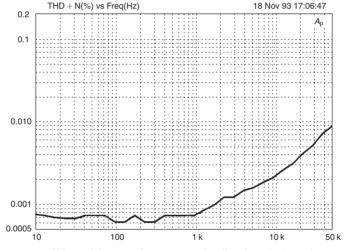

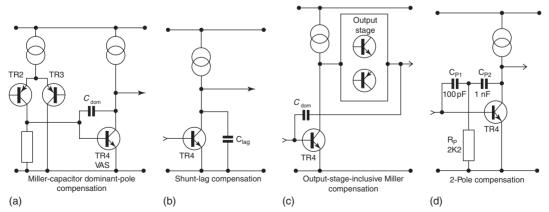

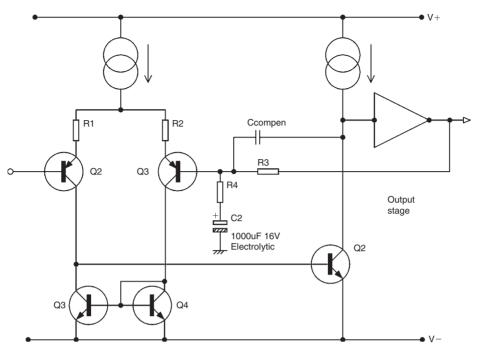

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                            |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation                                                                                                                                                                                                                                                                                                                                  | 215<br>                                                                                                                    |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens                                                                                                                                                                                                                                                                                                                                                                           | 215<br>                                                                                                                    |

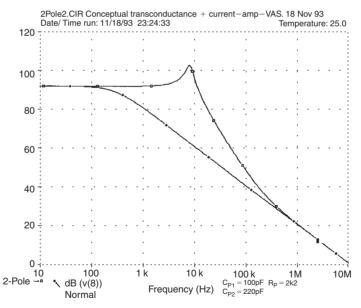

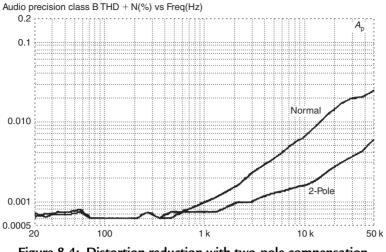

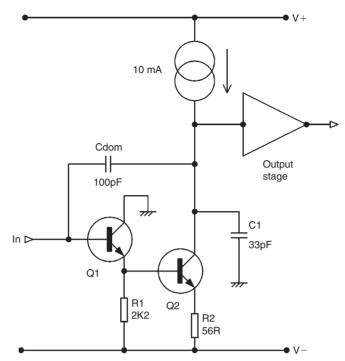

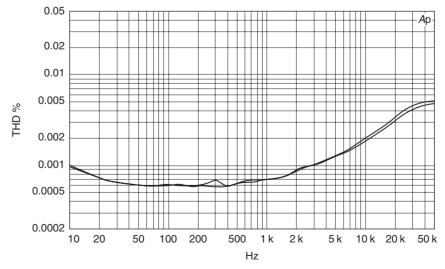

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance                                                                                                                                                                                                                                                    | 215<br>                                                                                                                    |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation<br>Two-pole compensation                                                                                                                                                                                                                                                                                                         | 215<br>                                                                                                                    |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance                                                                                                                                                                                                                                                    | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>222<br>223                                                         |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops                                                                                                                                                                                                                           | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>218<br>222<br>223<br>223<br>224                                    |

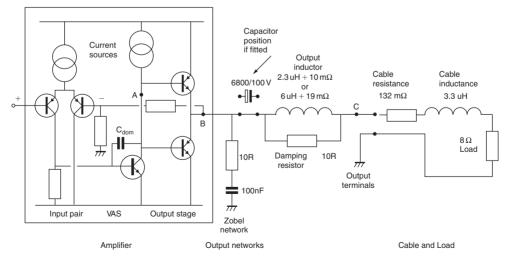

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks                                                                                                                                                                                                        | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>222<br>223<br>224<br>224                                           |

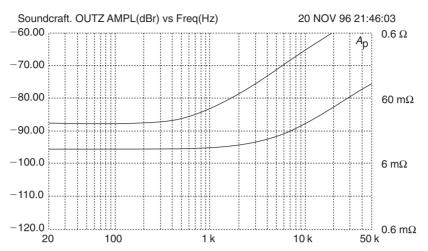

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compens<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance                                                                                                                                                                          | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>222<br>223<br>223<br>224<br>224<br>224<br>224                      |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compense<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance<br>Minimizing amplifier output impedance                                                                                                                                | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>222<br>223<br>223<br>224<br>224<br>224<br>224<br>227               |

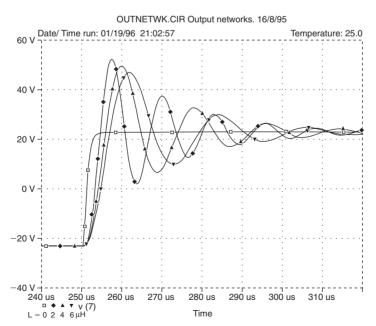

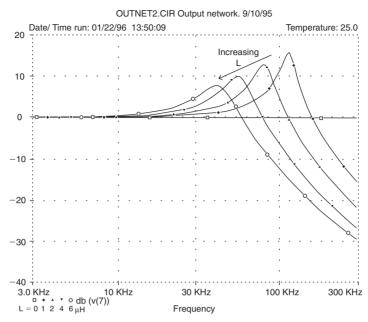

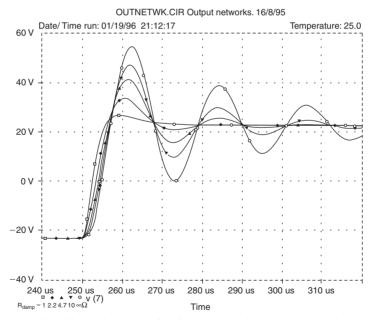

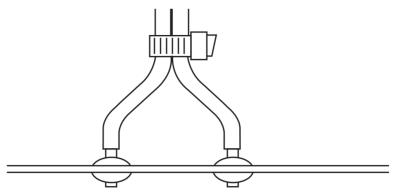

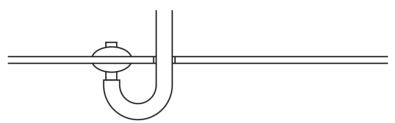

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compense<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance<br>Zobel networks<br>Output inductors<br>The output inductor value                                                                                                      | 215<br>216<br>217<br>sation 217<br>218<br>218<br>222<br>223<br>224<br>224<br>224<br>224<br>224<br>224<br>224<br>224        |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compense<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance<br>Zobel networks<br>Output inductors                                                                                                                                   | 215<br>216<br>217<br>sation 217<br>218<br>218<br>222<br>223<br>224<br>224<br>224<br>224<br>224<br>224<br>224<br>224        |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compense<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance<br>Minimizing amplifier output impedance<br>Zobel networks<br>Output inductors<br>The output inductor value<br>Cable effects<br>Crosstalk in amplifier output inductors | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>222<br>223<br>224<br>224<br>224<br>224<br>224<br>224<br>224<br>224 |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compense<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance<br>Xobel networks<br>Output inductors<br>The output inductor value<br>Cable effects                                                                                     | 215<br>216<br>217<br>sation 217<br>218<br>218<br>218<br>222<br>223<br>224<br>224<br>224<br>224<br>224<br>224<br>224<br>224 |

| Frequency compensation in general<br>Dominant-pole compensation<br>Lag compensation<br>Including the output stage: output-inclusive Miller compense<br>Other forms of inclusive compensation<br>Two-pole compensation<br>Stability and VAS-collector-to-ground capacitance<br>Nested feedback loops<br>Output networks<br>Amplifier output impedance<br>Minimizing amplifier output impedance<br>Zobel networks<br>Output inductors<br>The output inductor value<br>Cable effects<br>Crosstalk in amplifier output inductors | 215<br>216<br>217<br>sation 217<br>218<br>218<br>222<br>223<br>224<br>224<br>224<br>224<br>224<br>224<br>224<br>224        |

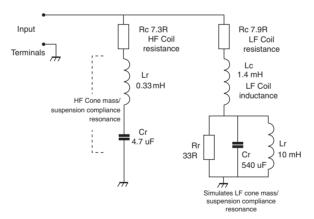

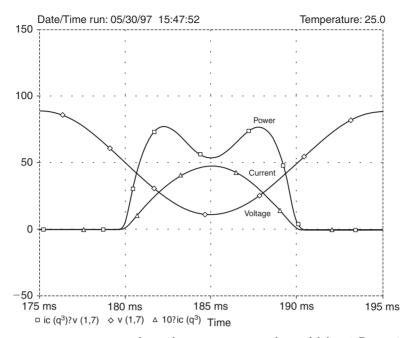

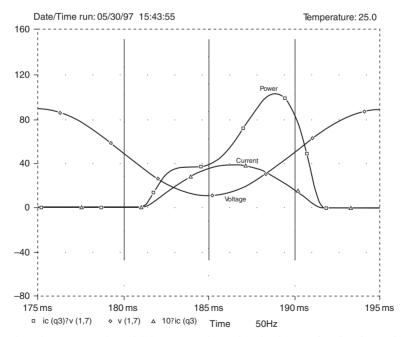

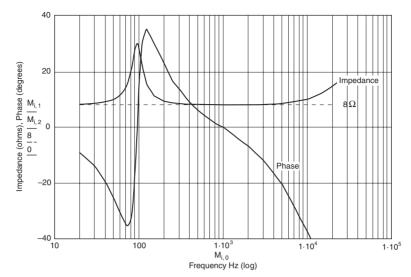

| Modeling real loudspeaker loading                 |     |

|---------------------------------------------------|-----|

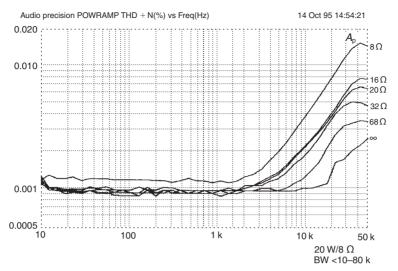

| Loudspeaker loads and output stages               |     |

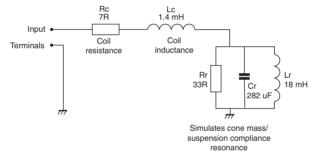

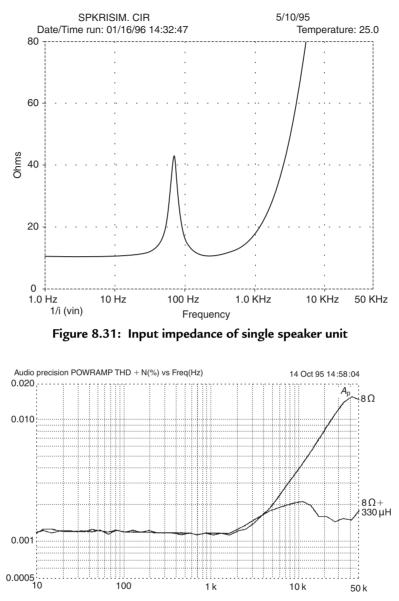

| Single-speaker load                               |     |

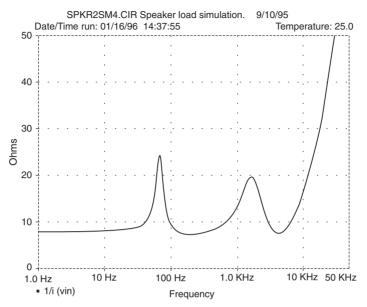

| Two-way speaker loads                             |     |

| Enhanced loudspeaker currents                     |     |

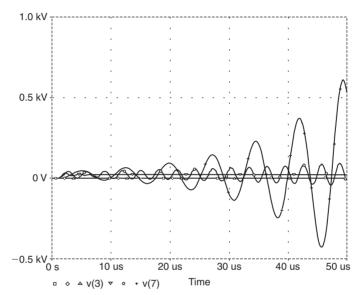

| Amplifier instability                             |     |

| HF instability                                    |     |

| LF instability                                    |     |

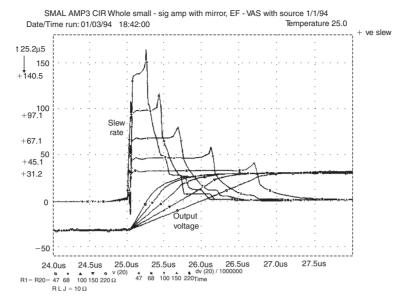

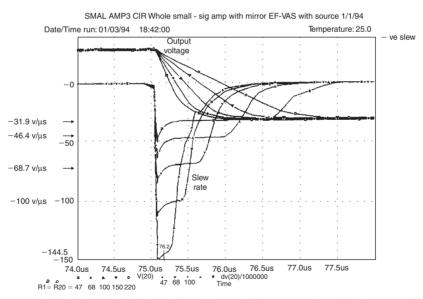

| Speed and slew rate in audio amplifiers           |     |

| The basics of amplifier slew-limiting             |     |

| Slew-rate measurement techniques                  |     |

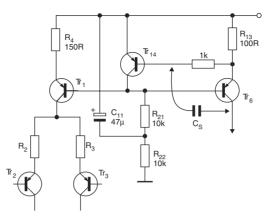

| Improving the slew rate                           |     |

| Simulating slew-limiting                          |     |

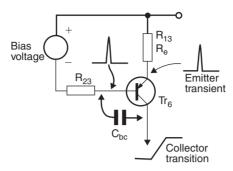

| Slewing limitations in real life                  |     |

| Some additional complications                     |     |

| Further improvements and other configurations     |     |

|                                                   |     |

| Chapter 9 Power supplies and PSRR                 |     |

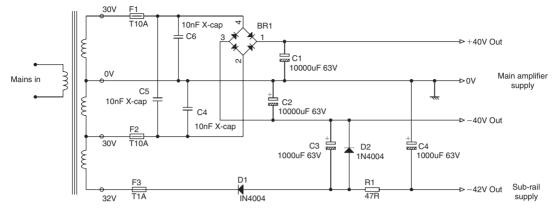

| Power-supply technologies                         |     |

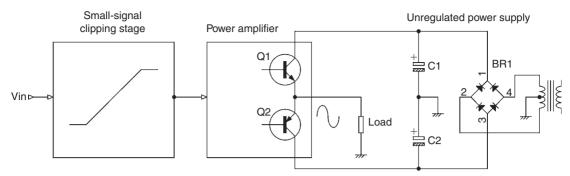

| Simple unregulated power supplies                 |     |

| Advantages                                        |     |

| Disadvantages                                     |     |

| Linear regulated power supplies                   |     |

| Advantages                                        |     |

| Disadvantages                                     |     |

| Switch-mode power supplies                        |     |

| Advantages                                        |     |

| Disadvantages                                     |     |

| A devious alternative to regulated power supplies |     |

| Design considerations for power supplies          |     |

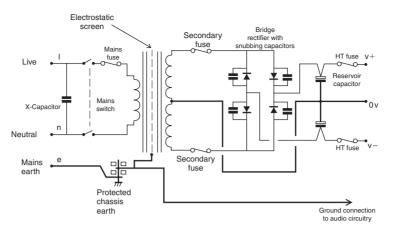

| Mains transformers                                |     |

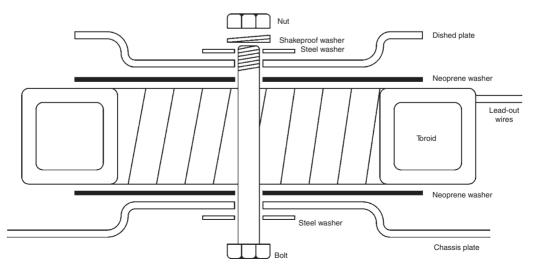

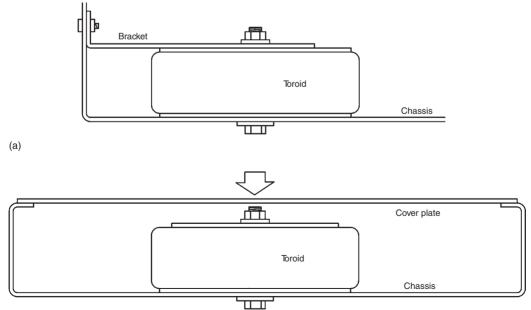

| Transformer mounting                              |     |

| Transformer specifications                        |     |

| Electrical specifications                         |     |

| Mechanical matters                                |     |

| Transformer evaluation                            |     |

| Transformers and hum                              |     |

| External power supplies                           |     |

| Advantages                                        | 279 |

| Disadvantages                                     |     |

| Inrush currents                                   |     |

| Inrush suppression by thermistor                  |     |

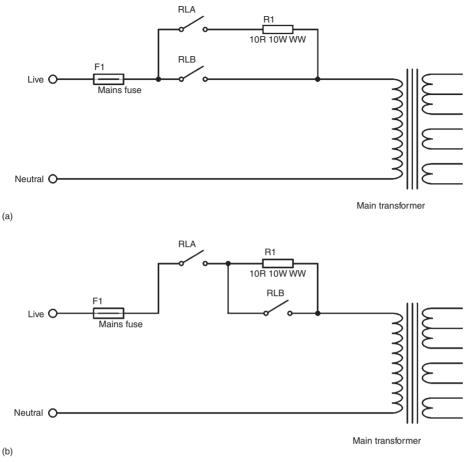

| Inrush suppression by relay                                          |  |

|----------------------------------------------------------------------|--|

| Fusing and rectification                                             |  |

| RF emissions from bridge rectifiers                                  |  |

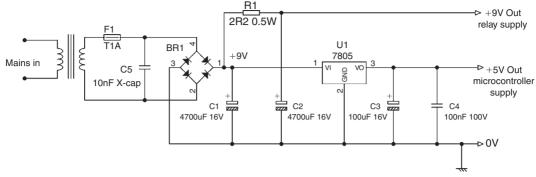

| Relay supplies                                                       |  |

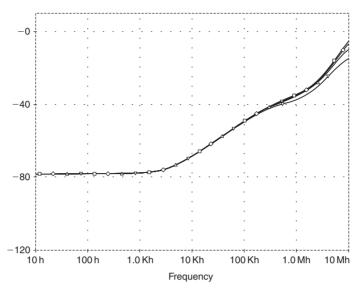

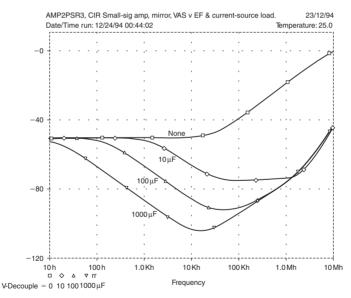

| Power-supply rail rejection in amplifiers                            |  |

| A design philosophy for supply-rail rejection                        |  |

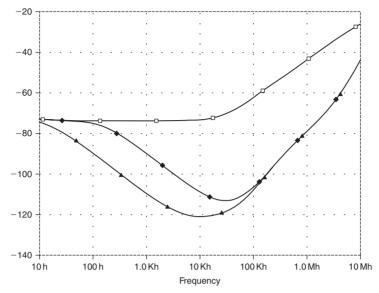

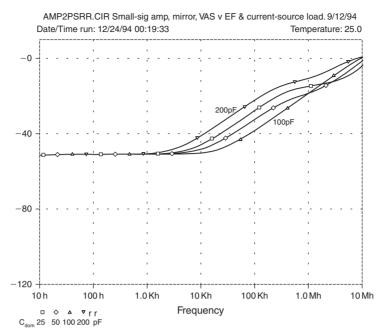

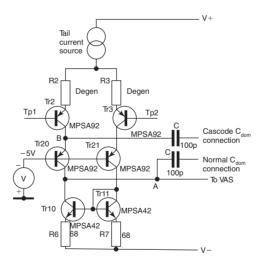

| Positive supply-rail rejection                                       |  |

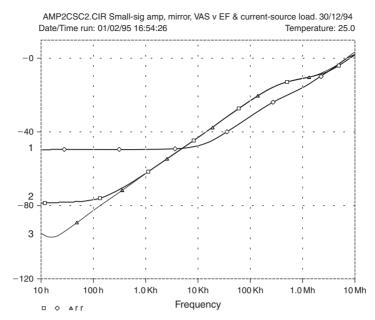

| Negative supply-rail rejection                                       |  |

| Negative sub-rails                                                   |  |

| Chapter 10 Class-A power amplifiers                                  |  |

| An introduction to Class-A                                           |  |

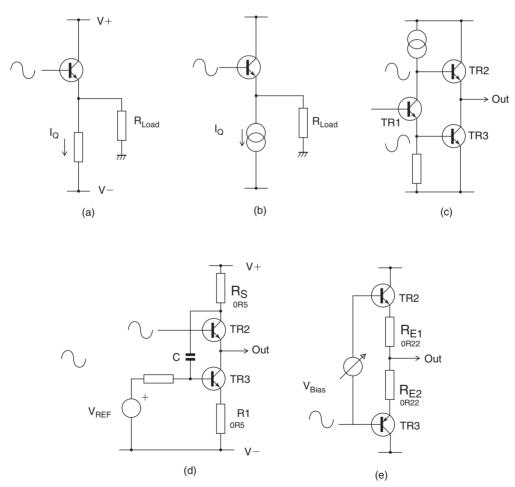

| Class-A configurations and efficiency                                |  |

| Output stages in Class-A                                             |  |

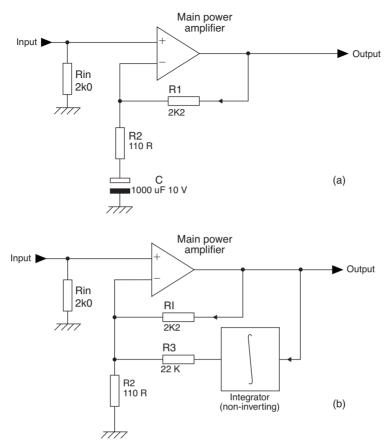

| Quiescent current control systems                                    |  |

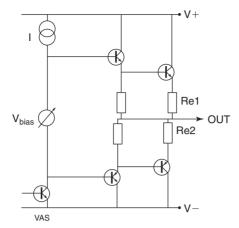

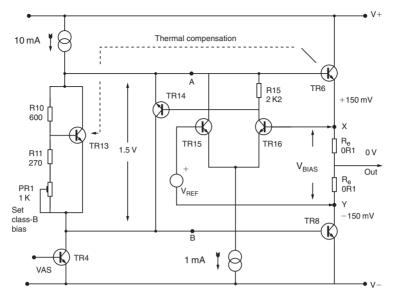

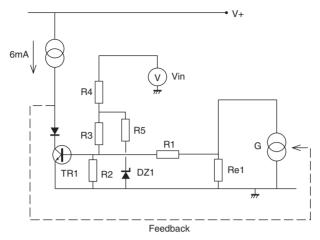

| A novel quiescent current controller                                 |  |

| A Class-A design                                                     |  |

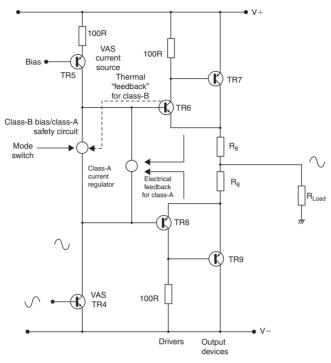

| The Trimodal amplifier                                               |  |

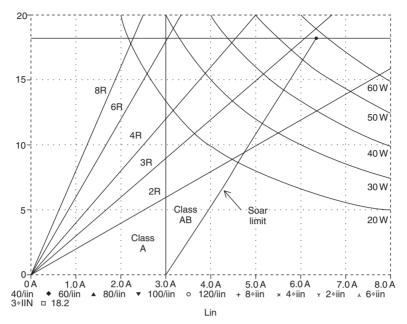

| Load impedance and operating mode                                    |  |

| Efficiency                                                           |  |

| On Trimodal biasing                                                  |  |

| Class-A/AB mode                                                      |  |

| Class-B mode                                                         |  |

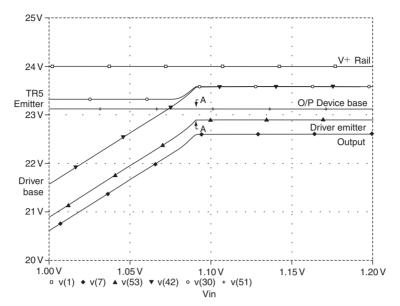

| The mode-switching system                                            |  |

| Thermal design                                                       |  |

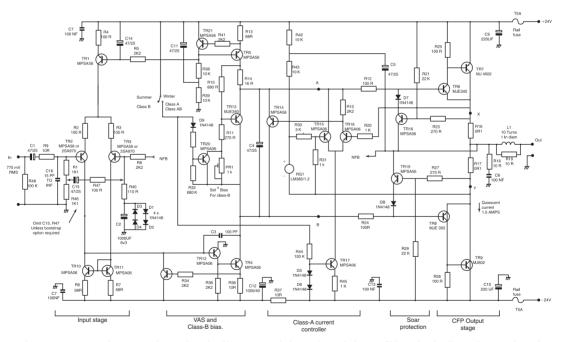

| A complete Trimodal amplifier circuit                                |  |

| The power supply                                                     |  |

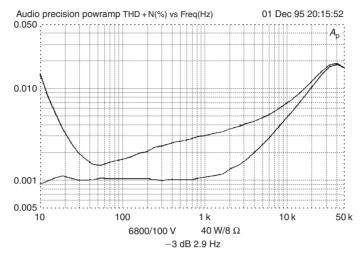

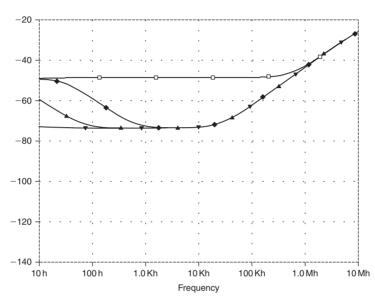

| The performance                                                      |  |

| Further possibilities                                                |  |

| Chapter 11 Class-XD <sup>™</sup> : crossover displacement technology |  |

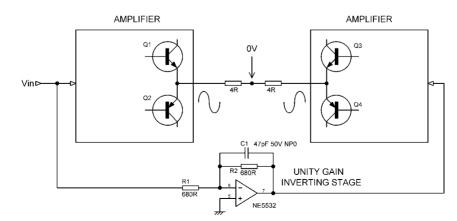

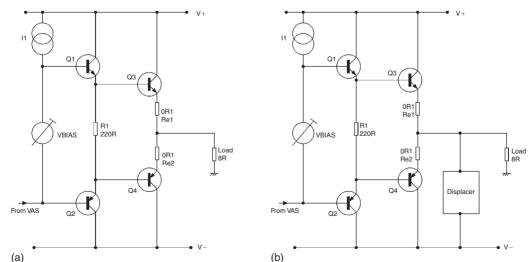

| The crossover displacement principle                                 |  |

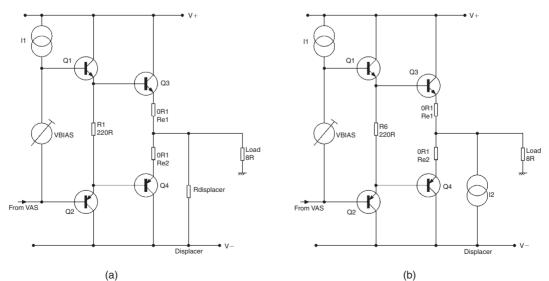

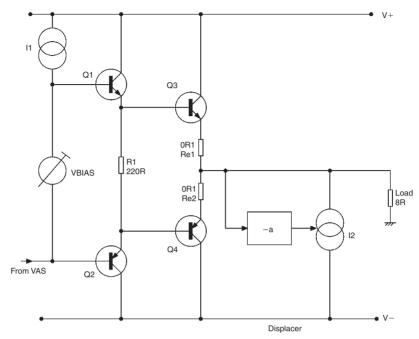

| Crossover displacement realization                                   |  |

| Circuit techniques for crossover displacement                        |  |

| A complete crossover displacement power amplifier circuit            |  |

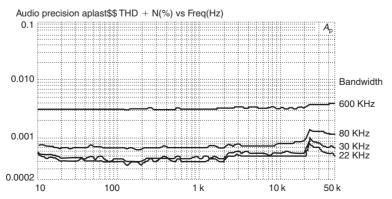

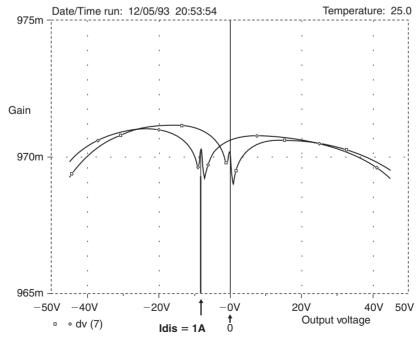

| The measured performance                                             |  |

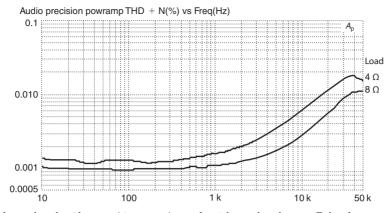

| The effect of loading changes                                        |  |

| The efficiency of crossover displacement                             |  |

| Other methods of push-pull displacement control                      |  |

| Summary                                                              |  |

| Advantages                                                           |  |

| Disadvantages                                                        |  |

| Chapter 12 Class-G power amplifiers                  |     |

|------------------------------------------------------|-----|

| The principles of Class-G                            |     |

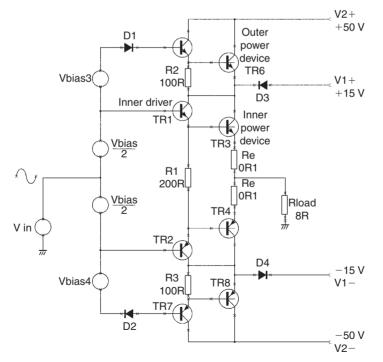

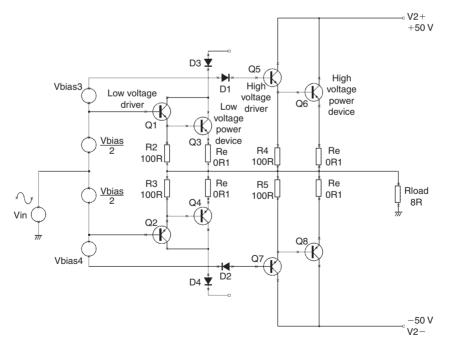

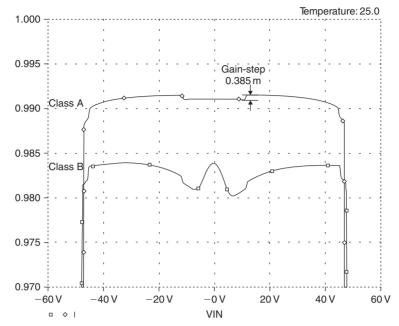

| Introducing series Class-G                           |     |

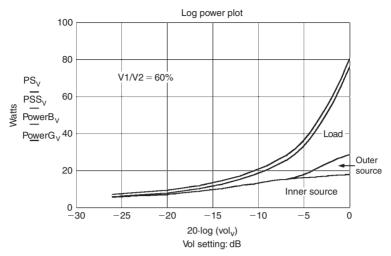

| Efficiency of Class-G                                |     |

| Practicalities                                       |     |

| The biasing requirements                             |     |

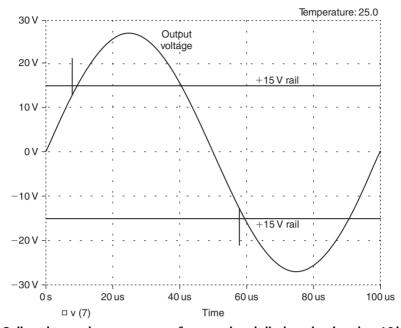

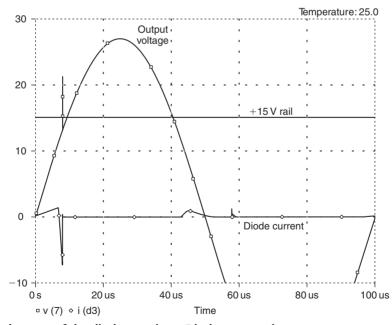

| The linearity issues of series Class-G               |     |

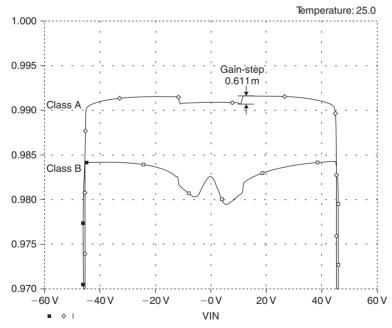

| The static linearity                                 |     |

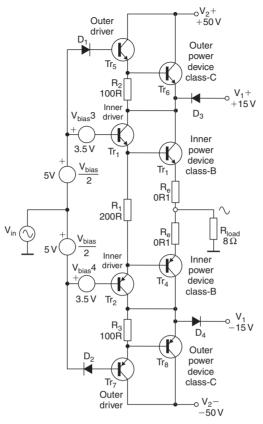

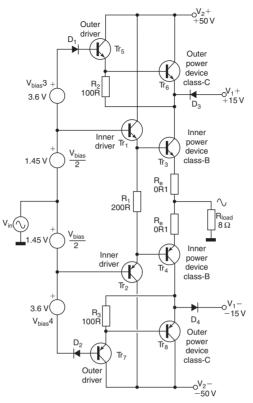

| Practical Class-G design                             |     |

| Controlling small-signal distortion                  |     |

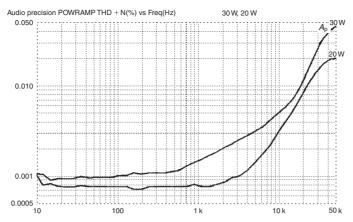

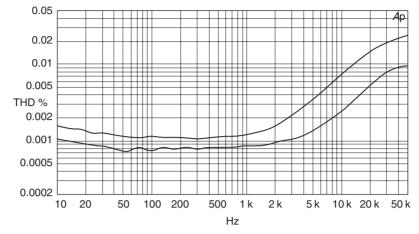

| The performance                                      |     |

| Deriving a new kind of amplifier: Class-A + C        |     |

| Adding two-pole compensation                         |     |

| Further variations on Class-G                        |     |

|                                                      |     |

| Chapter 13 Class-D amplifiers                        |     |

| History                                              |     |

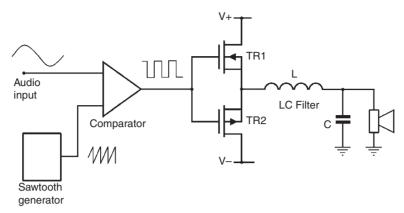

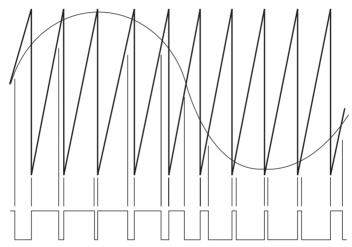

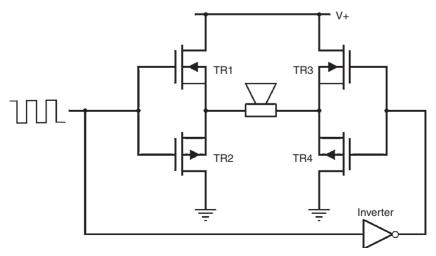

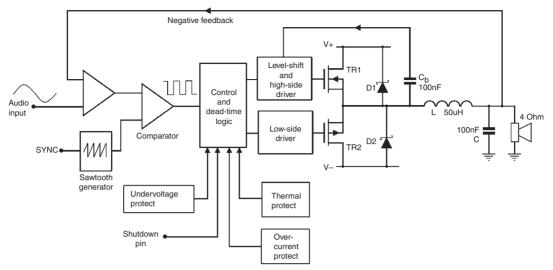

| Basic principles                                     |     |

| Technology                                           |     |

| Protection                                           |     |

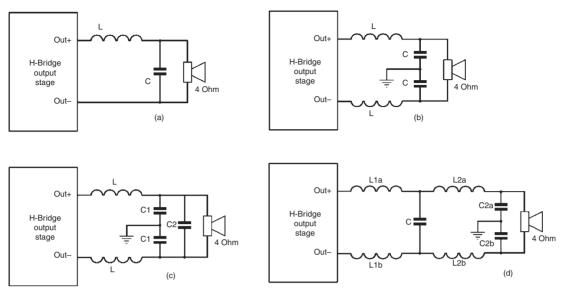

| Output filters                                       |     |

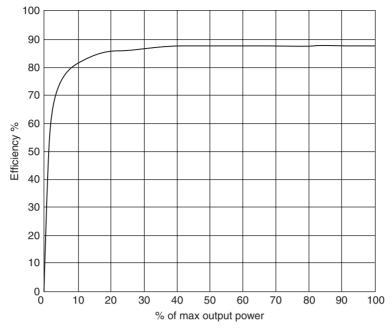

| Efficiency                                           |     |

| Chapter 14 FET output stages                         | 373 |

| The characteristics of power FETs                    |     |

| FET versus BJT output stages                         |     |

| Advantages of FETs                                   |     |

| Disadvantages of FETs                                |     |

| IGBTs                                                |     |

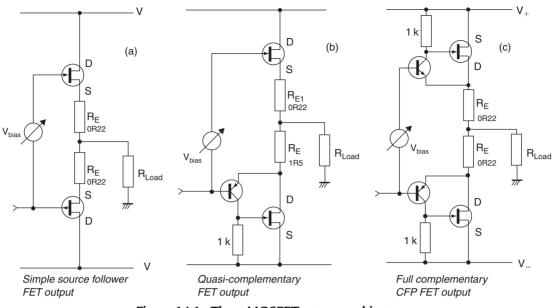

| Power FET output stages                              |     |

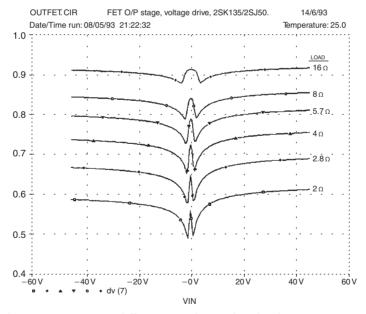

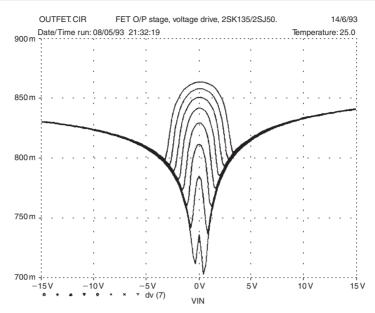

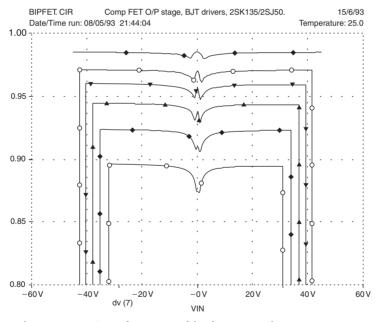

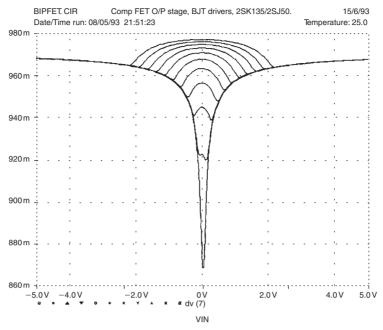

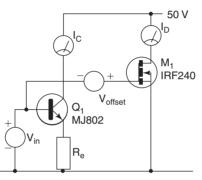

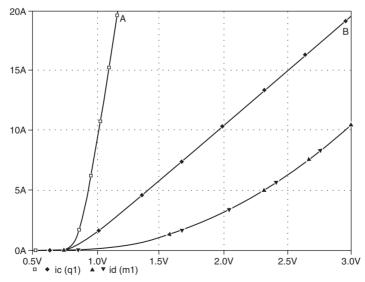

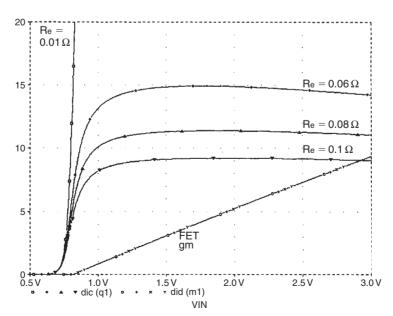

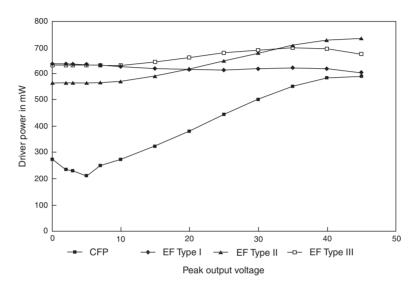

| Power FETs and bipolars: the linearity competition   |     |

| FETs in Class-A stages                               |     |

|                                                      |     |

| Chapter 15 Thermal compensation and thermal dynamics |     |

| Why quiescent conditions are critical                |     |

| Accuracy required of thermal compensation            |     |

| Basic thermal compensation                           |     |

| Assessing the bias errors                            |     |

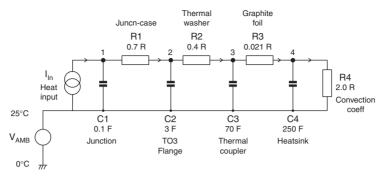

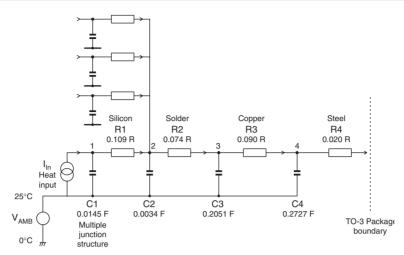

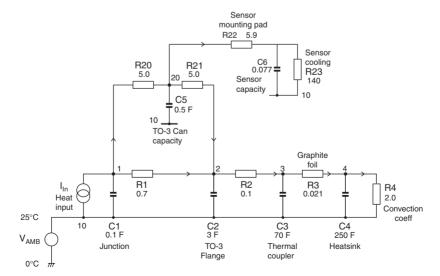

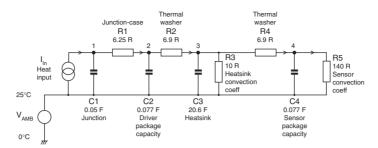

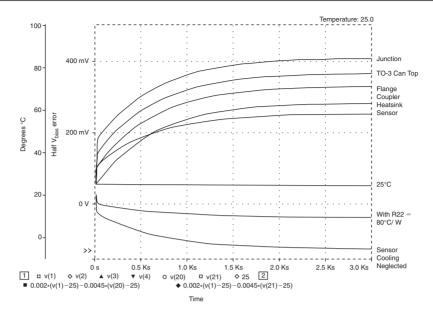

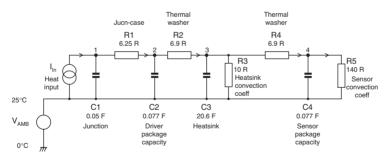

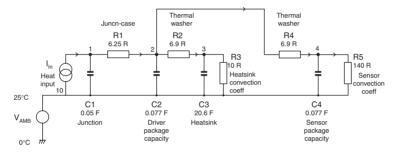

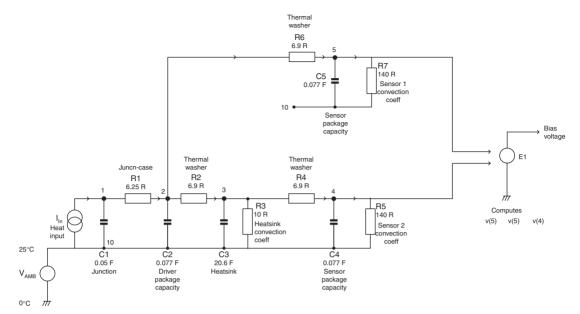

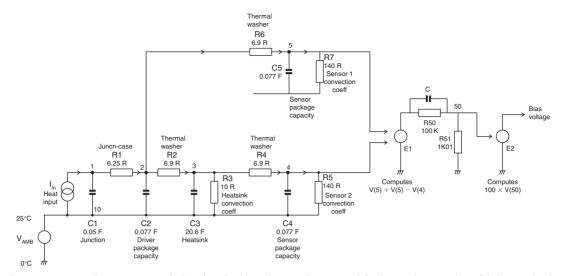

| Thermal simulation                                   |     |

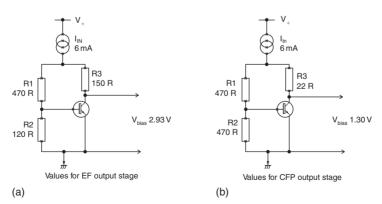

| Modeling the EF output stage                         |     |

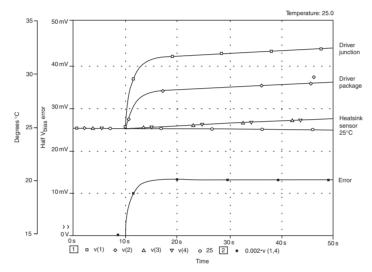

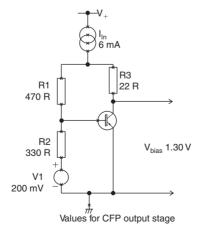

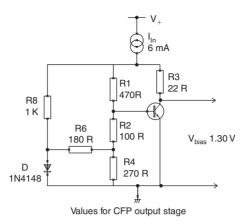

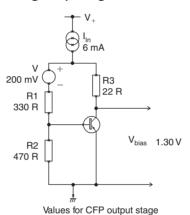

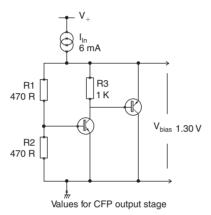

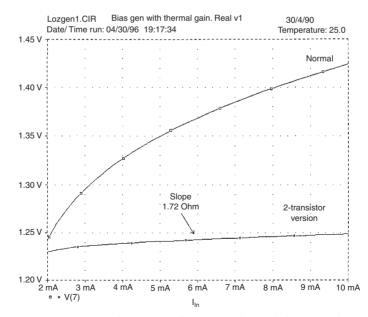

| Modeling the CFP output stage                        |     |

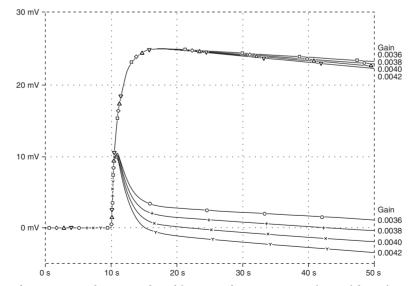

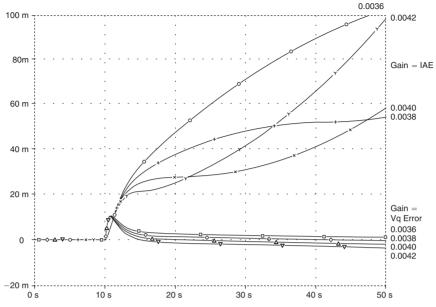

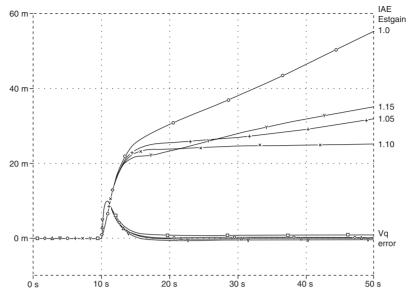

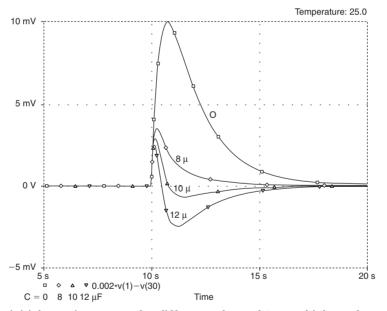

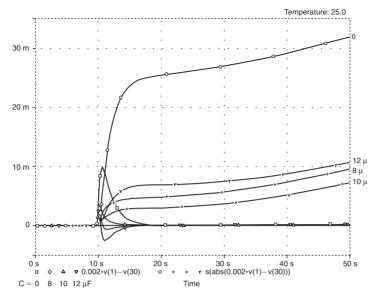

| The Integrated Absolute Error Criterion             | 400 |

|-----------------------------------------------------|-----|

| Improved thermal compensation for the EF stage      | 400 |

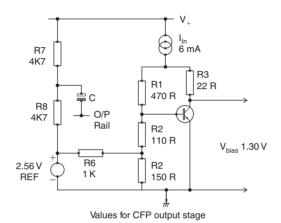

| Improved compensation for the CFP output stage      | 403 |

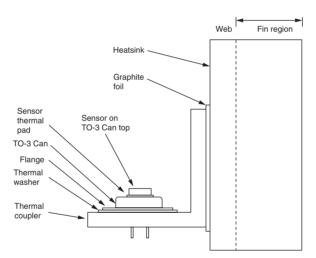

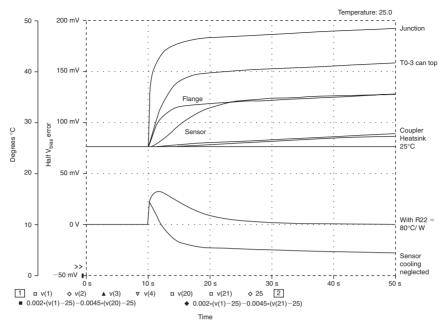

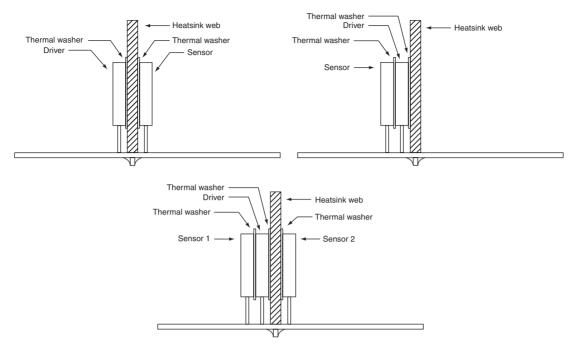

| A better sensor position                            | 405 |

| A junction-temperature estimator                    | 406 |

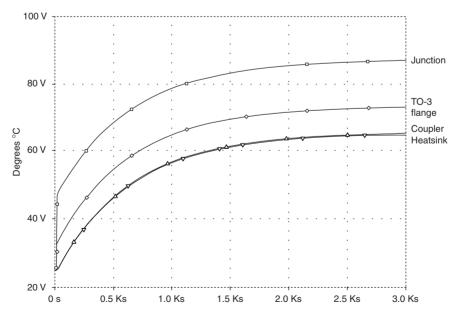

| A junction estimator with dynamics                  | 408 |

| Conclusions about the simulations                   | 409 |

| Power transistors with integral temperature sensors | 410 |

| Variable-tempco bias generators                     | 412 |

| Creating a higher tempco                            | 413 |

| Ambient temperature changes                         | 414 |

| Creating a lower tempco                             |     |

| Current compensation                                | 416 |

| Early effect in output stages                       |     |

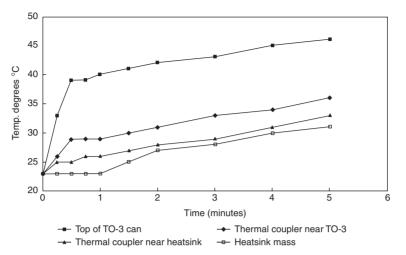

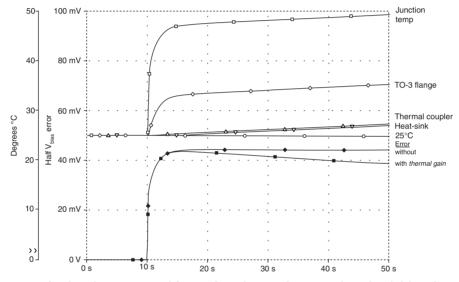

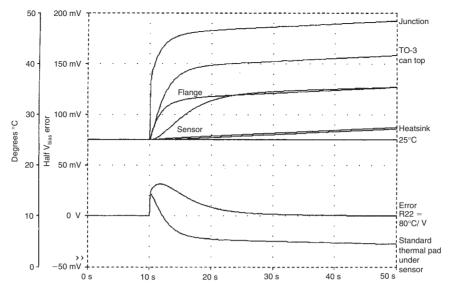

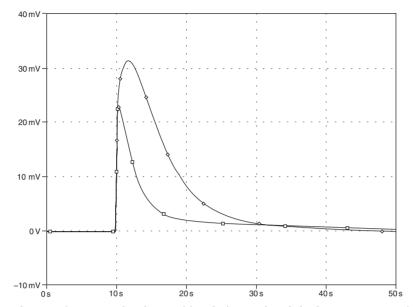

| Thermal dynamics by experiment                      | 420 |

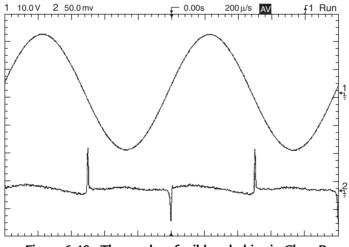

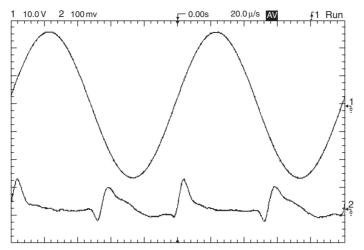

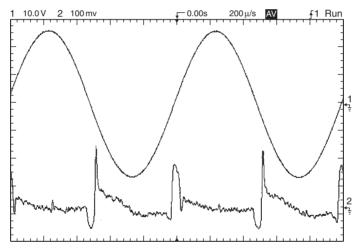

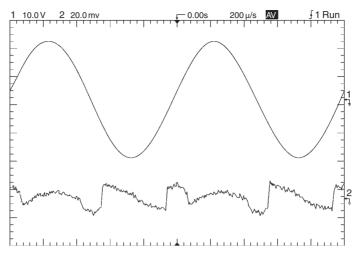

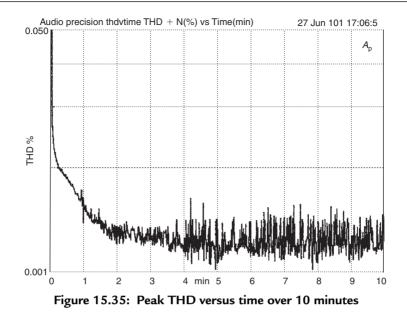

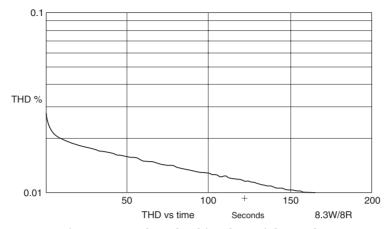

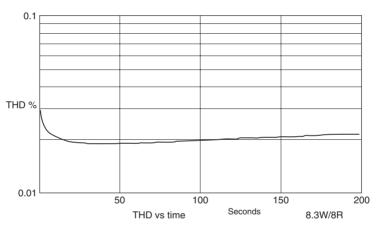

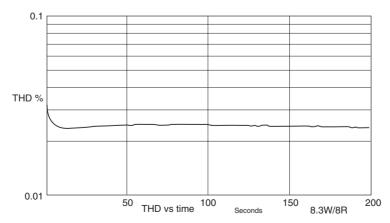

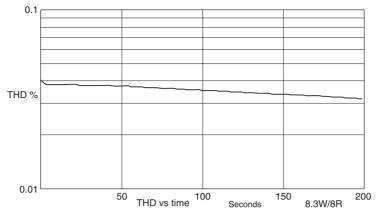

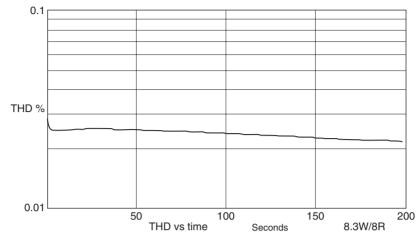

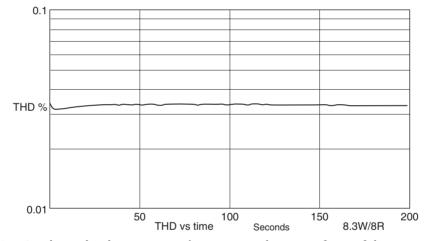

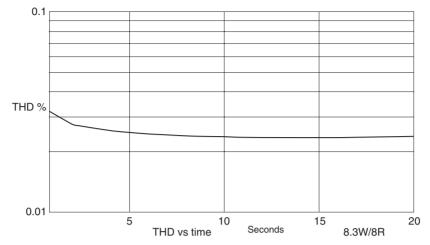

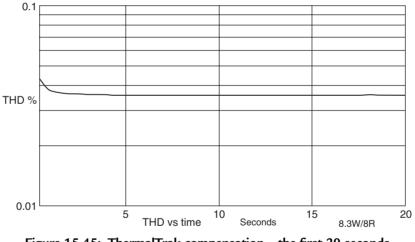

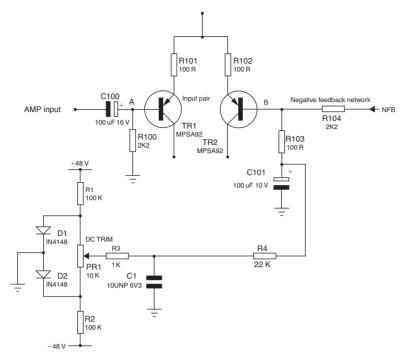

| Crossover distortion against time – some results    | 420 |

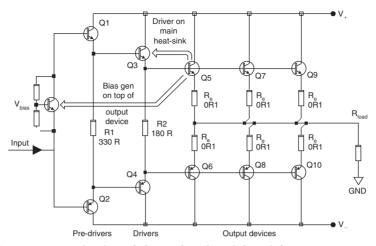

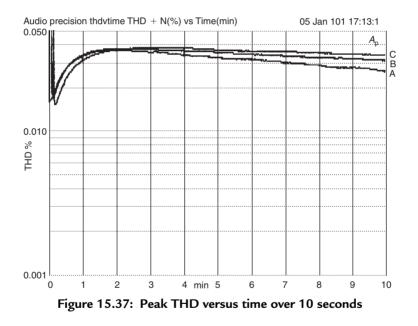

| More measurements – conventional and ThermalTrak    |     |

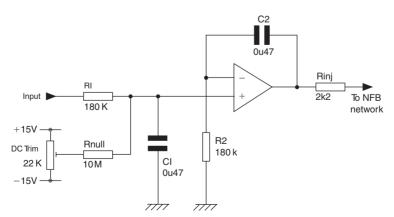

| Chapter 16 The design of DC servos        |  |

|-------------------------------------------|--|

| DC offset trimming                        |  |

| DC offset control by servo-loop           |  |

| The advantages of DC servos               |  |

| Basic servo configurations                |  |

| Noise, component values, and the roll-off |  |

| Non-inverting integrators                 |  |

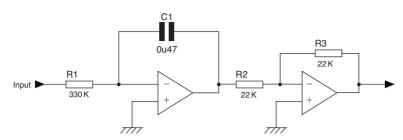

| The 2C integrator                         |  |

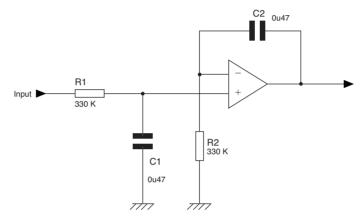

| The 1C integrator                         |  |

| Choice of integrator type                 |  |

| Choice of op-amps                         |  |

| Servo authority                           |  |

| Design of LF roll-off point               |  |

| Servo overload                            |  |

| Servo testing                             |  |

| Performance issues                        |  |

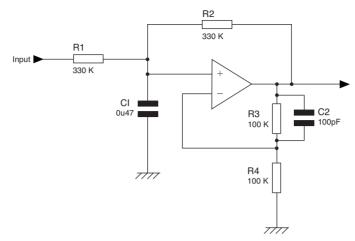

| Multi-pole servos                         |  |

| Chapter 17 Amplifier and loudspeaker protection |  |

|-------------------------------------------------|--|

| Categories of amplifier protection              |  |

| Semiconductor failure modes                     |  |

| Overload protection                             |  |

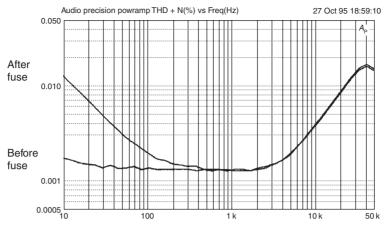

| Overload protection by fuses                    |  |

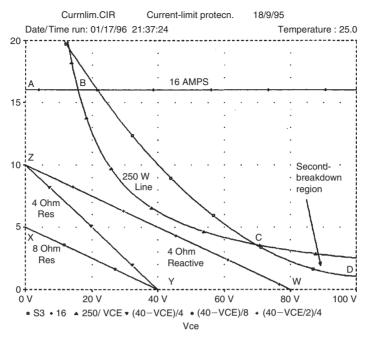

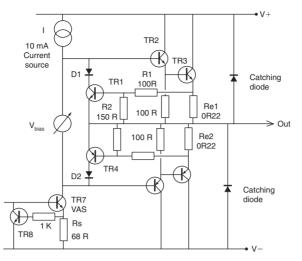

| Electronic overload protection          | 444 |

|-----------------------------------------|-----|

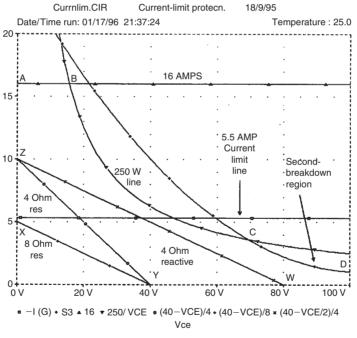

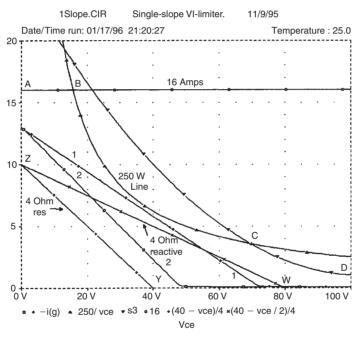

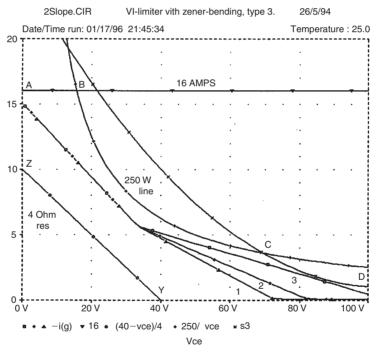

| Plotting the protection locus           |     |

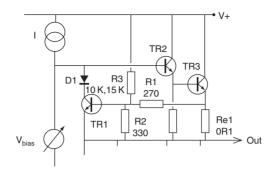

| Simple current limiting                 |     |

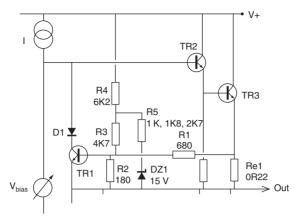

| Single-slope VI limiting                |     |

| Dual-slope VI limiting                  | 450 |

| VI limiting and temperature effects     |     |

| Simulating overload protection systems  |     |

| Testing the overload protection         | 454 |

| Speaker short-circuit detection         | 455 |

| Catching diodes                         | 455 |

| DC offset protection                    | 456 |

| DC protection by fuses                  | 456 |

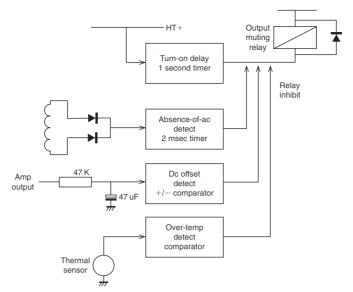

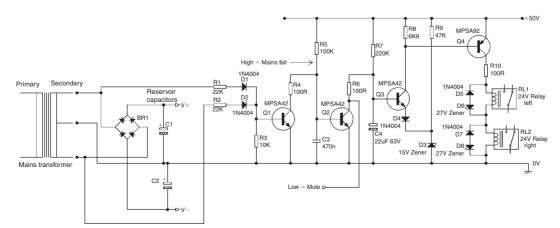

| Relay protection and muting control     | 458 |

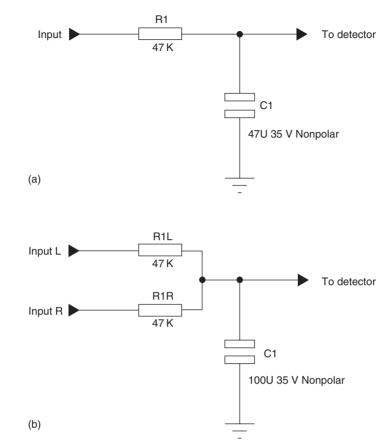

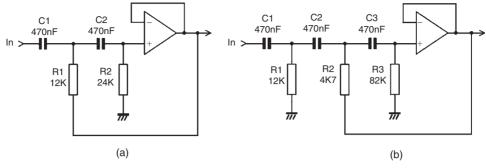

| Filtering for DC protection             | 459 |

| The single RC filter                    | 459 |

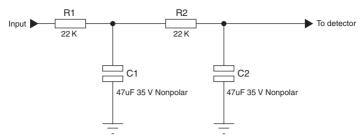

| The dual RC filter                      | 460 |

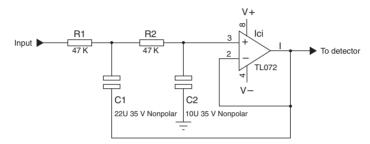

| The second-order active filter          | 461 |

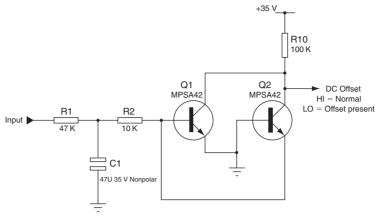

| Bidirectional DC detection              |     |

| The conventional two-transistor circuit |     |

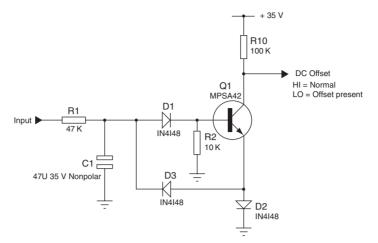

| The one-transistor version              |     |

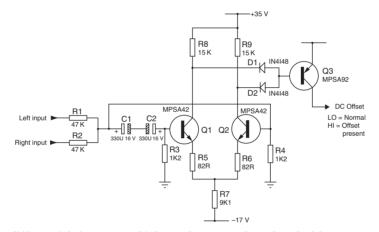

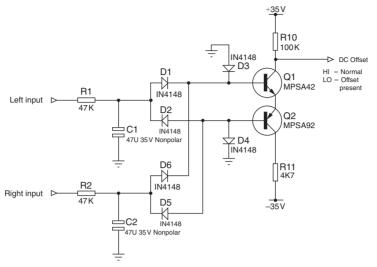

| The differential detector               |     |

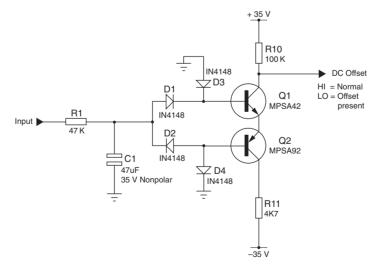

| The Self detector                       | 464 |

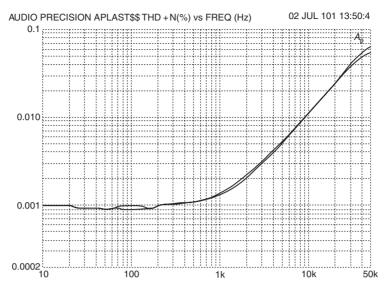

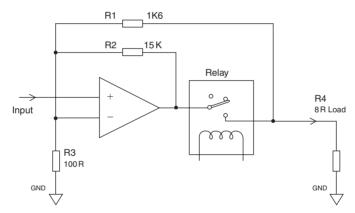

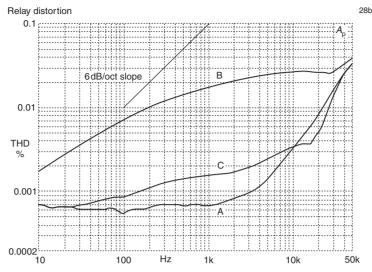

| Distortion in output relays             |     |

| Output crowbar DC protection            |     |

| Protection by power-supply shutdown     |     |

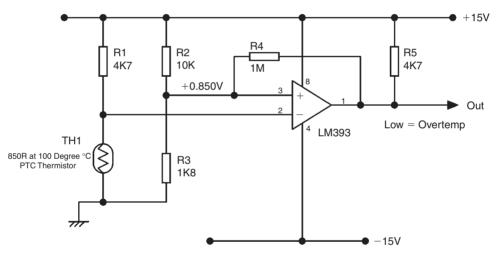

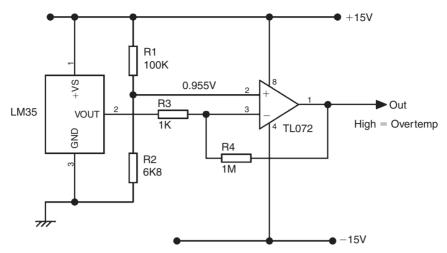

| Thermal protection                      | 471 |

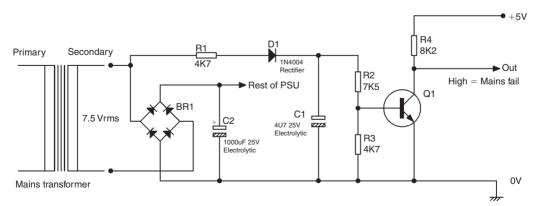

| Mains-fail detection                    |     |

| Powering auxiliary circuitry            |     |

| Chapter 18 Grounding, cooling, and layout |  |

|-------------------------------------------|--|

| Audio amplifier PCB design                |  |

| Crosstalk                                 |  |

| Rail induction distortion                 |  |

| Mounting output devices on the main PCB   |  |

| Advantages                                |  |

| Disadvantages                             |  |

| Single- and double-sided PCBs             |  |

| Power-supply PCB layout                   |  |

| Power amplifier PCB layout details        |  |

| The audio PCB layout sequence             |  |

| Miscellaneous points                      |  |

| -                                         |  |

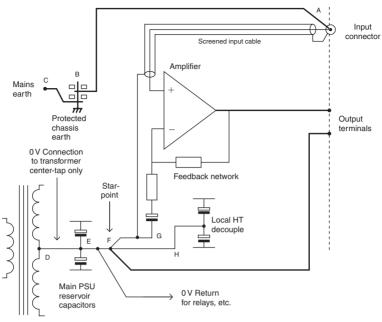

| Amplifier grounding                                   | 487 |

|-------------------------------------------------------|-----|

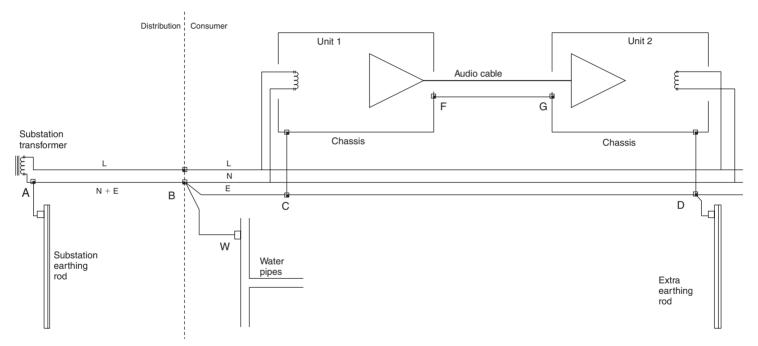

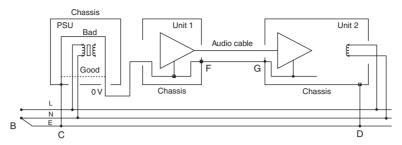

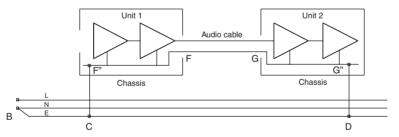

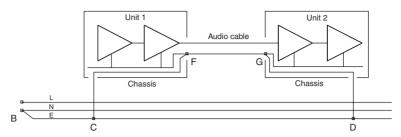

| Ground loops: how they work and how to deal with them |     |

| Hum injection by mains grounding currents             |     |

| Hum injection by transformer stray magnetic fields    |     |

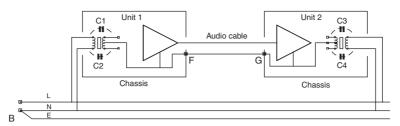

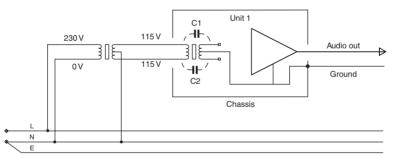

| Hum injection by transformer stray capacitance        | 491 |

| Ground currents inside equipment                      |     |

| Balanced mains power                                  | 493 |

| Class-I and Class-II                                  | 494 |

| Warning                                               | 495 |

| Cooling                                               | 495 |

| Convection cooling                                    | 496 |

| Heat-sink materials                                   | 497 |

| Heat-sink compounds                                   | 499 |

| Thermal washers                                       | 499 |

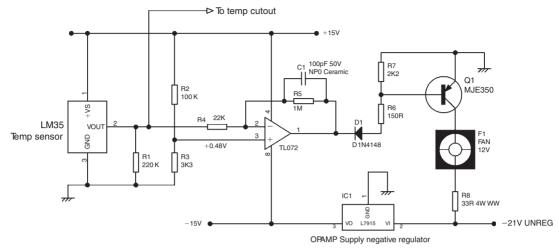

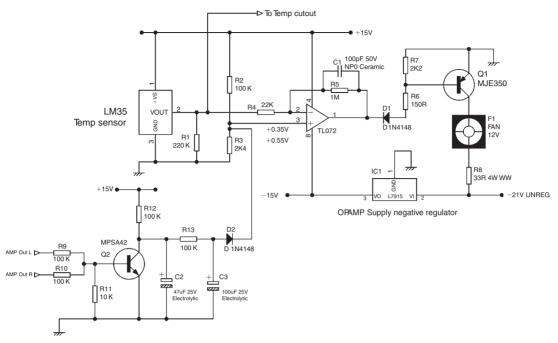

| Fan cooling                                           | 500 |

| Fan control systems                                   | 501 |

| Fan failure safety measures                           | 504 |

| Heat pipes                                            | 504 |

| Mechanical layout and design considerations           | 505 |

| Wiring layout                                         | 505 |

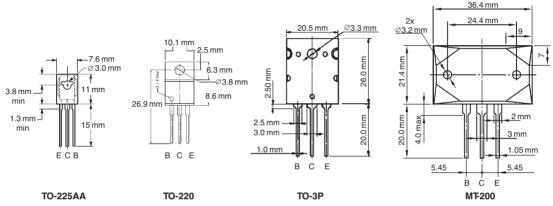

| Semiconductor installation                            | 505 |

| Chapter 19 Testing and safety    | 509 |

|----------------------------------|-----|

| Testing and fault-finding        |     |

| Powering up for the first time   | 511 |

| Safety when working on equipment | 512 |

| Warning                          | 513 |

| Safety regulations               | 513 |

| Electrical safety                |     |

| Shocks from the mains plug       |     |

| Touch current                    | 517 |

| Case openings                    | 517 |

| Equipment temperature and safety | 517 |

| Touching hot parts               |     |

| Instruction manuals              |     |

| Chapter 20 Power amplifier input systems |  |

|------------------------------------------|--|

| External signal levels                   |  |

| Internal signal levels                   |  |

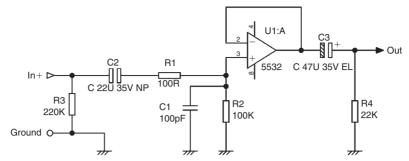

| The choice of op-amps                    |  |

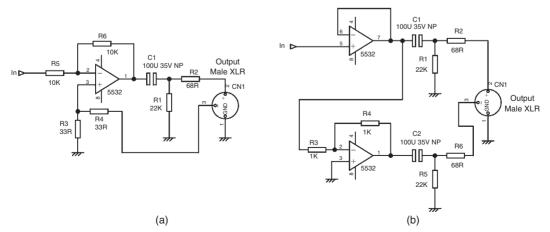

| Unbalanced inputs                        |  |

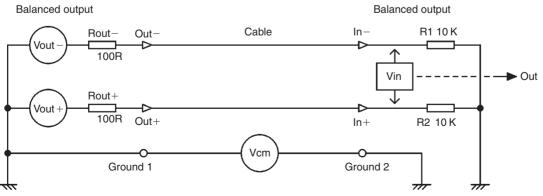

| Balanced interconnections                         |     |

|---------------------------------------------------|-----|

| Advantages                                        | 527 |

| Disadvantages                                     |     |

| Common-mode rejection ratio                       | 530 |

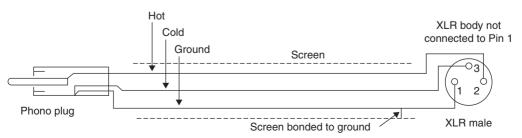

| Balanced connectors                               | 532 |

| Balanced signal levels                            |     |

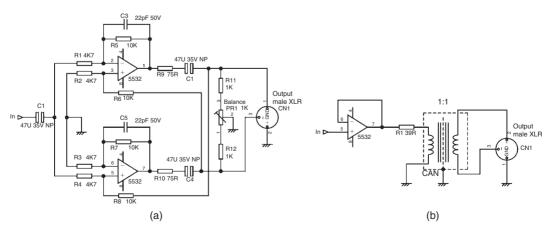

| Balanced inputs: electronic versus transformer    | 533 |

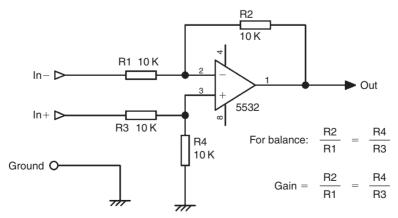

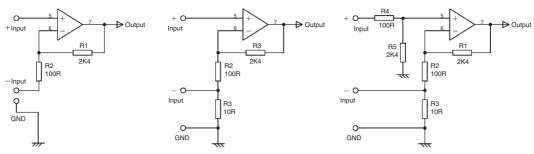

| The basic balanced input                          | 533 |

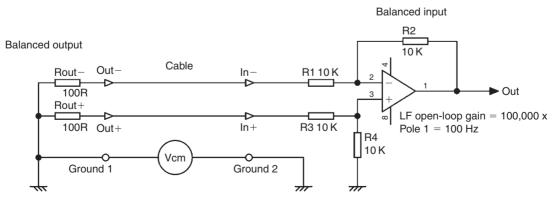

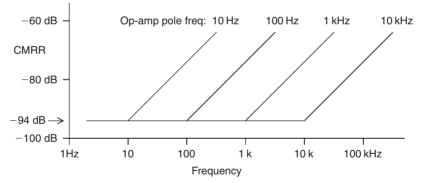

| Common-mode rejection in the basic balanced input | 535 |

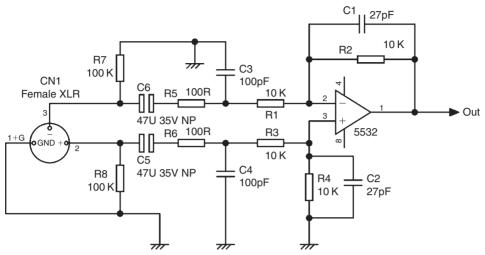

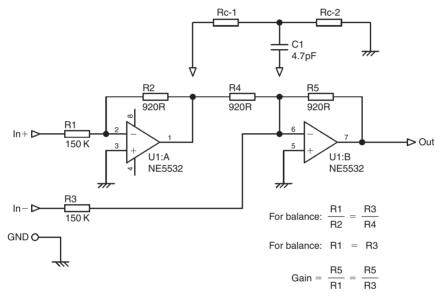

| The practical balanced input                      | 539 |

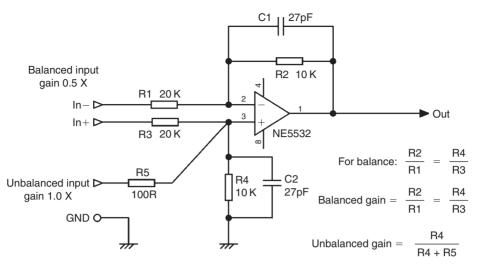

| Combined unbalanced and balanced inputs           | 540 |

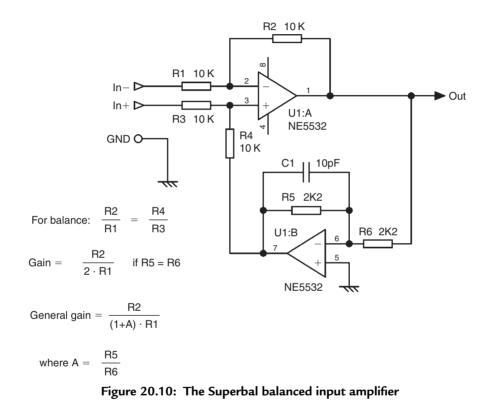

| Superbal input                                    | 541 |

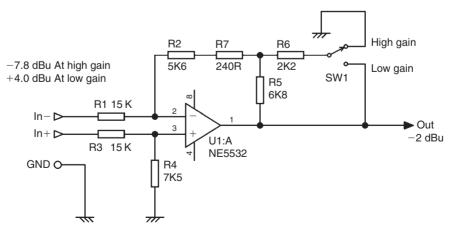

| Switched-gain balanced inputs                     | 542 |

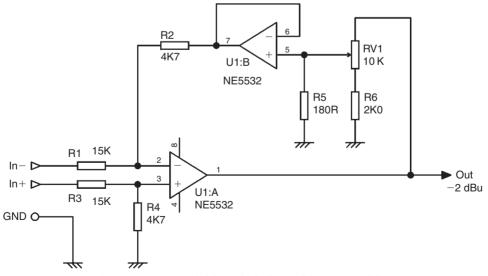

| Variable-gain balanced inputs                     | 544 |

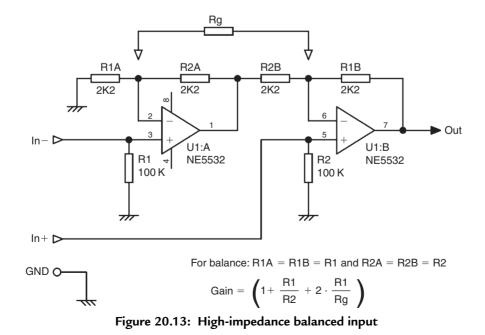

| High-impedance balanced inputs                    | 545 |

| The inverting two-op-amp input                    | 546 |

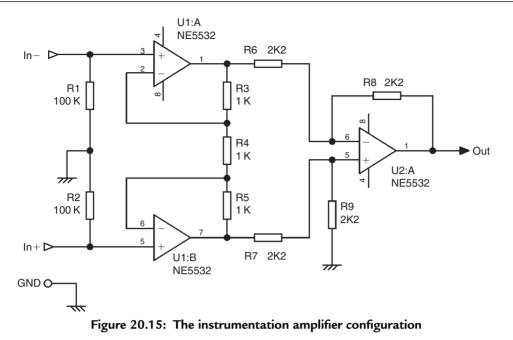

| The instrumentation amplifier                     | 546 |

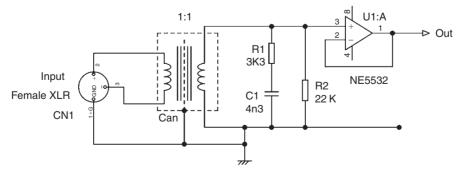

| Transformer balanced inputs                       | 548 |

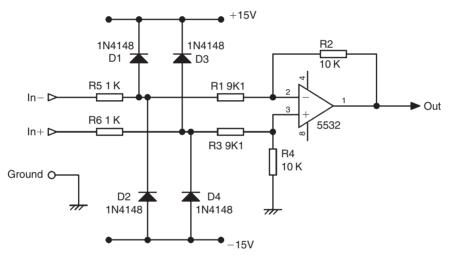

| Input overvoltage protection                      | 549 |

| Noise and the input system                        | 550 |

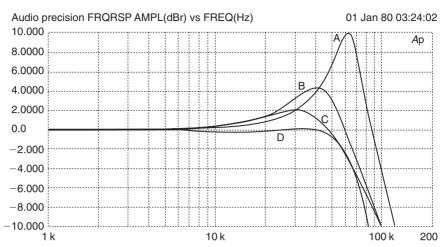

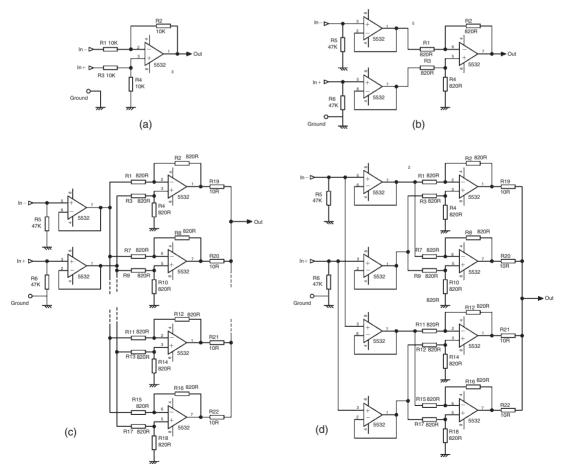

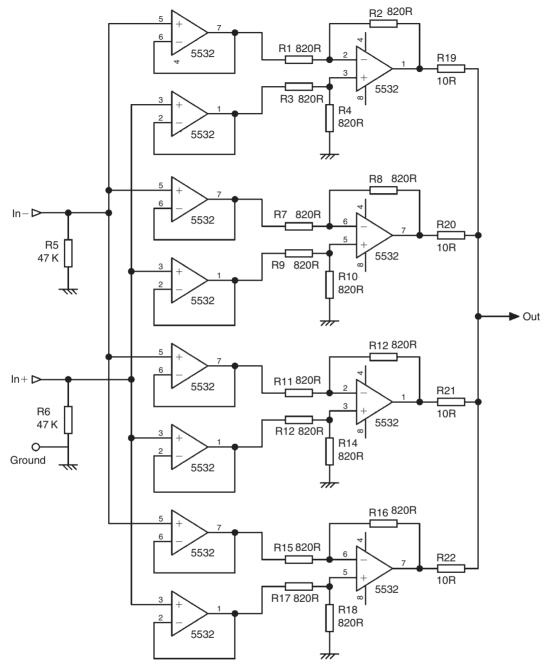

| Low-noise balanced inputs                         | 552 |

| And quieter yet                                   | 556 |

| Noise reduction in real life                      | 556 |

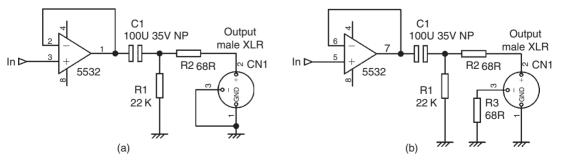

| Unbalanced and balanced outputs                   | 557 |

| Unbalanced outputs                                | 558 |

| Ground-canceling outputs                          | 559 |

| Balanced outputs                                  |     |

| Quasi-floating outputs                            |     |

| Transformer balanced outputs                      |     |

| Using a balanced power amplifier interface        |     |

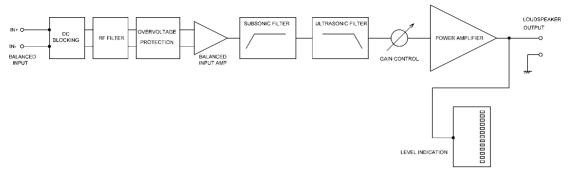

| Chapter 21 Input processing and auxiliary subsystems |  |

|------------------------------------------------------|--|

| Ground-lift switches                                 |  |

| Phase reversal facility                              |  |

| Gain control                                         |  |

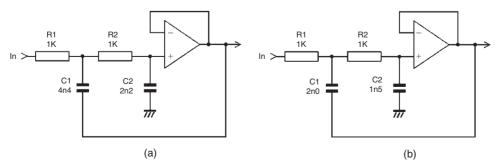

| Subsonic filtering: high-pass                        |  |

| Ultrasonic filtering: low-pass                       |  |

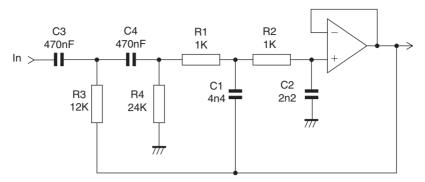

| Combined filters                                     |  |

| Electronic crossovers                                |  |

| Digital signal processing                            |  |

| Signal-present indication                            |  |

|                                                      |  |

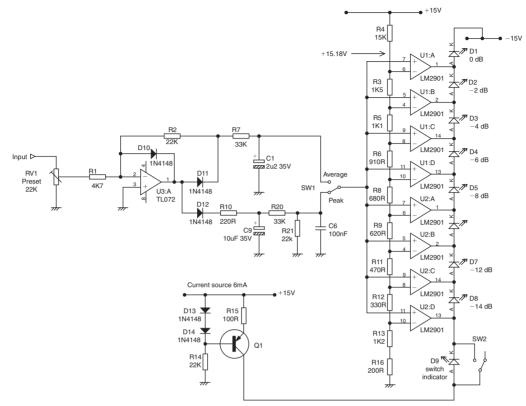

| Output level indication        |  |

|--------------------------------|--|

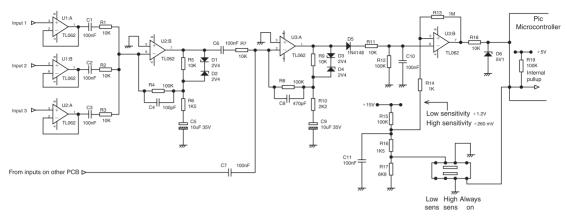

| Signal activation              |  |

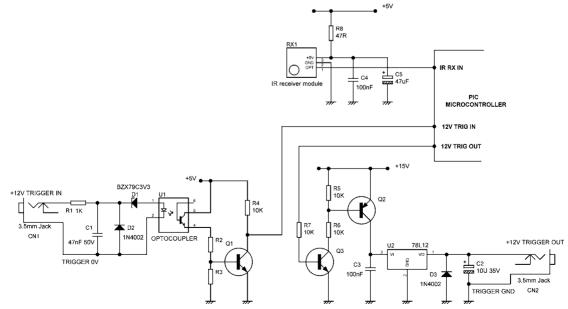

| Twelve-Volt trigger activation |  |

| Infrared remote control        |  |

| Other amplifier facilities     |  |

| *                              |  |

### Acknowledgments

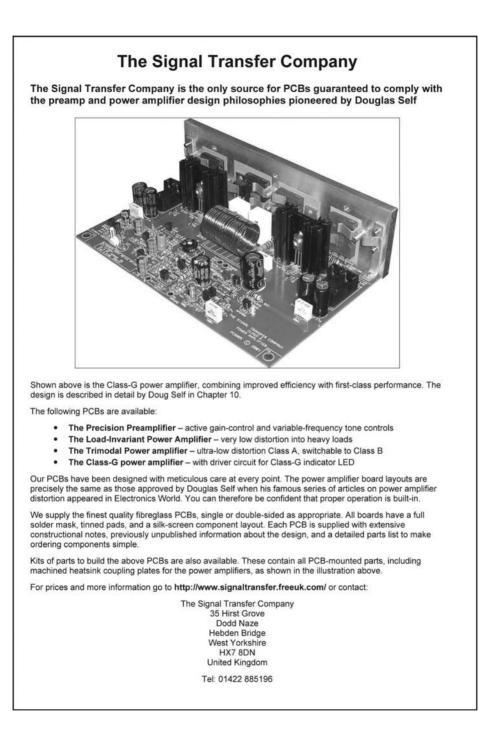

Heartfelt thanks to Gareth Connor of The Signal Transfer Company for practical help, never-failing encouragement, and for providing the facilities with which some of the experiments in this book were done.

I wish to thank Averil Donohoe for her help with some of the harder sums.

## Preface to Fifth Edition

You will have noted from the increased weight of this book that it has been significantly expanded. The text has increased in size by more than 50%, and there are a hundred new illustrations.

There is a completely new chapter on the Class-XD system that I recently introduced at Cambridge Audio; an amplifier utilizing this system won an Innovation award at Chicago CES, January 2008.

There is also a big new chapter on balanced line inputs and balanced interconnections in general. These are becoming more and more common in the hi-fi field and have always been of prime importance in professional amplifier systems. This is a vital topic as without good interconnection technology the signal quality is irrevocably compromised before it gets anywhere near the actual power amplifier stage. This chapter also includes a lot of new material on ultra-low-noise design.

There is also a wholly new chapter on amplifier subsystems such as signal activation, 12V trigger, level indication, and more. Amplifier input stages and voltage-amplifier stages now have separate chapters of their own.

I have added lots of new material on four-stage amplifier architectures, current-mirrors, power transistors with internal sensing diodes, amplifier bridging, distortion mechanisms, input stage common-mode distortion, double input stages, amplifier stability, output stages with gain, transformers and their hum fields, inrush current suppression, DC servo design, thermal protection, the subtleties of cooling fan control, line input stages, low-noise design, high- and low-pass filtering, testing and safety, infrared control, and much more. There is significantly more material on professional power amplifiers as used in sound reinforcement and PA applications.

I am aware there is still very little material on power MOSFETs in this book, as I still hold to the view that they are inevitably more nonlinear and harder to work with than bipolar transistors. I know that some people – including some I have much respect for – do not agree, but I find the evidence in both theory and practice to be convincing.

There has been some rearrangement to get a more logical layout of the subject matter. Your favorite topic has not been removed, but it might well have been moved.

As you will have gathered, I am still fascinated by the apparently simple but actually fiendishly complex business of making small signals bigger and applying them to a loudspeaker. An amplifier performs one of the simplest possible mathematical operations on a signal – multiplication by a constant. It is fascinating to see how much more complicated things get after that.

#### xx Preface to Fifth Edition

Part of the lure of electronics as a pursuit is the speed with which ideas can be turned into physical reality. In audio amplifier design, you very often need just a handful of components, a piece of prototype board, and a few minutes to see if the latest notion really is correct. If you come up with a brilliant new way of designing large concrete dams then it is going to take more than an afternoon to prove that it works.

You will also see, in Chapter 1, that in the last few years I have found no reason to alter my views on the pernicious irrationality of subjectivism. In that period I have repeatedly been involved in double-blind listening tests using experienced subjects and proper statistical analysis, which confirmed every time that if you cannot measure it you cannot hear it. Nevertheless the controversy rumbles on, although in a more logical world it would have been regarded as settled in the 1970s. I get a steady flow of emails supporting my position on this issue, but I fear I am still regarded in some quarters as the Gregor Eisenhorn of amplifier design.

There is in this book a certain emphasis on commercial manufacture, which I hope does not offend those purely interested in amateur construction or intellectual enquiry. In a commercial environment, if you want to sell something (for more than a very short time) it has to work – and keep working. This is still a valuable discipline if you are making a one-off design to test some new ideas; if the design is not reliable then it must be unsound in some way that may have more impact on what is going on than you think.

In a changing world, one of the many things that has changed is the nature of discussion on audio technologies. For many years *Wireless World* – later *Electronics World* – was a major forum for this, and I contributed many articles to it over 30 years; it has, however, now changed its emphasis. *Elektor* since its beginning has hosted serious audio articles and still does. The biggest change is of course the arrival of the Internet, which allows debate to proceed at a lightning pace compared with the old method of writing a letter and waiting for a month or two to see it published. Currently the only bulletin-board I frequent is DIYaudio.com; I personally think it is one of the best.

In producing this edition of the book it struck me frequently and forcibly how much has had to be omitted for reasons of space, despite the generous increase in its size. Audio power amplifier design, even if confined to solid-state amplifiers, and even if further confined to those with bipolar output stages, is already too big a field for one person to know everything. I certainly don't think I do.

The journey continues.

Douglas Self

### **Abbreviations**

I have kept the number of abbreviations used to a minimum. However, those few are used extensively, so a list is given in case they are not all blindingly obvious:

| BJT    | Bipolar junction transistor                                                                                                     |

|--------|---------------------------------------------------------------------------------------------------------------------------------|

| CFP    | Complementary feedback pair                                                                                                     |

| C/L    | Closed loop                                                                                                                     |

| СМ     | Common mode                                                                                                                     |

| CMOS   | Complementary metal oxide semiconductor                                                                                         |

| CMRR   | Common-mode rejection ratio                                                                                                     |

| CTF    | Current timing factor                                                                                                           |

| DF     | Damping factor                                                                                                                  |

| DSP    | Digital signal processing                                                                                                       |

| EF     | Emitter-follower                                                                                                                |

| EFA    | Emitter-follower added                                                                                                          |

| EIN    | Equivalent input noise                                                                                                          |

| ESR    | Equivalent series resistance                                                                                                    |

| FEA    | Finite element analysis                                                                                                         |

| FET    | Field-effect transistor                                                                                                         |

| HF     | Amplifier behavior above the dominant pole frequency, where the open-loop gain                                                  |

|        | is usually falling at 6 dB/octave                                                                                               |

| IAE    | Integrated absolute error                                                                                                       |

| IC     | Integrated circuit                                                                                                              |

| IGBT   | Insulated-gate bipolar transistor                                                                                               |

| I/P    | Input                                                                                                                           |

| ISE    | Integrated square error                                                                                                         |

| LED    | Light-emitting diode                                                                                                            |

| LF     | Relating to amplifier action below the dominant pole, where the open-loop gain is assumed to be essentially flat with frequency |

| LSN    | Large-signal nonlinearity                                                                                                       |

| MOSFET | Metal oxide semiconductor field-effect transistor                                                                               |

| NF     | Noise figure                                                                                                                    |

| NFB        | Negative feedback                                                                 |

|------------|-----------------------------------------------------------------------------------|

| O/L        | Open loop                                                                         |

| O/P        | Output                                                                            |

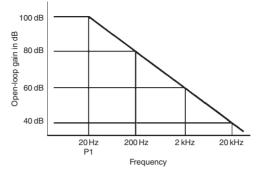

| <i>P</i> 1 | The first O/L response pole, and its frequency in Hz (i.e. the $-3 dB$ point of a |

|            | 6 dB/octave roll-off)                                                             |

| P2         | The second response pole, at a higher frequency                                   |

| PA         | Public address                                                                    |

| PCB        | Printed-circuit board                                                             |

| PDF        | Probability density function                                                      |

| PPD        | Power partition diagram                                                           |

| PSRR       | Power-supply rejection ratio                                                      |

| PSU        | Power-supply unit                                                                 |

| PWM        | Pulse width modulation                                                            |

| RF         | Radio frequency                                                                   |

| SID        | Slew-induced distortion                                                           |

| SOA, SOAR  | Safe operating area                                                               |

| SPL        | Sound pressure level                                                              |

| Tempco     | Temperature coefficient                                                           |

| THD        | Total harmonic distortion                                                         |

| TID        | Transient intermodulation distortion                                              |

| TIM        | Transient intermodulation                                                         |

| VAS        | Voltage-amplifier stage                                                           |

| VCIS       | Voltage-controlled current source                                                 |

| VCVS       | Voltage-controlled voltage source                                                 |

| VI         | Voltage/current                                                                   |

## Introduction and General Survey

### The Economic Importance of Power Amplifiers

Audio power amplifiers are of considerable economic importance. They are built in their hundreds of thousands every year, and have a history extending back to the 1920s. It is therefore surprising there have been so few books dealing in any depth with solid-state power amplifier design.

The first aim of this text is to fill that need, by providing a detailed guide to the many design decisions that must be taken when a power amplifier is designed.

The second aim is to disseminate the results of the original work done on amplifier design in the last few years. The unexpected result of these investigations was to show that power amplifiers of extraordinarily low distortion could be designed as a matter of routine, without any unwelcome side-effects, so long as a relatively simple design methodology was followed. This methodology will be explained in detail.

#### Assumptions

To keep its length reasonable, a book such as this must assume a basic knowledge of audio electronics. I do not propose to plough through the definitions of frequency response, total harmonic distortion (THD) and signal-to-noise ratio; these can be found anywhere. Commonplace facts have been ruthlessly omitted where their absence makes room for something new or unusual, so this is not the place to start learning electronics from scratch. Mathematics has been confined to a few simple equations determining vital parameters such as open-loop gain; anything more complex is best left to a circuit simulator you trust. Your assumptions, and hence the output, may be wrong, but at least the calculations in between will be correct . . .

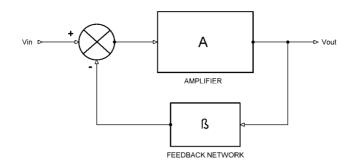

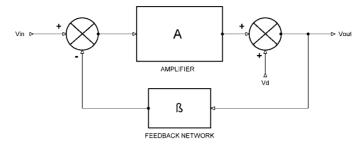

The principles of negative feedback as applied to power amplifiers are explained in detail, as there is still widespread confusion as to exactly how it works.

#### Origins and Aims

The core of this book is based on a series of eight articles originally published in *Electronics World* as 'Distortion in Power Amplifiers'. This series was primarily concerned with distortion as the most variable feature of power amplifier performance. You may have two units placed side by side,

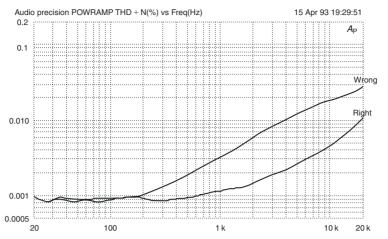

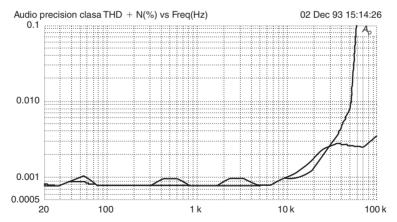

one giving 2% THD and the other 0.0005% at full power, and both claiming to provide the ultimate audio experience. The ratio between the two figures is a staggering 4000:1, and this is clearly a remarkable state of affairs. One might be forgiven for concluding that distortion was not a very important parameter. What is even more surprising to those who have not followed the evolution of audio over the last two decades is that the more distortive amplifier will almost certainly be the more expensive. I shall deal in detail with the reasons for this astonishing range of variation.

The original series was inspired by the desire to invent a new output stage that would be as linear as Class-A, without the daunting heat problems. In the course of this work it emerged that output stage distortion was completely obscured by nonlinearities in the small-signal stages, and it was clear that these distortions would need to be eliminated before any progress could be made. The small-signal stages were therefore studied in isolation, using *model* amplifiers with low-power and very linear Class-A output stages, until the various overlapping distortion mechanisms had been separated out. It has to be said this was not an easy process. In each case there proved to be a simple, and sometimes well-known, cure and perhaps the most novel part of my approach is that all these mechanisms are dealt with, rather than one or two, and the final result is an amplifier with unusually low distortion, using only modest and safe amounts of global negative feedback.

Much of this book concentrates on the distortion performance of amplifiers. One reason is that this varies more than any other parameter – by up to a factor of 1000. Amplifier distortion was until recently an enigmatic field – it was clear that there were several overlapping distortion mechanisms in the typical amplifier, but it is the work reported here that shows how to disentangle them, so they may be separately studied and then, with the knowledge thus gained, minimized.

I assume here that distortion is a bad thing, and should be minimized; I make no apology for putting it as plainly as that. Alternative philosophies hold that as some forms of nonlinearity are considered harmless or even euphonic, they should be encouraged, or at any rate not positively discouraged. I state plainly that I have no sympathy with the latter view; to my mind the goal is to make the audio path as transparent as possible. If some sort of distortion is considered desirable, then surely the logical way to introduce it is by an outboard processor, working at line level. This is not only more cost-effective than generating distortion with directly heated triodes, but has the important attribute that *it can be switched off*. Those who have brought into being our current signal-delivery chain, i.e. mixing consoles, multitrack recorders, CDs, etc., have done us proud in the matter of low distortion, and to willfully throw away this achievement at the very last stage strikes me as curious at best.

In this book I hope to provide information that is useful to all those interested in power amplifiers. Britain has a long tradition of small and very small audio companies, whose technical and production resources may not differ very greatly from those available to the committed amateur. I hope this volume will be of service to both.

I have endeavored to address both the quest for technical perfection – which is certainly not over, as far as I am concerned – and also the commercial necessity of achieving good specifications at minimum cost.

The field of audio is full of statements that appear plausible but in fact have never been tested and often turn out to be quite untrue. For this reason, I have confined myself as closely as possible to facts that I have verified myself. This volume may therefore appear somewhat idiosyncratic in places. For example, field-effect transistor (FET) output stages receive much less coverage than bipolar ones because the conclusion appears to be inescapable that FETs are both more expensive and less linear; I have therefore not pursued the FET route very far. Similarly, most of my practical design experience has been on amplifiers of less than 300W power output, and so heavy-duty designs for large-scale public address (PA) work are also under-represented. I think this is preferable to setting down untested speculation.

### The Study of Amplifier Design

Although solid-state amplifiers have been around for some 40 years, it would be a great mistake to assume that everything possible is known about them. In the course of my investigations, I discovered several matters which, not appearing in the technical literature, appear to be novel, at least in their combined application:

- The need to precisely balance the input pair to prevent second-harmonic generation.

- The demonstration of how a beta-enhancement transistor increases the linearity and reduces the collector impedance of the voltage-amplifier stage (VAS).

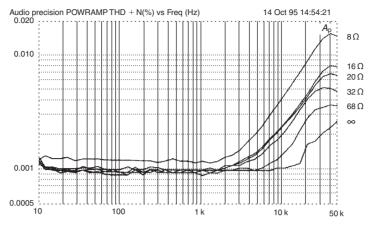

- An explanation of why BJT output stages always distort more into  $4\Omega$  than  $8\Omega$ .

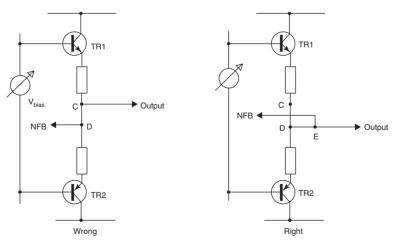

- In a conventional BJT output stage, quiescent current as such is of little importance. What is crucial is the voltage between the transistor emitters.

- Power FETs, though for many years touted as superior in linearity, are actually far less linear than bipolar output devices.

- In most amplifiers, the major source of distortion is not inherent in the amplifying stages, but results from avoidable problems such as induction of supply-rail currents and poor power-supply rejection.