# **Nios® V Embedded Processor Design Handbook**

Updated for Intel® Quartus® Prime Design Suite: 23.4

# **Contents**

| 1. Ab  | out the Nios® V Embedded Processor                                             | 5  |

|--------|--------------------------------------------------------------------------------|----|

|        | 1.1. Intel® FPGA and Embedded Processors Overview                              | 5  |

|        | 1.2. Intel Quartus® Prime Software Support                                     | 6  |

|        | 1.3. Nios V Processor Licensing                                                | 6  |

|        | 1.4. Embedded System Design                                                    |    |

|        | 1.5. Nios V Processor Quick Start Guide                                        |    |

|        | 1.5.1. System Requirements                                                     |    |

|        | 1.5.2. Nios V Processor Example Design                                         |    |

|        | 1.5.3. Software Design Flow                                                    |    |

|        | 1.5.4. Programming Nios V into the FPGA Device                                 | 14 |

| 2. Nic | os V Processor Hardware System Design with Intel Quartus Prime Software and    |    |

|        | Platform Designer                                                              |    |

|        | 2.1. Creating Nios V Processor System Design with Platform Designer            |    |

|        | 2.1.1. Instantiating Nios V Processor Intel FPGA IP                            |    |

|        | 2.1.2. Defining System Component Design                                        |    |

|        | 2.1.3. Specifying Base Addresses and Interrupt Request Priorities              |    |

|        | 2.2. Integrating Platform Designer System into the Intel Quartus Prime Project | 2/ |

|        | Prime Project                                                                  | 27 |

|        | 2.2.2. Connecting Signals and Assigning Physical Pin Locations                 |    |

|        | 2.2.3. Constraining the Intel FPGA Design                                      |    |

|        | 2.3. Designing a Nios V Processor Memory System                                |    |

|        | 2.3.1. Volatile Memory                                                         |    |

|        | 2.3.2. Non-Volatile Memory                                                     |    |

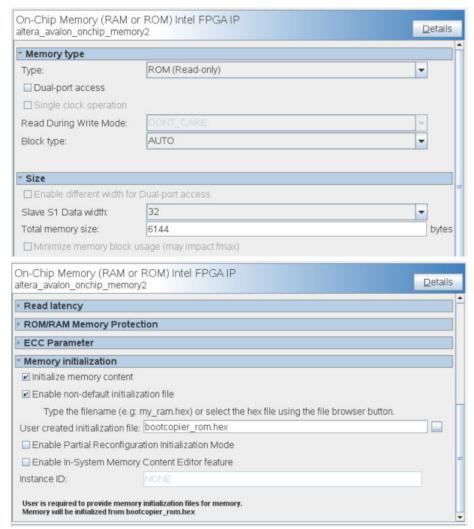

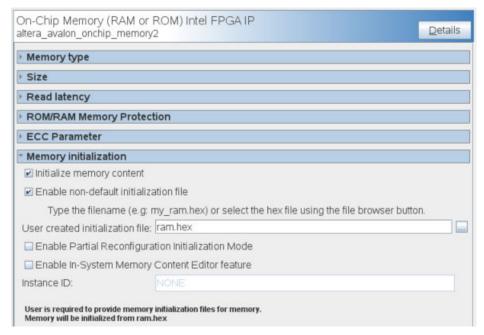

|        | 2.3.3. On-Chip Memory Configuration – RAM or ROM                               |    |

|        | 2.4. Clocks and Resets Best Practices                                          |    |

|        | 2.4.1. Reset Request Interface                                                 |    |

|        | 2.5. Assigning a Default Agent                                                 | 31 |

| 3. Nic | os V Processor Software System Design                                          | 32 |

|        | 3.1. Nios V Processor Software Development Flow                                |    |

|        | 3.1.1. Board Support Package Project                                           |    |

|        | 3.1.2. Application Project                                                     |    |

|        | 3.2. Intel FPGA Embedded Development Tools                                     |    |

|        | 3.2.1. Nios V Processor Board Support Package Editor                           |    |

|        | 3.2.2. RiscFree IDE for Intel FPGAs                                            |    |

|        | 3.2.3. Eclipse CDT for Embedded C/C++ Developer                                |    |

|        | 3.2.4. Nios V Utilities Tools                                                  |    |

|        | 3.2.6. Other Utilities Tools                                                   |    |

|        |                                                                                |    |

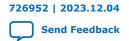

| 4. Nic | os V Processor Configuration and Booting Solutions                             |    |

|        | 4.1. Introduction                                                              |    |

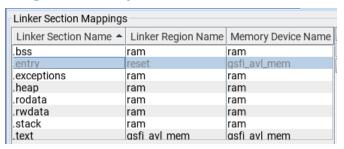

|        | 4.2. Linking Applications                                                      |    |

|        | 4.2.1. Linking Behavior                                                        |    |

|        | 4.4. Introduction to Nios V Processor Booting Methods                          |    |

|        | T.T. IIII UUUCUUII W WIUS V FIUCESSUI DUUUIIU MEUUUS                           | 41 |

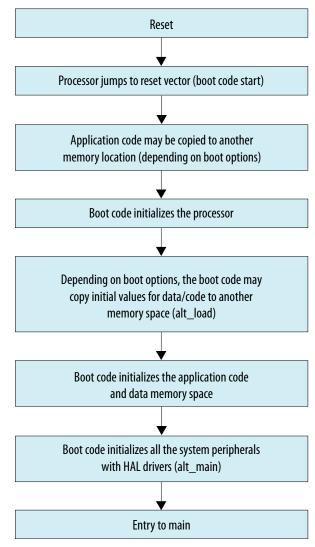

|       | 4.4.1. Nios V Processor Application Execute-In-Place from Boot Flash                    | 42  |

|-------|-----------------------------------------------------------------------------------------|-----|

|       | 4.4.2. Nios V Processor Application Copied from Boot Flash to RAM Using Boot            |     |

|       | Copier                                                                                  |     |

|       | 4.4.3. Nios V Processor Application Execute-In-Place from OCRAM                         |     |

|       | 4.4.4. Nios V Processor Application Execute-In-Place from TCM                           |     |

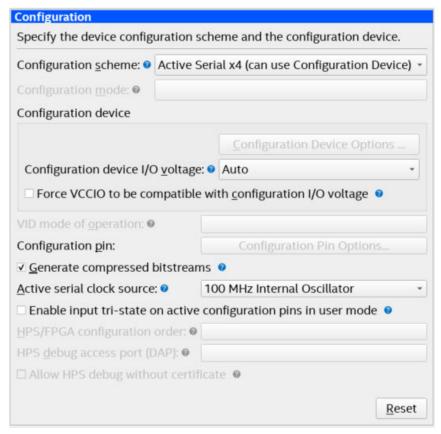

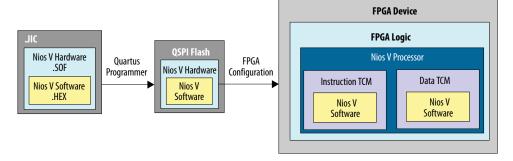

|       | 4.5. Nios V Processor Booting from Configuration QSPI Flash                             | 46  |

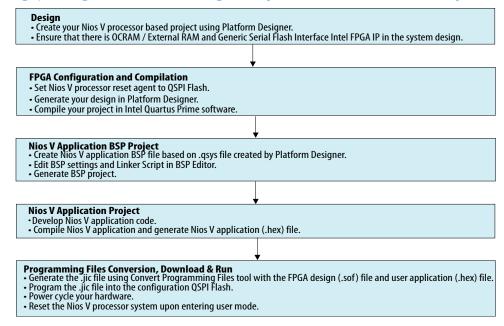

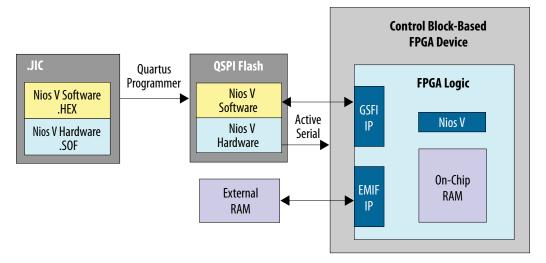

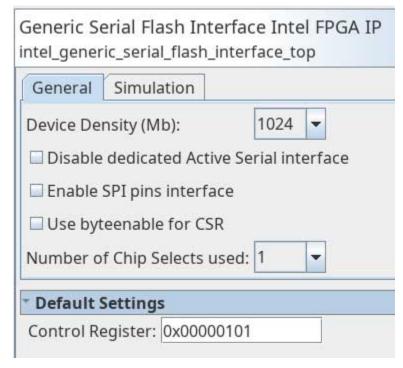

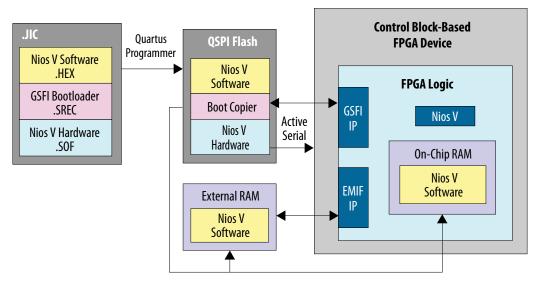

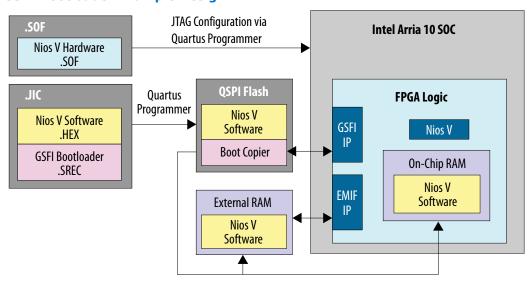

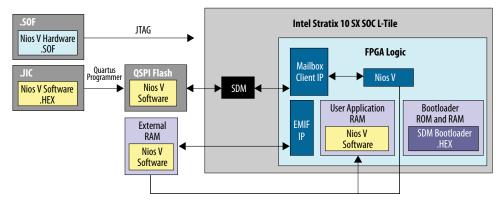

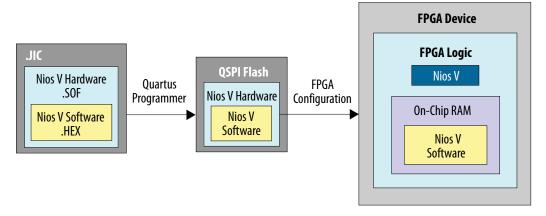

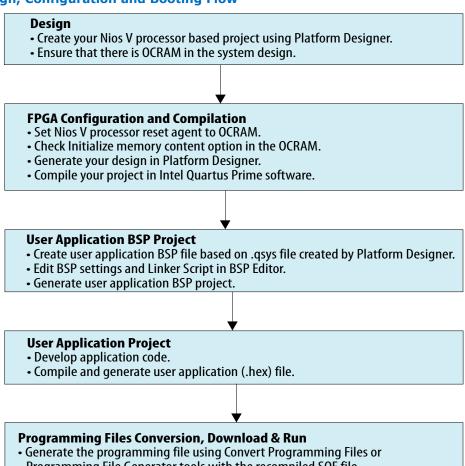

|       | 4.5.1. Nios V Processor Design, Configuration and Boot Flow (Control Blockbased Device) | 47  |

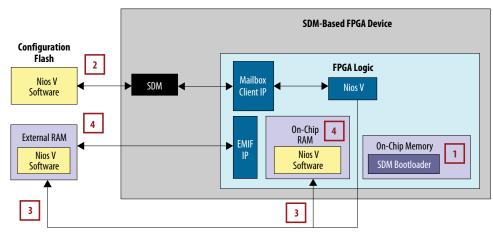

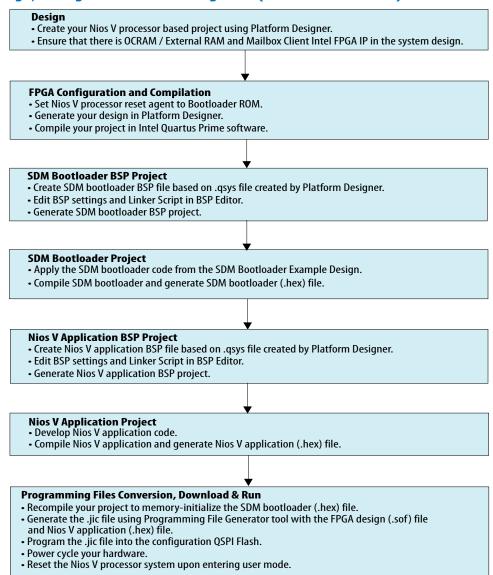

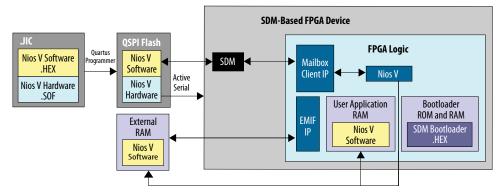

|       | 4.5.2. Nios V Processor Design, Configuration and Boot Flow (SDM-based Devices          |     |

|       | 4.6. Nios V Processor Booting from On-Chip Memory (OCRAM)                               |     |

|       | 4.6.1. Nios V Processor Application Executes in-place from OCRAM                        |     |

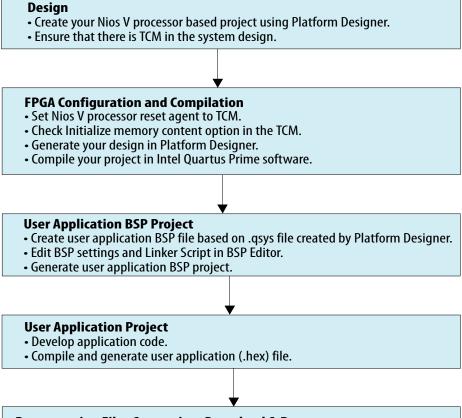

|       | 4.7. Nios V Processor Booting from Tightly Coupled Memory (TCM)                         |     |

|       | 4.7.1. Nios V Processor Application Executes in-place from TCM                          |     |

|       | 4.8. Summary of Nios V Processor Vector Configuration and BSP Settings                  |     |

|       |                                                                                         |     |

| 5. Ni | ios V Processor - Using the MicroC/TCP-IP Stack                                         |     |

|       | 5.1. Introduction                                                                       |     |

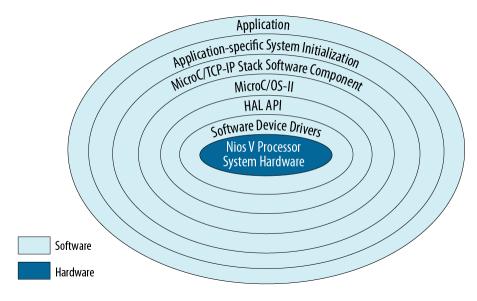

|       | 5.2. Software Architecture                                                              |     |

|       | 5.3. Support and Licensing                                                              |     |

|       | 5.4. MicroC/TCP-IP Example Designs                                                      |     |

|       | 5.4.1. Hardware and Software Requirements                                               |     |

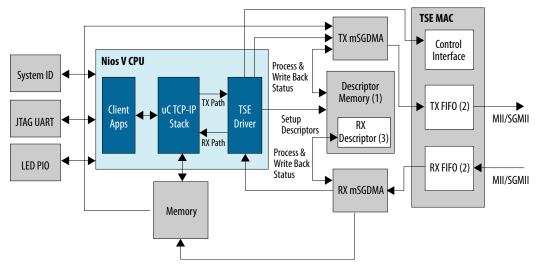

|       | 5.4.2. Overview                                                                         |     |

|       | 5.4.3. Acquiring the Example Design Files                                               |     |

|       | 5.4.4. Hardware Design Files                                                            |     |

|       | 5.4.5. Software Design Files                                                            |     |

|       | 5.5. Development Flow                                                                   |     |

|       | 5.5.1. Hardware Development Flow                                                        |     |

|       | 5.5.2. Software Development Flow                                                        |     |

|       | 5.5.3. Device Programming                                                               |     |

|       | 5.6. Operating the Example Designs                                                      |     |

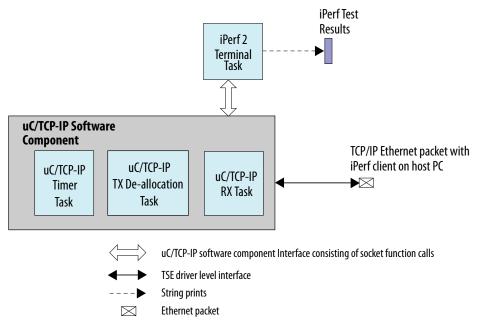

|       | 5.6.1. Operating the MicroC/TCP-IP IPerf                                                |     |

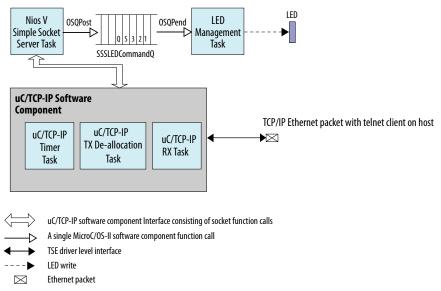

|       | 5.6.2. Operating the MicroC/TCP-IP Simple Socket Server                                 |     |

|       | 5.7. Optional Configuration                                                             |     |

|       | 5.7.1. Configuring Hardware Name                                                        |     |

|       | 5.7.2. Configuring MAC and IP Addresses                                                 |     |

|       | 5.7.3. Configuring MicroC/TCP-IP Initialization                                         |     |

|       | 5.7.4. Configuring iPerf Server Auto-Initialization                                     |     |

|       | 5.8. MicroC/TCP-IP Simple Socket Server Concepts                                        |     |

|       | 5.8.1. MicroC/OS-II Resources                                                           |     |

|       | 5.8.2. Error Handling                                                                   |     |

|       | 5.8.3. MicroC/TCP-IP Stack Default Configuration                                        | 129 |

| 6. Ni | ios V Processor Debugging, Verifying, and Simulating                                    | 130 |

|       | 6.1. Debugging Nios V/c Processor                                                       |     |

|       | 6.1.1. Steps to Debug Nios V/c Processor                                                |     |

|       | 6.2. Debugging Nios V Processor Software Designs                                        |     |

|       | 6.2.1. OpenOCD and Eclipse Embedded CDT                                                 |     |

|       | 6.2.2. Objdump File                                                                     | 132 |

|       | 6.2.3. Show Make Commands                                                               |     |

|       | 6.3. Debugging Tools                                                                    |     |

|       | 6.4. Additional Embedded Design Considerations                                          |     |

|       | 6.4.1. JTAG Signal Integrity                                                            |     |

|       | - · · · · · · · · · · · · · · · · · · ·                                                 |     |

|        | 6.4.2. Additional Memory Space for System Prototyping                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

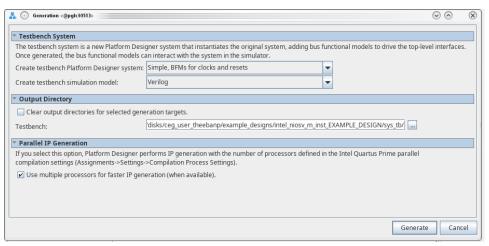

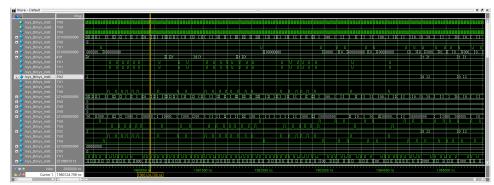

|        | 6.5. Simulating Nios V Processor Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                         |

|        | 6.5.1. Prerequisites                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                         |

|        | 6.5.2. Setting Up and Generating Your Simulation Environment in Platform Designer                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

|        | 6.5.3. Creating Nios V Processor Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

|        | 6.5.4. Generating Memory Initialization File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|        | 6.5.5. Generating System Simulation Files                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

|        | 6.5.6. Running Simulation in the QuestaSim Simulator Using Command Line                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                         |

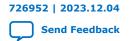

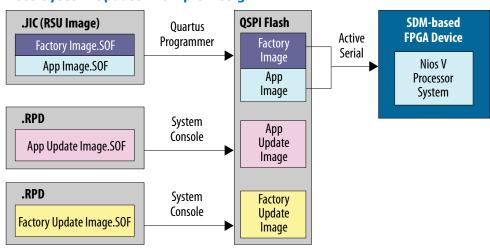

| 7. Nio | s V Processor — Remote System Update1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                         |

|        | 7.1. Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|        | 7.2. Intel Quartus Prime Pro Edition Software and Tool Support                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                         |

|        | 7.2.1. Intel <sup>®</sup> Quartus <sup>®</sup> Prime Pro Edition Software                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

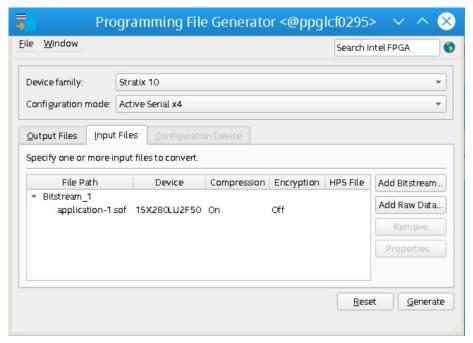

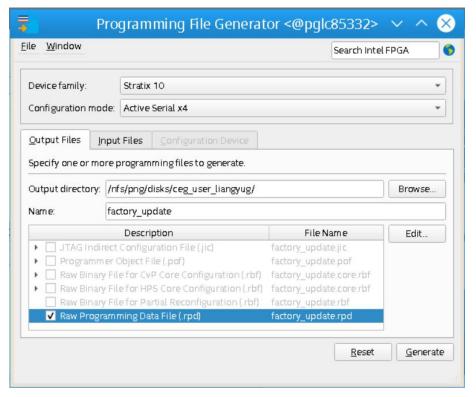

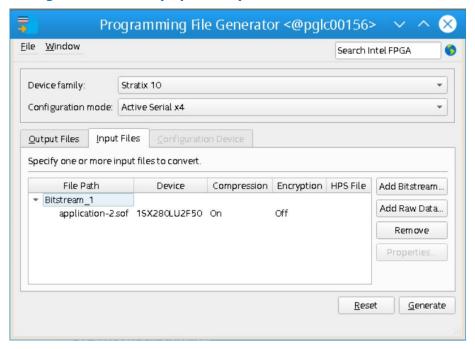

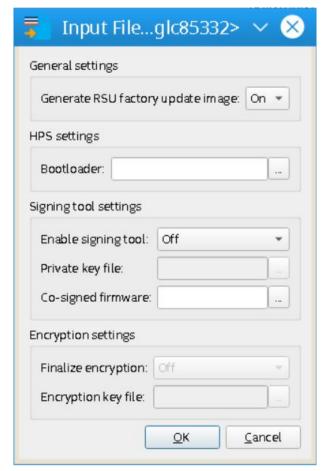

|        | 7.2.2. Programming File Generator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                         |

|        | 7.3. Nios V Processor RSU Quick Start Guide in SDM-based Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                         |

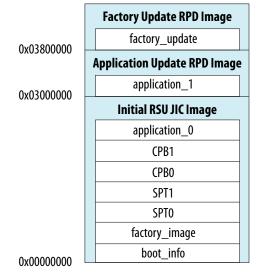

|        | 7.3.1. Individual Factory, Application, and Update Images                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

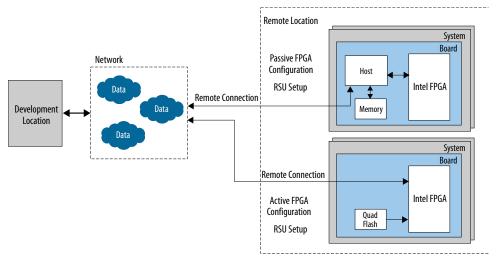

|        | 7.3.2. Hardware Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|        | 7.3.3. Individual Images Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |

|        | 7.3.4. Remote System Update Image Files Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                         |

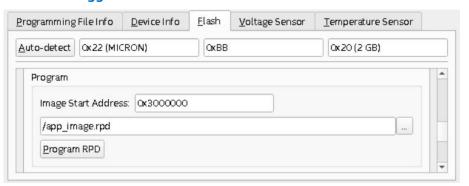

|        | 7.3.5. QSPI Flash Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                         |

|        | 7.3.6. Operating the RSU Client API                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 162                                                                                     |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                         |

|        | s V Processor — Using Custom Instruction1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                         |

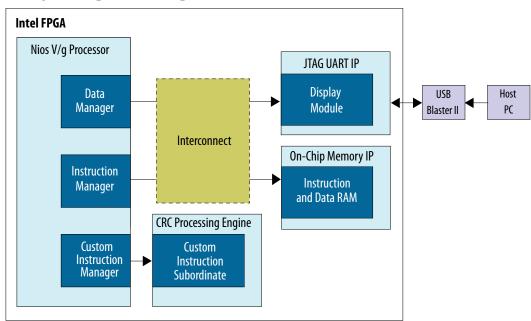

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166                                                                                     |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166                                                                              |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>166                                                                       |

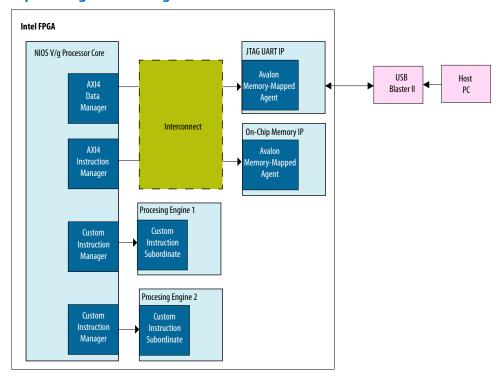

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>166<br>167                                                                |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>166<br>167<br>167                                                         |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>166<br>167<br>167<br>167                                                  |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>166<br>167<br>167<br>167                                                  |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>167<br>167<br>167<br>169                                                  |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>167<br>167<br>167<br>169<br>169                                           |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>167<br>167<br>167<br>169<br>170                                           |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>172                                    |

|        | 8.1. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>172<br>173                             |

|        | 8.1. Introduction. 8.2. Unimplemented Instruction Example Design. 8.2.1. Hardware and Software Requirements. 8.2.2. Overview. 8.2.3. Acquiring the Example Design File. 8.2.4. Hardware Design Files. 8.2.5. Software Design Files. 8.2.6. Development Flow. 8.2.7. Operating the Example Design. 8.3. Hardware Acceleration Example Design. 8.3.1. Hardware and Software Requirements. 8.3.2. Overview. 8.3.3. Acquiring the Example Design File.                                                                           | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>172<br>173<br>173                      |

|        | 8.1. Introduction 8.2. Unimplemented Instruction Example Design 8.2.1. Hardware and Software Requirements 8.2.2. Overview 8.2.3. Acquiring the Example Design File 8.2.4. Hardware Design Files 8.2.5. Software Design Files 8.2.6. Development Flow 8.2.7. Operating the Example Design 8.3. Hardware Acceleration Example Design 8.3.1. Hardware and Software Requirements 8.3.2. Overview 8.3.3. Acquiring the Example Design File 8.3.4. Hardware Design Files                                                           | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>172<br>173<br>173<br>173               |

|        | 8.1. Introduction.  8.2. Unimplemented Instruction Example Design.  8.2.1. Hardware and Software Requirements.  8.2.2. Overview.  8.2.3. Acquiring the Example Design File.  8.2.4. Hardware Design Files.  8.2.5. Software Design Files.  8.2.6. Development Flow.  8.2.7. Operating the Example Design.  8.3. Hardware Acceleration Example Design.  8.3.1. Hardware and Software Requirements.  8.3.2. Overview.  8.3.3. Acquiring the Example Design File.  8.3.4. Hardware Design Files.  8.3.5. Software Design Files. | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>172<br>173<br>173<br>173<br>174        |

|        | 8.1. Introduction 8.2. Unimplemented Instruction Example Design 8.2.1. Hardware and Software Requirements 8.2.2. Overview 8.2.3. Acquiring the Example Design File 8.2.4. Hardware Design Files 8.2.5. Software Design Files 8.2.6. Development Flow 8.2.7. Operating the Example Design 8.3.1. Hardware Acceleration Example Design 8.3.2. Overview 8.3.3. Acquiring the Example Design File 8.3.4. Hardware Design Files 8.3.5. Software Design Files 8.3.6. Development Flow                                              | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>173<br>173<br>173<br>174<br>174        |

|        | 8.1. Introduction 8.2. Unimplemented Instruction Example Design 8.2.1. Hardware and Software Requirements 8.2.2. Overview 8.2.3. Acquiring the Example Design File 8.2.4. Hardware Design Files 8.2.5. Software Design Files 8.2.6. Development Flow 8.2.7. Operating the Example Design 8.3.1. Hardware Acceleration Example Design 8.3.2. Overview 8.3.3. Acquiring the Example Design File 8.3.4. Hardware Design Files 8.3.5. Software Design Files 8.3.6. Development Flow 8.3.7. Operating the Example Design          | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>173<br>173<br>173<br>174<br>175<br>176 |

|        | 8.1. Introduction 8.2. Unimplemented Instruction Example Design 8.2.1. Hardware and Software Requirements 8.2.2. Overview 8.2.3. Acquiring the Example Design File 8.2.4. Hardware Design Files 8.2.5. Software Design Files 8.2.6. Development Flow 8.2.7. Operating the Example Design 8.3.1. Hardware Acceleration Example Design 8.3.2. Overview 8.3.3. Acquiring the Example Design File 8.3.4. Hardware Design Files 8.3.5. Software Design Files 8.3.6. Development Flow                                              | 166<br>166<br>167<br>167<br>167<br>169<br>170<br>173<br>173<br>173<br>174<br>175<br>176 |

# 1. About the Nios® V Embedded Processor

## 1.1. Intel® FPGA and Embedded Processors Overview

Intel FPGA devices can implement logic that functions as a complete microprocessor while providing many options.

An important difference between discrete microprocessors and Intel FPGA is that Intel FPGA fabric contains no logic when it powers up. Before you run software on a Nios® V processor based system, you must configure the Intel FPGA device with a hardware design that contains a Nios V processor. The Nios V processor is a soft intellectual property (IP) processor based on the RISC-V specification. You can place the Nios V processor anywhere on the Intel FPGA, depending on the requirements of the design.

To enable your Intel® FPGA IP-based embedded system to behave as a discrete microprocessor-based system, your system should include the following:

- A JTAG interface to support Intel FPGA configuration, hardware and software debugging

- A power-up Intel FPGA configuration mechanism

If your system has these capabilities, you can begin refining your design from a pretested hardware design loaded in the Intel FPGA. Using an Intel FPGA also allows you to modify your design quickly to address problems or to add new functionality. You can test these new hardware designs easily by reconfiguring the Intel FPGA using your system's JTAG interface.

The JTAG interface supports hardware and software development. You can perform the following tasks using the JTAG interface:

- Configure the Intel FPGA

- Download and debug software

- Communicate with the Intel FPGA through a UART-like interface (JTAG UART

- Debug hardware (with the Signal Tap embedded logic analyzer)

- Program flash memory

After you configure the Intel FPGA with a Nios V processor-based design, the software development flow is similar to the flow for discrete microcontroller designs.

#### **Related Information**

- Nios V Processor Reference Manual Provides information about the Nios V processor performance benchmarks, processor architecture, the programming model, and the core implementation.

- Embedded Peripherals IP User Guide

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

Nios V Processor Software Developer Handbook

Describes the Nios V processor software development environment, the tools that are available, and the process to build software to run on Nios V processor.

Ashling\* RiscFree\* Integrated Development Environment (IDE) for Intel FPGAs User Guide

Describes the RiscFree\* integrated development environment (IDE) for Intel FPGAs Arm\*-based HPS and Nios V core processor.

Nios V Processor Intel FPGA IP Release Notes

# 1.2. Intel Quartus® Prime Software Support

Nios V processor build flow is different for Intel Quartus<sup>®</sup> Prime Pro Edition software and Intel Quartus Prime Standard Edition software. Refer to *AN 980: Nios V Processor Intel Quartus Prime Software Support* for more information about the differences.

#### **Related Information**

AN 980: Nios V Processor Intel Quartus Prime Software Support

## 1.3. Nios V Processor Licensing

Each Nios V processor core has its license key. You can acquire the Nios V Processor Intel FPGA IP licenses at zero cost.

The Nios V processor license key list is available in the Intel FPGA Self-Service Licensing Center. Click the **Sign up for Evaluation or Free License** tab, and select the corresponding options to make the request.

#### Figure 1. Intel FPGA Self-Service Licensing Center

Intel® FPGA Self-Service Licensing Center

#### With the license keys, you can:

- Implement a Nios V processor within your system.

- Simulate the behavior of a Nios V processor system.

- Verify the functionality of the design, such as size and speed.

- Generate device programming files.

- Program a device and verify the design in hardware.

You do not need a license to develop software in the Ashling\* RiscFree\* IDE for Intel FPGAs.

#### **Related Information**

- Intel FPGA Self-Service Licensing Center

- For more information about obtaining the Nios V Processor Intel FPGA IP license keys.

- Intel FPGA Software Installation and Licensing

- For more information about licensing the Intel FPGA software and setting up a fixed license and network license server.

## 1.4. Embedded System Design

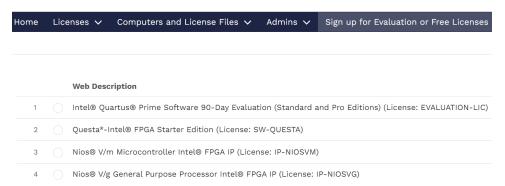

The following figure illustrates a simplified Nios V processor based system design flow, including both hardware and software development.

Figure 2. Nios V Processor System Design Flow

## 1.5. Nios V Processor Quick Start Guide

## 1.5.1. System Requirements

#### 1.5.1.1. Hardware and Software Requirements

Intel uses the following hardware and software to build a Nios V processor system:

- Supported Intel FPGA devices. For more information about the supported devices, refer to the Table: Nios V Processor Core and Device Support in AN 980: Nios V Processor Intel Quartus Prime Software Support.

- Intel Quartus Prime software

- Intel Quartus Prime Pro Edition software version 21.3 or later

- Intel Quartus Prime Standard Edition software version 22.1 or later

- Ashling RiscFree IDE for Intel FPGAs

Note: Intel recommends you to install the same software version for all software.

You need to acquire the free license for the Nios V processor to compile the design in Intel Quartus Prime software.

#### **Related Information**

- Getting Started with Nios V Processor

For more information about acquiring the license for the Nios V/m processor.

- AN 980: Nios V Processor Intel Quartus Prime Software Support

## 1.5.2. Nios V Processor Example Design

Note:

For Intel Quartus Prime Standard Edition software, refer to AN 980: Nios V Processor Intel Quartus Prime Software Support for the steps to generate the example design.

To acquire the Nios V processor example design using Intel Quartus Prime Pro Edition software, follow these steps:

- 1. Go to Intel FPGA Design Store.

- 2. Search for Arria10 NIOSV based Helloworld example design on Arria10 devkit package.

- 3. Click on the link at the title.

- 4. Accept the Software License Agreement.

- Download the package according to the Intel Quartus Prime software version of your host machine.

- 6. Double-click to run the top.par file.

- 7. top project folder is created by default after running the PAR file.

- 8. Open the top\_project and refer to the readme.txt for how-to guide.

**Table 1.** Example Design File Description

| File           | Description                                                                                                                                                               |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hw/            | Contains files necessary to run the hardware project.                                                                                                                     |

| ready_to_test/ | Contains pre-built hardware and software binaries to run the design on the target hardware. For this package, the target hardware is Intel Arria® 10 SoC development kit. |

| scripts/       | Consists of scripts to build the design.                                                                                                                                  |

| sw/            | Contains software application files.                                                                                                                                      |

| readme.txt     | Contains description and steps to apply the pre-bulit binaries or rebuild the binaries from scratch.                                                                      |

9. The Platform Designer system in the hw folder is ready for Software Design Flow.

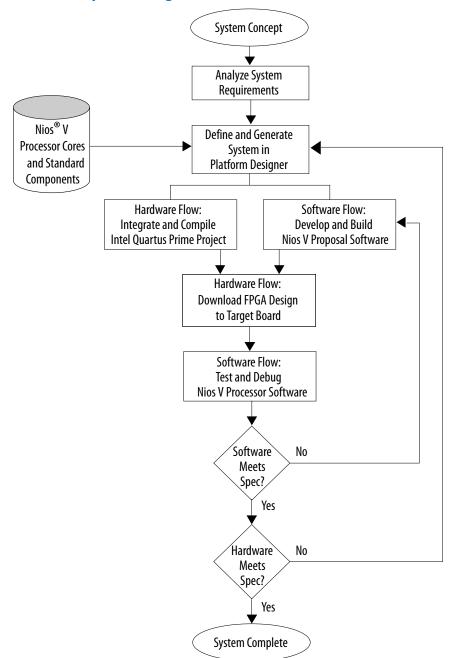

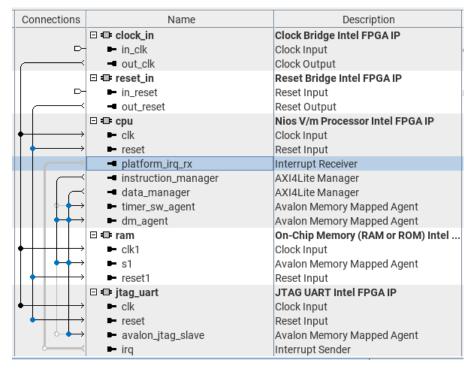

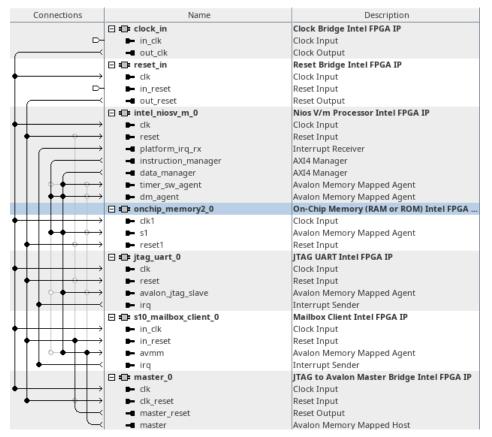

The system is built using the IP blocks described in the following table and shown in the following figure.

**Table 2.** Component Description

| Components                       | Description                                                                          |

|----------------------------------|--------------------------------------------------------------------------------------|

| Nios V/m Processor Intel FPGA IP | Runs application by executing instructions.                                          |

| JTAG UART Intel FPGA IP          | Enables serial character communication between Nios V/m processor and host computer. |

| On-Chip Memory Intel FPGA IP     | Stores data and instructions.                                                        |

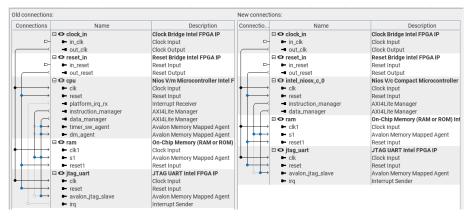

Figure 3. Nios V/m Example Design Block Diagram

Note:

For other Intel FPGA boards, you can modify the design to target your board by configuring the following settings:

- Target device setting from **Assignments** ➤ **Device...**

- Clock pin setting in the **Assignment Editor**

#### **Related Information**

- AN 980: Nios V Processor Intel Quartus Prime Software Support

- Intel FPGA Design Store

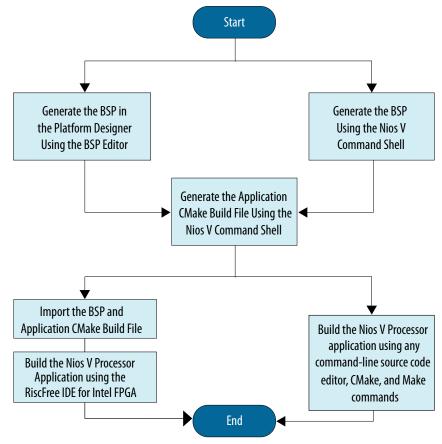

## 1.5.3. Software Design Flow

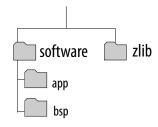

After generating the Nios V processor hardware system in Platform Designer, you need to create a Nios V processor software system. A basic software system comprises of a Board Support Package (BSP) and Application Project File (APP).

You can apply the pre-built BSP and APP projects in the sw folder. The BSP and APP projects are compatible with the Platform Designer system in the hw folder. The pre-built projects support the following operating systems:

- Intel HAL (\*\_hal)

- Micrium MicroC/OS-II (\*\_ucosii)

For custom BSP or APP projects, refer to Generating the Board Support Package and Generating the Application Project File.

#### **Related Information**

Nios V Processor Software System Design on page 32

For more information about RiscFree\* IDE for Intel FPGA and Eclipse Embedded

## 1.5.3.1. Generating the Board Support Package

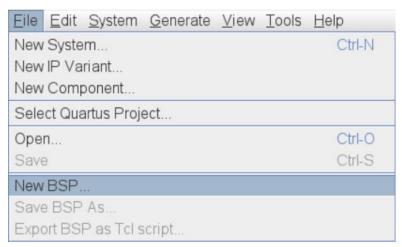

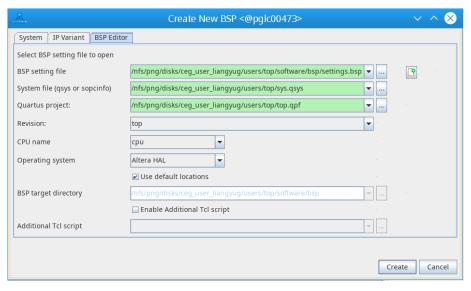

## 1.5.3.1.1. Generating the Board Support Package using the BSP Editor GUI

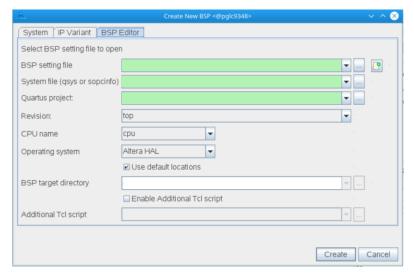

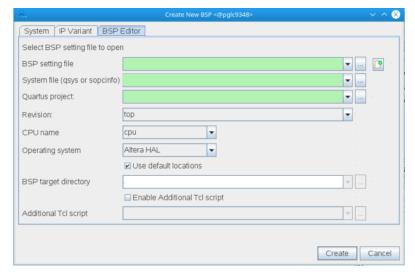

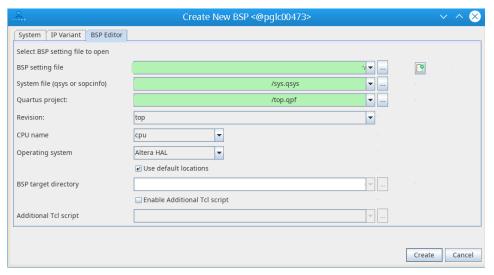

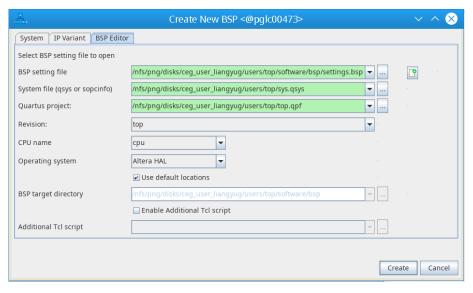

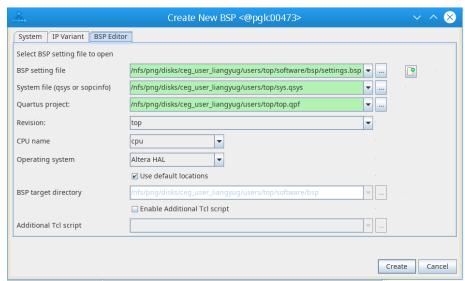

Platform Designer includes the BSP Editor board support package editing tool. A board support package (BSP) provides a software runtime environment for embedded systems, such as Nios V processor systems. The BSP Editor is a GUI tool that you can launch from Platform Designer to generate and configure BSP contents.

- 1. In the Intel Quartus Prime software, go to **Tools** ➤ **Platform Designer**.

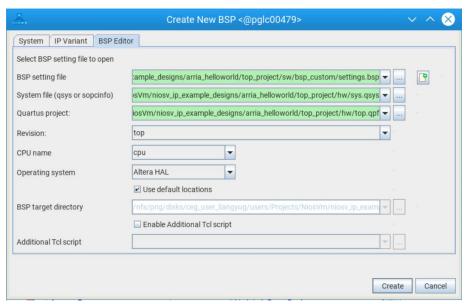

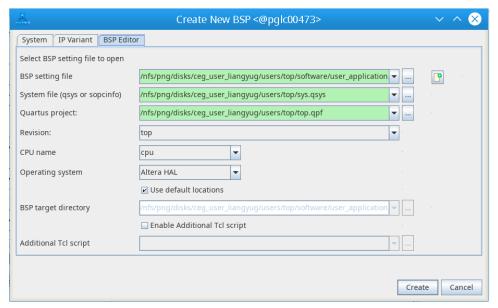

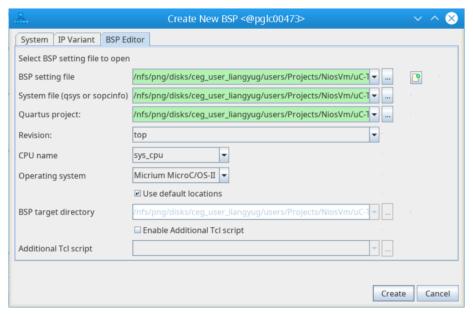

- In the Platform Designer window, go to File ➤ New BSP. The Create New BSP window appears.

- 3. For **BSP setting file**, create a BSP file (settings.bsp) in <Project directory>/sw/bsp\_custom/settings.bsp.

- 4. For **System file (qsys or sopcinfo)**, select the Nios V processor Platform Designer system (sys.qsys).

Note: For Intel Quartus Prime Standard Edition software, generate the BSP files using SOPCINFO file. Refer to AN 980: Nios V Processor Intel Quartus Prime Software Support for more information.

- 5. For **Quartus project**, select the example design Quartus Project File (top.qpf).

- 6. For **Revision**, select **top**.

- 7. For **CPU name**, select **cpu**.

- 8. Select the Operating system as Altera HAL or Micrium MicroC/OS II.

- 9. Click Create to create the BSP file.

Figure 4. Create New BSP window

10. Click **Generate BSP** to generate the BSP file.

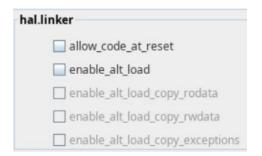

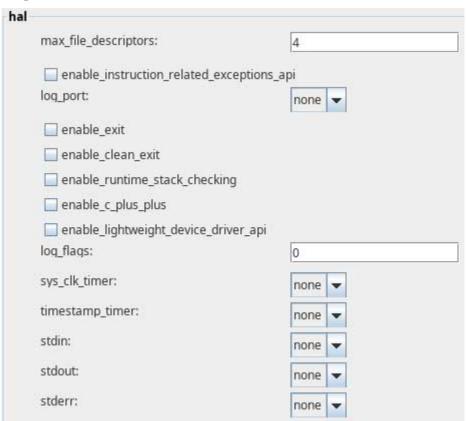

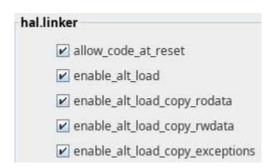

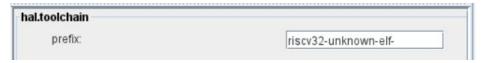

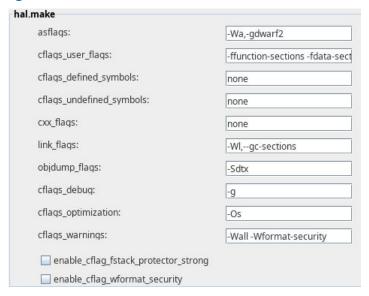

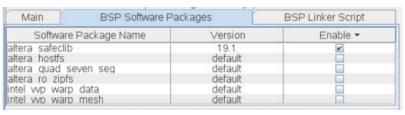

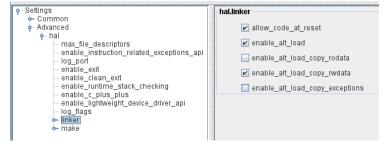

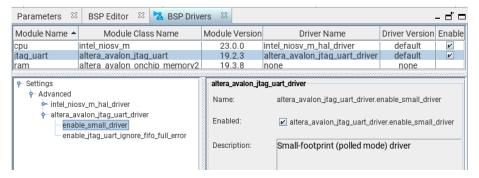

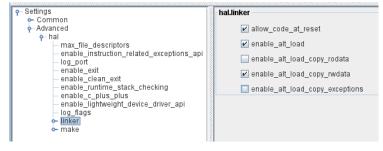

#### Figure 5. BSP Editor

Note: In the **BSP Editor**, the default selection for **sys\_clk\_timer** and **timestamp\_timer** are configured to **cpu** to use the Nios V processor's internal timer.

#### **Related Information**

- Intel Quartus Prime Pro Edition User Guide: Platform Designer

More information about Creating a Board Support Package with BSP Editor.

- Nios V Processor Software Developer Handbook: Board Support Package Editor

- AN 980: Nios V Processor Intel Quartus Prime Software Support

- Intel FPGA Design Store

#### 1.5.3.1.2. Generating the Board Support Package using the Command-Line Interface

You can also generate the BSP file using the following step:

- 1. Launch the Nios V Command Shell

- 2. Based on your Intel Quartus Prime version, execute the following CLI command to generate the BSP file. Select the **type** as **hal**, **ucosii**, or **freertos**.

In Intel Quartus Prime Pro Edition software:

```

niosv-bsp -c --quartus-project=hw/top.qpf --qsys=hw/sys.qsys \

--type=<hal, ucosii, or freertos> sw/bsp_custom/settings.bsp

```

• In Intel Quartus Prime Standard Edition software:

```

niosv-bsp -c --quartus-project=hw/top.qpf --sopcinfo=hw/sys.sopcinfo \

--type=<hal, ucosii, or freertos> sw/bsp_custom/settings.bsp

```

## 1.5.3.2. Generating the Application Project File

You can find the application source files at the following locations:

- Intel HAL application source file hello.c in the sw/app folder

- The Micrium MicroC/OS-II application source file hello\_ucosii.c in the sw/ app ucosii folder

Follow these steps to generate the application project file:

- 1. Make a new directory as <Project directory>/sw/app\_custom.

- 2. Copy the relevant application source file.

- 3. Launch the Nios V Command Shell.

- 4. Execute the command below to generate an application CMakeLists.txt.

```

niosv-app --bsp-dir=sw/bsp_custom --app-dir=sw/app_custom \

--srcs=sw/app_custom/hello.c --elf-name=hello.elf

```

#### 1.5.3.3. Building the Application Project

You can build the application project using one of the following tools:

- RiscFree IDE for Intel FPGAs

- Eclipse Embedded CDT

- Command-line interface (CLI)

```

cmake -G "Unix Makefiles" -DCMAKE_BUILD_TYPE=Debug -B \

sw/app_custom/debug -S sw/app_custom

make -C sw/app_custom/debug

```

#### **Related Information**

- RiscFree IDE for Intel FPGAs on page 35

- Eclipse CDT for Embedded C/C++ Developer on page 36

- Other Utilities Tools on page 37

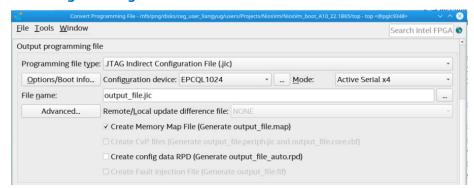

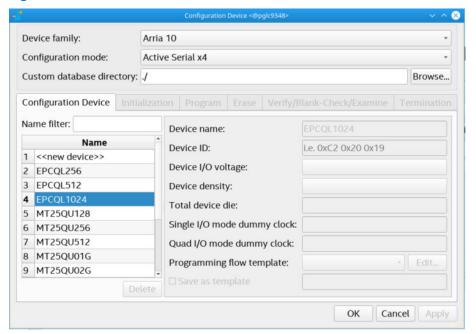

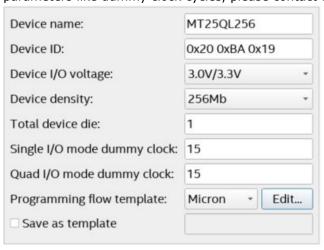

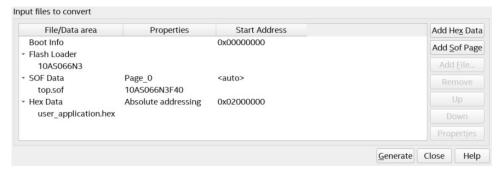

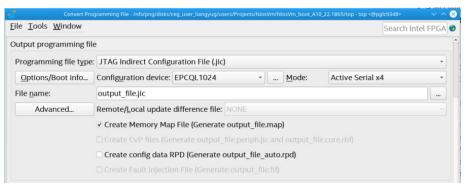

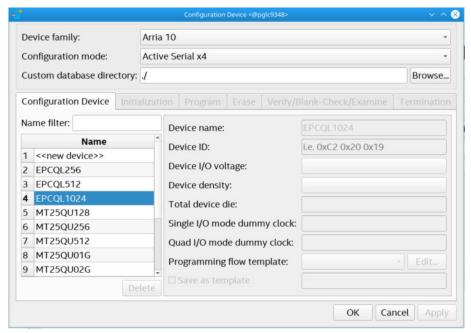

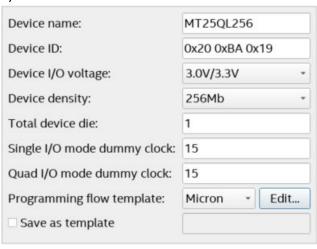

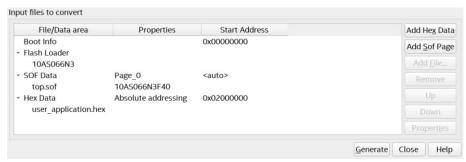

## 1.5.4. Programming Nios V into the FPGA Device

To program Nios V processor based system into the FPGA and to run your application, use Intel Quartus Programmer tool.

1. To create the Nios V processor inside the FPGA device, download the .sof file onto the board with the following command.

#### Windows:

```

quartus_pgm -c 1 -m JTAG -o p;hw/output_files/top.sof@1

Linux:

quartus_pgm -c 1 -m JTAG -o p\;hw/output_files/top.sof@1

```

Note: • -c 1 is referring to cable number connected to the Host Computer.

- @1 is referring to device index on the JTAG Chain and may differ for your board.

- 2. To run the Hello World application program, reset the Nios V processor system using the toggle\_issp.tcl script.

```

quartus_stp -t scripts/toggle_issp.tcl

```

3. Download the .elf using the niosv-download command.

```

niosv-download <elf file>

```

*Note:* Set the **Enable Debug** option during configuration in Platform Designer to use niosv-download command.

4. Use the JTAG UART terminal to print the stdout and stderr of the Nios V processor system.

```

juart-terminal

```

5. The Hello World application displays as shown in the following figures.

#### Figure 6. Output of the Hello World application using hello.c

```

juart-terminal: connected to hardware target using JTAG UART on cable juart-terminal: "USB-BlasterII on 10.219.70.15:44584 [1-4.2.3]", device 1, instance 0 juart-terminal: (Use the IDE stop button or Ctrl-C to terminate)

Hello world, this is the Nios V/m cpu checking in 0... Hello world, this is the Nios V/m cpu checking in 1... Hello world, this is the Nios V/m cpu checking in 2... Hello world, this is the Nios V/m cpu checking in 3... Hello world, this is the Nios V/m cpu checking in 4... Hello world, this is the Nios V/m cpu checking in 5... Hello world, this is the Nios V/m cpu checking in 6... Hello world, this is the Nios V/m cpu checking in 7... Hello world, this is the Nios V/m cpu checking in 7... Hello world, this is the Nios V/m cpu checking in 9... Hello world, this is the Nios V/m cpu checking in 9... Hello world, this is the Nios V/m cpu checking in 10... Hello world, this is the Nios V/m cpu checking in 11... Hello world, this is the Nios V/m cpu checking in 11...

```

## Figure 7. Output of the Hello World application using hello\_ucosii.c

```

juart-terminal: connected to hardware target using JTAG UART on cable

juart-terminal: "USB-BlasterII on sjlab-3332-1-r7.sc.intel.com:34128 [3-6.5]", device 1, instance 0

juart-terminal: (Use the IDE stop button or Ctrl-C to terminate)

Hello from main...

Task1 -- TOS: 0x27e34, BOS: 0x25e38

Task2 -- TOS: 0x29e38, BOS: 0x27e3c

Task3 -- TOS: 0x22e38, BOS: 0x27e3c

Stat -- TOS: 0x22c4c0, BOS: 0x2e5c4

Idle -- TOS: 0x2dc40, BOS: 0x2c5c4

Hello from task1: 0

Hello from task2: 0

Hello from task3: 1

Hello from task3: 1

Hello from task3: 2

Hello from task3: 1

Hello from task3: 3

```

#### **Related Information**

- Intel Quartus Prime Pro Edition User Guide: Programmer

- AN 812: Platform Designer System Design Tutorial

# 2. Nios V Processor Hardware System Design with Intel **Quartus Prime Software and Platform Designer**

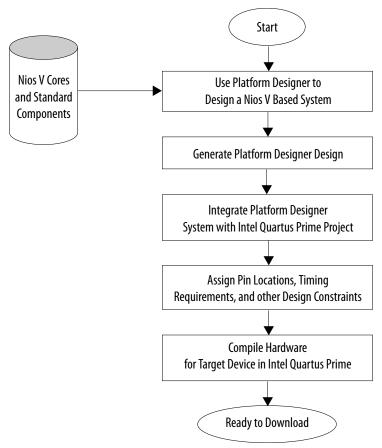

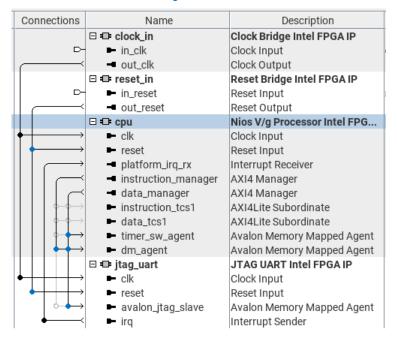

The following diagram illustrates a typical Nios V processor hardware design.

Figure 8. **Nios V Processor System Hardware Design Flow**

# 2.1. Creating Nios V Processor System Design with Platform **Designer**

The Intel Quartus Prime software includes the Platform Designer system integration tool that simplifies the task of defining and integrating Nios V processor IP core and other IPs into an Intel FPGA system design. The Platform Designer automatically creates interconnect logic from the specified high-level connectivity. The interconnect automation eliminates the time-consuming task of specifying system-level HDL connections.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

9001:2015 Registered

After analyzing the system hardware requirements, you use Intel Quartus Prime to specify the Nios V processor core, memory, and other components your system requires. The Platform Designer automatically generates the interconnect logic to integrate the components in the hardware system.

## 2.1.1. Instantiating Nios V Processor Intel FPGA IP

You can instantiate any of the processor IP cores in **Platform Designer** ➤ **IP** Catalog ➤ Processors and Peripherals ➤ Embedded Processors.

The IP core of each processor supports different configuration options based on its unique architecture. You can define these configurations to better suit your design needs.

**Table 3. Configuration Options Across Core Variants**

| Configuration Options               | Nios V/c Processor | Nios V/m Processor | Nios V/g Processor |

|-------------------------------------|--------------------|--------------------|--------------------|

| Debug                               | _                  | √                  | √                  |

| Use Reset Request                   | √                  | √                  | √                  |

| Vectors                             | √                  | √                  | √                  |

| CPU Architecture                    | _                  | √                  | √                  |

| ECC                                 | √                  | √                  | √                  |

| Caches, Peripheral Regions and TCMs | _                  | _                  | √                  |

| Custom Instructions                 | _                  | _                  | √                  |

## 2.1.1.1. Instantiating Nios V/c Compact Microcontroller Intel FPGA IP

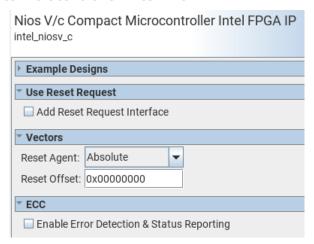

Figure 9. Nios V/c Compact Microcontroller Intel FPGA IP

## 2.1.1.1.1 Use Reset Request Tab

## **Table 4.** Use Reset Request Tab Parameter

| Use Reset Request Tab          | Description                                                                                                                                                                              |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add Reset Request<br>Interface | Enable this option to expose local reset ports where a local master can use it to trigger the Nios V processor to reset without affecting other components in a Nios V processor system. |

|                                | The reset interface consists of an input resetreg signal and an output ack signal.                                                                                                       |

|                                | You can request a reset to the Nios V processor core by asserting the resetreq signal.                                                                                                   |

|                                | The resetreq signal must remain asserted until the processor asserts ack signal. Failure for the signal to remain asserted can cause the processor to be in a non-deterministic state.   |

|                                | Assertion of the resetreq signal in debug mode has no effect on the processor's state.                                                                                                   |

|                                | The Nios V processor responds that the reset is successful by asserting the ack signal.                                                                                                  |

|                                | After the processor is successfully reset, the assertion of the ack signal can happen multiple times periodically until the de-assertion of the resetreq signal.                         |

#### 2.1.1.1.2. Vectors Tab

## **Table 5. Vectors Tab Parameters**

| Vectors      | Description                                                                                                                                                                                             |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset Agent  | The memory hosting the reset vector (the Nios V processor reset address) where the reset code resides.                                                                                                  |  |

|              | You can select any memory module connected to the Nios V processor instruction master and supported by a Nios V processor boot flow as the reset agent.                                                 |  |

| Reset Offset | <ul> <li>Specifies the offset of the reset vector relative to the chosen reset agent's base address.</li> <li>Platform Designer automatically provides a default value for the reset offset.</li> </ul> |  |

Note:

Platform Designer provides an **Absolute** option, which allows you to specify an absolute address in Reset Offset. Use this option when the memory storing the reset vector is located outside the processor system and subsystems.

#### 2.1.1.1.3. ECC Tab

## Table 6. ECC Tab

| ECC                                         | Description                                                                                                                                                                                                                                                                              |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Error Detection and Status Reporting | Enable this option to apply ECC feature for Nios V processor internal RAM blocks.     ECC feature detects error without correcting it.     — If it is a correctable error, the processor continues to operate.     — If it is an uncorrectable error, the processor halts its operation. |

## 2.1.1.2. Instantiating Nios V/m Microcontroller Intel FPGA IP

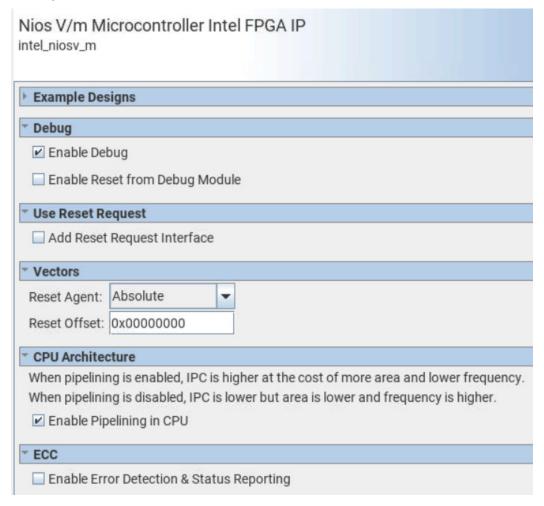

#### Figure 10. Nios V/m Microcontroller Intel FPGA IP

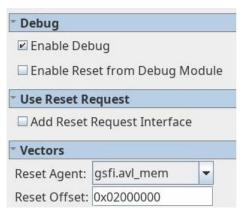

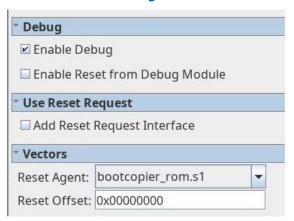

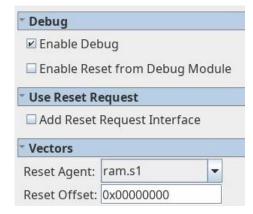

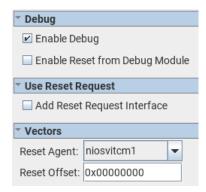

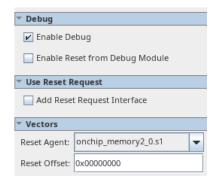

#### 2.1.1.2.1. Debug Tab

## **Table 7. Debug Tab Parameters**

| Debug Tab                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Debug                      | Enable this option to add the JTAG target connection module to the Nios V processor.     The JTAG target connection module allows connecting to the Nios V processor through the JTAG interface pins of the FPGA.     The connection provides the following basic capabilities:         Start and stop the Nios V processor         Examine and edit registers and memory.         Download the Nios V application .elf file to the processor memory at runtime via niosv-download.         Debug the application running on the Nios V processor         Connect dm_agent port to the processor instruction and data bus. Ensure the base address between both buses are the same. |

| Enable Reset from Debug<br>Module | <ul> <li>Enable this option to expose dbg_reset_out and ndm_reset_in ports.</li> <li>JTAG debugger or niosv-download -r command trigger the dbg_reset_out, which allows the Nios V processor to reset system peripherals connecting to this port.</li> <li>You must connect the dbg_reset_out interface to ndm_reset_in instead of reset interface to trigger reset to processor core and timer module.</li> </ul>                                                                                                                                                                                                                                                                  |

## 2.1.1.2.2. Use Reset Request Tab

## **Table 8.** Use Reset Request Tab Parameter

| Use Reset Request Tab          | Description                                                                                                                                                                              |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add Reset Request<br>Interface | Enable this option to expose local reset ports where a local master can use it to trigger the Nios V processor to reset without affecting other components in a Nios V processor system. |

|                                | The reset interface consists of an input resetreg signal and an output ack signal.                                                                                                       |

|                                | You can request a reset to the Nios V processor core by asserting the resetreq signal.                                                                                                   |

|                                | The resetreq signal must remain asserted until the processor asserts ack signal. Failure for the signal to remain asserted can cause the processor to be in a non-deterministic state.   |

|                                | Assertion of the resetreg signal in debug mode has no effect on the processor's state.                                                                                                   |

|                                | The Nios V processor responds that the reset is successful by asserting the ack signal.                                                                                                  |

|                                | After the processor is successfully reset, the assertion of the ack signal can happen multiple times periodically until the de-assertion of the resetreq signal.                         |

## 2.1.1.2.3. Vectors Tab

#### **Table 9. Vectors Tab Parameters**

| Vectors      | Description                                                                                                                                                                                             |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset Agent  | The memory hosting the reset vector (the Nios V processor reset address) where the reset code resides.                                                                                                  |  |

|              | You can select any memory module connected to the Nios V processor instruction master<br>and supported by a Nios V processor boot flow as the reset agent.                                              |  |

| Reset Offset | <ul> <li>Specifies the offset of the reset vector relative to the chosen reset agent's base address.</li> <li>Platform Designer automatically provides a default value for the reset offset.</li> </ul> |  |

Note:

Platform Designer provides an **Absolute** option, which allows you to specify an absolute address in Reset Offset. Use this option when the memory storing the reset vector is located outside the processor system and subsystems.

#### 2.1.1.2.4. CPU Architecture

#### **Table 10.** CPU Architecture Tab Parameters

| CPU Architecture         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Enable Pipelining in CPU | <ul> <li>Enable this option to instantiate pipelined Nios V/m processor.         <ul> <li>IPC is higher at the cost of higher logic area and lower Fmax frequency.</li> </ul> </li> <li>Disable this option to instantiate non-pipelined Nios V/m processor.         <ul> <li>Has similar core performance with the Nios V/c processor.</li> <li>Supports debugging and interrupt capability</li> <li>Lower logic area and higher Fmax frequency at the cost of lower IPC.</li> </ul> </li> </ul> |  |

#### 2.1.1.2.5. ECC Tab

#### Table 11. ECC Tab

| ECC                                         | Description                                                                                                                                                        |  |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Enable Error Detection and Status Reporting | <ul> <li>Enable this option to apply ECC feature for Nios V processor internal RAM blocks.</li> <li>ECC feature detects error without correcting it.</li> </ul>    |  |

|                                             | <ul> <li>If it is a correctable error, the processor continues to operate.</li> <li>If it is an uncorrectable error, the processor halts its operation.</li> </ul> |  |

## 2.1.1.3. Instantiating Nios V/g General Purpose Processor Intel FPGA IP

## Figure 11. Nios V/g General Purpose Processor Intel FPGA IP

Nios V/g General Purpose Processor Intel FPGA IP intel\_niosv\_g

Example Designs

CPU Architecture

Debug

Use Reset Request

Vectors

Memory Configurations

Caches

Peripheral Regions

Tightly Coupled Memories

ECC

Custom Instructions

#### 2.1.1.3.1. Debug Tab

## **Table 12.** Debug Tab Parameters

| Debug Tab                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Enable Debug                      | Enable this option to add the JTAG target connection module to the Nios V processor.     The JTAG target connection module allows connecting to the Nios V processor through the JTAG interface pins of the FPGA.     The connection provides the following basic capabilities:         Start and stop the Nios V processor         Examine and edit registers and memory.         Download the Nios V application .elf file to the processor memory at runtime via niosv-download.         Debug the application running on the Nios V processor         Connect dm_agent port to the processor instruction and data bus. Ensure the base address between both buses are the same. |

| Enable Reset from Debug<br>Module | <ul> <li>Enable this option to expose dbg_reset_out and ndm_reset_in ports.</li> <li>JTAG debugger or niosv-download -r command trigger the dbg_reset_out, which allows the Nios V processor to reset system peripherals connecting to this port.</li> <li>You must connect the dbg_reset_out interface to ndm_reset_in instead of reset interface to trigger reset to processor core and timer module.</li> </ul>                                                                                                                                                                                                                                                                  |

## 2.1.1.3.2. Use Reset Request Tab

## **Table 13.** Use Reset Request Tab Parameter

| Use Reset Request Tab          | Description                                                                                                                                                                              |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Add Reset Request<br>Interface | Enable this option to expose local reset ports where a local master can use it to trigger the Nios V processor to reset without affecting other components in a Nios V processor system. |  |

|                                | The reset interface consists of an input resetreg signal and an output ack signal.                                                                                                       |  |

|                                | You can request a reset to the Nios V processor core by asserting the resetreq signal.                                                                                                   |  |

|                                | The resetreq signal must remain asserted until the processor asserts ack signal. Failure for the signal to remain asserted can cause the processor to be in a non-deterministic state.   |  |

|                                | Assertion of the resetreq signal in debug mode has no effect on the processor's state.                                                                                                   |  |

|                                | The Nios V processor responds that the reset is successful by asserting the ack signal.                                                                                                  |  |

|                                | After the processor is successfully reset, the assertion of the ack signal can happen multiple times periodically until the de-assertion of the resetreq signal.                         |  |

## 2.1.1.3.3. Vectors Tab

#### **Table 14.** Vectors **Tab Parameters**

| Vectors      | Description                                                                                                                                                                                             |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reset Agent  | The memory hosting the reset vector (the Nios V processor reset address) where the recode resides.                                                                                                      |  |

|              | You can select any memory module connected to the Nios V processor instruction master<br>and supported by a Nios V processor boot flow as the reset agent.                                              |  |

| Reset Offset | <ul> <li>Specifies the offset of the reset vector relative to the chosen reset agent's base address.</li> <li>Platform Designer automatically provides a default value for the reset offset.</li> </ul> |  |

Note:

Platform Designer provides an **Absolute** option, which allows you to specify an absolute address in Reset Offset. Use this option when the memory storing the reset vector is located outside the processor system and subsystems.

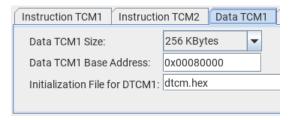

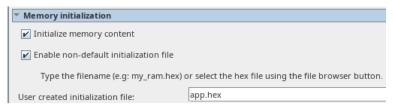

## 2.1.1.3.4. Memory Configurations Tab

## **Table 15.** Memory Configuration Tab Parameters

| Category                    | Memory<br>Configuration Tab | Description                                                                                                                                                                                                                                                              |

|-----------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

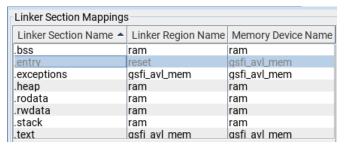

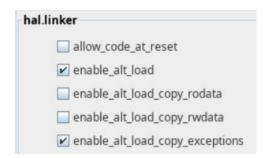

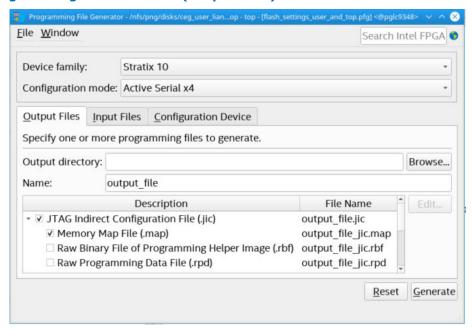

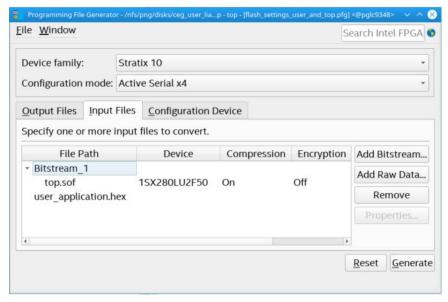

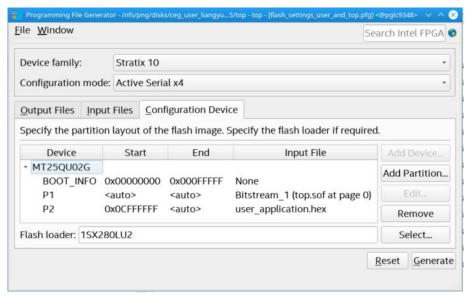

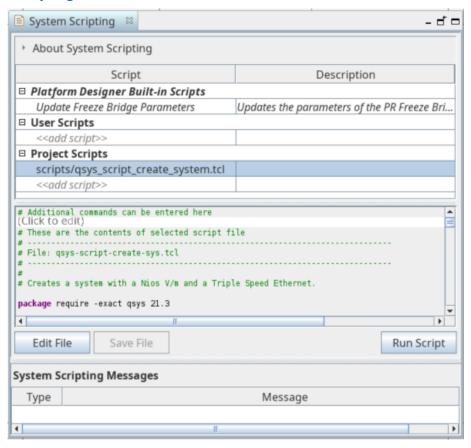

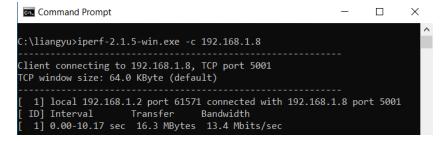

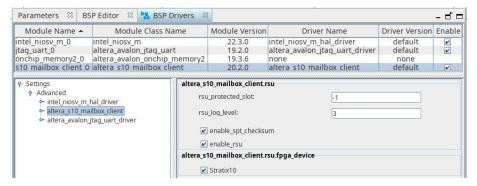

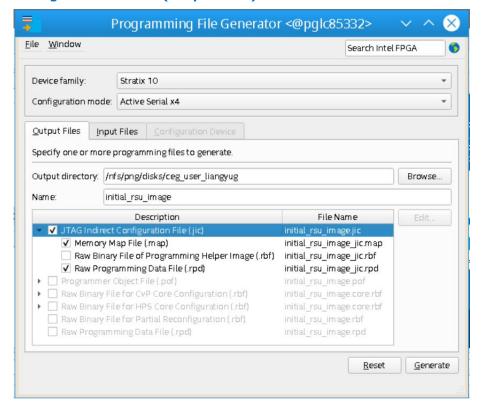

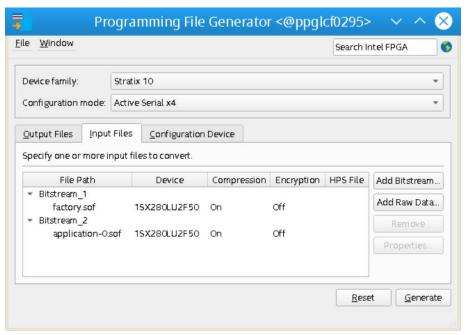

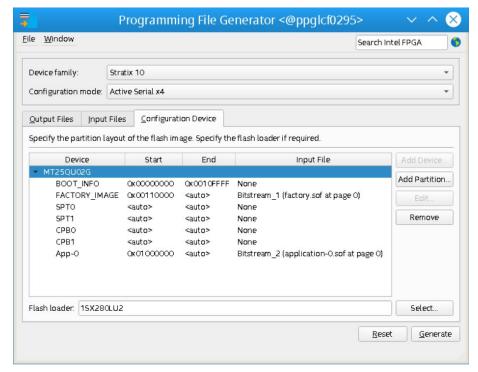

| Caches                      | Data Cache Size             | <ul><li>Specifies the size of the data cache.</li><li>Valid sizes are from 1 kilobytes (KB) to 16 KB.</li></ul>                                                                                                                                                          |